Fターム[5F058BA20]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成の目的、効果 (3,596) | その他 (1,569)

Fターム[5F058BA20]に分類される特許

161 - 180 / 1,569

炭化珪素半導体装置の製造方法

【課題】炭化珪素MOSFETにおいて、炭化珪素層とゲート絶縁膜との界面に発生する界面準位を十分に低減できず、キャリアの移動度が低下する場合があった。

【解決手段】この発明に係る炭化珪素半導体装置は、炭化珪素層を有し炭化珪素層上にゲート絶縁膜を形成した基板を炉の中に導入する基板導入工程と、基板を導入した炉を加熱して一酸化窒素と窒素とを導入する加熱工程とを備え、加熱工程は、窒素を反応させてゲート絶縁膜と炭化珪素層との界面を窒化する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアに位置ずれが生じても、ビアがエアギャップにつながることを抑制できるようにする。

【解決手段】複数の配線240は例えばCu配線であり、互いに平行に延伸している。側壁絶縁膜212は、複数の配線240それぞれの側壁に形成されている。エアギャップは、複数の配線240それぞれの相互間に形成され、複数の側壁絶縁膜212の間に位置している。絶縁膜302は、複数の配線240上、複数の側壁絶縁膜212上、およびエアギャップ214上に形成されている。ビア344は絶縁膜302を貫通しており、いずれかの配線240に接続している。そして側壁絶縁膜212は、絶縁膜302がエッチングされる条件では絶縁膜302よりエッチングレートが低い材料により形成されている。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いるトランジスタにおいては、酸化物半導体内に水素が存在することでトランジスタの電気特性不良に繋がる。そこで、良好な電気特性を有する半導体装置を提供する。

【解決手段】チャネル領域が形成される酸化物半導体層と接する絶縁層をハロゲン化珪素を用いたプラズマCVD法により形成する。このようにして形成された絶縁層の水素濃度は6×1020atoms/cm3未満であり、且つハロゲンの濃度は1×1020atoms/cm3以上であるので、酸化物半導体層に水素が拡散することを防ぐことができ、ハロゲンにより酸化物半導体層内に存在する水素を不活性化させ、または脱離させ、良好な電気特性を有する半導体装置を提供することできる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】金属酸化膜または金属シリケート膜を含む薄膜ゲート絶縁膜を有する半導体装置の製造方法において、VFBを十分に制御し、Vthを十分に制御すること。

【解決手段】基板1上に、第1の金属の酸化膜、または、第1の金属のシリケート膜からなる第1高誘電率ゲート絶縁膜5を形成する第1工程と、第1高誘電率ゲート絶縁膜5上に、第2の金属の酸化膜からなる第2高誘電率ゲート絶縁膜6を形成する第2工程と、第2高誘電率ゲート絶縁膜6上に、ゲート電極膜7を形成する第3工程と、を有し、前記第2工程では、第2の金属元素および炭化水素基からなる主原料と、溶媒材料と、を混合した混合材料を用いて、原子層蒸着法により第2高誘電率ゲート絶縁膜6を形成する半導体装置の製造方法を提供する。

(もっと読む)

成膜方法及び成膜装置

【課題】比較的低温で成膜しても含有する炭素濃度を多くさせてクリーニング時のエッチングレートを比較的小さくでき、もってクリーニング時の膜厚の制御性を向上させることができる成膜方法を提供する。

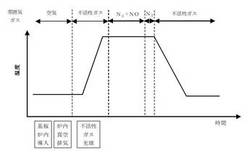

【解決手段】被処理体Wが収容されて真空引き可能になされた処理容器4内に、シラン系ガスと窒化ガスと炭化水素ガスとを供給して前記被処理体の表面にSiCN膜よりなる薄膜を形成する成膜方法において、前記シラン系ガスと前記窒化ガスと前記炭化水素ガスとをそれぞれ一定の供給期間でパルス状に供給する供給工程と供給を停止する停止工程とよりなる1サイクルを複数回繰り返し実行してプラズマを用いることなく前記薄膜を形成する。これにより、比較的低温で成膜しても含有する炭素濃度を多くさせてクリーニング時のエッチングレートを比較的小さくでき、もってクリーニング時の膜厚の制御性を向上させる。

(もっと読む)

半導体デバイスの製造方法

【課題】第1ガスの使用効率を向上させる。

【解決手段】処理室に連通する第1ノズルから、処理室内の排気速度を低下させた状態で処理室内に第1ガスを供給する工程と、第1ガスの供給を止めた後、第1ノズル内に不活性ガスを供給する工程と、処理室内に残留する第1ガスを除去する工程と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線間の実効的な容量の増加を抑制する。

【解決手段】半導体装置100は、6員環構造の環状シロキサンを原料とする絶縁膜11と、絶縁膜11に形成された配線溝12と、配線溝12に金属膜(配線メタル)15が埋め込まれて構成される配線10と、を有する。半導体装置100では、配線溝12の底面において、絶縁膜11の内部よりも単位体積あたりの炭素原子数、又は/及び、窒素原子数が多い改質層13が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

塗布装置および塗布方法

【課題】 シートフィルム上に薄膜を形成する塗布装置および塗布方法において、吸着による塗布膜厚ムラを防止するのに適した技術を提供する。

【解決手段】 シートフィルムFの一面の周縁を吸引して吸着する真空チャックにて基材を保持するステージ340と、ステージ340保持されたシートフィルムFの表面に薄膜材料を塗布する塗布ノズル343と、塗布された薄膜材料をシートフィルムFの表面に広げるためにステージ340を回転する回転機構とを具備する塗布ユニット34において、塗布手ノズル343より薄膜材料が塗布される前にシートフィルムFを保持した状態でステージ340を回転することでステージ340の中央部341aとシートフィルムFとの間に残留する空気を排気した状態で吸着状態を達成する。

(もっと読む)

成膜方法及び薄膜トランジスタの作製方法

【課題】3層以上の膜を成膜するに際して、第1の膜の成分が第3の膜に含まれることを防ぐ成膜方法を提供する。

【解決手段】上部電極104と下部電極102が設けられた成膜装置100により3層以上の膜を成膜する多層膜の成膜に際して、下部電極102上に基板110を配して第1の膜112を成膜し、前記第1の膜112の形成時よりも上部電極104と前記基板110の間の距離を長くし、前記第1の膜112上に第2の膜114を成膜し、前記第2の膜114の形成時よりも前記上部電極104と前記基板110の間の前記距離を短くし、前記第2の膜114上に第3の膜116を成膜する。

(もっと読む)

半導体装置の製造方法

【課題】従来よりも低温でシリコン含有窒化膜を成膜することができる半導体装置の製造方法を提供する。

【解決手段】ウエハにSiN膜を形成する半導体装置の製造方法であって、ウエハが収容される処理室に、DCS(ジクロロシラン)を供給するシラン系ガス供給工程と、前記シラン系ガスの供給と同時ではないタイミングで、前記処理室にNH3(アンモニア)を供給する窒化ガス供給工程と、前記処理室にTEA(トリエチルアミン)を供給するアミン系ガス供給工程と、前記処理室の前記シラン系ガスまたは前記窒化ガスを排気する排気工程と、を有し、前記アミン系ガス供給工程は、前記シラン系ガス供給工程及び前記窒化ガス供給工程と合わせて行う。

(もっと読む)

シリコン酸化膜からのOH基除去法

【課題】OH基を含有するシリコン酸化膜から、TFTの性能である界面特性や絶縁性のため、及び基板を安価なものにするため低温で作製するため、低温で簡便な方法でOH基を減少させる方法を提供する。

【解決手段】基板上に低温形成された、OH基を含有するシリコン酸化膜を有機溶媒に接触・浸漬させる工程と、その後、前記シリコン酸化膜を低温加熱する熱アニール処理を加える工程と、を有することを特徴とするシリコン酸化膜からのOH基除去法。

(もっと読む)

半導体装置及びその製造方法

【課題】Cdsubの低減を通じて、出力容量Cossの低減に寄与する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板と半導体基板上に絶縁膜を介して形成された第1導電型の半導体層とを有するSOI基板と、第1導電型の半導体層からなる活性領域内に、第2導電型の半導体層からなるウェルを形成するとともに、ウェル内および第1導電型の活性領域内に、第1導電型の半導体層からなるソース・ドレイン領域を形成した横型MOSFETにおいて、活性領域のうち、ドレイン領域にコンタクトするように形成されるドレインパッド形成領域9p下の少なくとも一部は、SOI基板の絶縁膜に到達するように形成された絶縁性領域11で構成される。

(もっと読む)

誘電体膜の材料特性を高めるための活性化学的方法

【課題】ケイ素含有誘電体材料の層の誘電率の修復

【解決手段】第1の誘電率および少なくとも1つの表面を有するケイ素含有誘電体材料の層の誘電率の修復方法であって、ケイ素含有誘電体材料の層の第1の誘電率が第2の誘電率まで増加しており、該方法は、ケイ素含有誘電体材料の層の少なくとも1つの表面と、ケイ素含有流体とを接触させるステップ、そしてケイ素含有誘電体材料の層の少なくとも1つの表面を、紫外線照射、熱、および電子ビームからなる群から選択されるエネルギー源に曝すステップ、の各ステップを含み、ケイ素含有誘電体材料の層は、ケイ素含有誘電体材料の層をエネルギー源に曝した後の第2の誘電率より低い第3の誘電率を有する、方法。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する酸化物半導体層に接する絶縁層に、シリコン過酸化ラジカルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

微細空間への絶縁物充填方法

【課題】半導体基板に設けられた微細空間内に、充填不全などを回避して、絶縁物を確実に充填しえる方法を提供すること。

【解決手段】 半導体基板2に設けられた微細空間21内に絶縁物を充填するにあたり、微細空間21の開口する半導体基板2の一面側から、微細空間21内に流動性絶縁物4を充填する。そして、流動性絶縁物4を、加圧したままで、硬化させる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する脱水化または脱水素化された酸化物半導体層に接する絶縁層に、シリコン過酸化ラジカルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

成膜方法及び処理システム

【課題】比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成することが可能な成膜方法を提供する。

【解決手段】絶縁層1が表面に形成された被処理体Wに対して成膜処理を施す成膜方法において、第1の金属よりなる第1の薄膜60を形成する第1の薄膜形成工程と、前記第1の薄膜を酸化して酸化膜60Aを形成する酸化工程と、前記酸化膜上に第2の金属を含む第2の薄膜62を形成する第2の薄膜形成工程とを有する。これにより、比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成する。

(もっと読む)

シリコンオキシナイトライド膜の形成方法およびそれにより製造されたシリコンオキシナイトライド膜付き基板

【課題】エネルギーコストを抑制できるシリコンオキシナイトライド膜の製造方法とそれにより製造されたシリコンオキシナイトライド膜付き基板の提供。

【解決手段】基板表面にポリシラザン化合物を含む被膜形成用組成物を塗布して塗膜を形成させ、前記塗膜に含まれる過剰の溶媒を除去し、溶媒除去後の塗膜を150℃未満の温度条件下で紫外線を照射することを含むシリコンオキシナイトライド膜の形成方法。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。信頼性の高い半導体装置を歩留まり良く作製する。

【解決手段】酸化物半導体膜を有するトップゲート構造のスタガ型トランジスタにおいて、酸化物半導体膜と接する第1のゲート絶縁膜を、プラズマCVD法によりフッ化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成し、該第1のゲート絶縁膜上に積層する第2のゲート絶縁膜を、プラズマCVD法により水素化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成する。

(もっと読む)

161 - 180 / 1,569

[ Back to top ]