Fターム[5F082AA08]の内容

Fターム[5F082AA08]に分類される特許

21 - 40 / 142

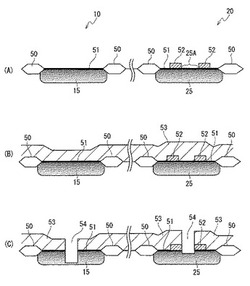

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、印加電圧により抵抗値にバラツ

キが生じない半導体装置を提供することを目的とする。

【解決手段】半導体基板(2)上にバイポーラ素子とともに抵抗素子を形成さ

れる半導体装置(100)において、抵抗素子は、半導体基板(2)上に形成さ

れ、半導体基板(2)を絶縁する絶縁層(101)と、絶縁層(101)上に形

成され、抵抗を形成する抵抗層(102)とを設ける。

(もっと読む)

高周波増幅器

【課題】回路面積を増加させることなく、動作状態のトランジスタからの発熱を抑制することによって、小型化及び低コスト化を図ることができる高周波増幅器を提供する。

【解決手段】複数の単位トランジスタ3が並列に接続されたトランジスタ列からなり、高周波を増幅する増幅素子と、トランジスタ列の隣り合った単位トランジスタ3のフィンガ間にそれぞれ形成された出力整合回路の回路素子2とを備える。

(もっと読む)

半導体装置、半導体基板、及び半導体基板の処理方法

【課題】表面が(111)面以外であるシリコン層と、表面が(0001)面である窒化物半導体層とを基板に設け、かつシリコンと窒化物半導体の線膨張係数の違いに起因した応力を小さくする。

【解決手段】まずSOI(Silicon On Insulator)基板を準備する。SOI基板は、表面が(111)面であるシリコン基板100上に絶縁層120及びシリコン層200を積層した基板である。シリコン層200は、表面が(111)面以外の面方位である。次いで、絶縁層120及びシリコン層200に、底面にシリコン基板100が露出している開口部201を形成する。次いで、開口部201内にIII族の窒化物半導体層300を形成する。

(もっと読む)

バイポーラ・トランジスタ及びその製造方法

【課題】 バイポーラ・トランジスタ構造体、バイポーラ・トランジスタを設計し製造する方法、及びバイポーラ・トランジスタを有する回路を設計する方法を提供する。

【解決手段】 バイポーラ・トランジスタを設計する方法は、バイポーラ・トランジスタの初期設計を選択するステップ(図25の240)と、バイポーラ・トランジスタの初期設計をスケーリングしてバイポーラ・トランジスタの縮小設計を生成するステップ(245)と、バイポーラ・トランジスタの縮小設計の応力補償が必要かどうかを、スケーリング後のバイポーラ・トランジスタのエミッタの寸法に基づいて判断するステップ(250)と、バイポーラ・トランジスタの縮小設計の応力補償が必要な場合に、縮小設計のトレンチ分離レイアウト・レベルのレイアウトを、縮小設計のエミッタ・レイアウト・レベルのレイアウトに対して調節して(255)バイポーラ・トランジスタの応力補償縮小設計を生成するステップ(260)と、を含む。

(もっと読む)

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】同一基板に形成されるHBTとFETとの相互影響を低減する。

【解決手段】第1半導体と、第1半導体の上方に形成された第2半導体とを備え、第2半導体は、P型の伝導型を示す不純物またはN型の伝導型を示す第1不純物原子と、第2半導体が第1不純物原子を有する場合のフェルミ準位を、第2半導体が第1不純物原子を有しない場合のフェルミ準位に近づける第2不純物原子とを有する半導体基板を提供する。一例として、当該第2半導体の多数キャリアは電子であり、第2不純物原子は、第1不純物原子を有する第2半導体のフェルミ準位を下降させる。第2半導体は3−5族化合物半導体であり、第2不純物原子が、ベリリウム、ボロン、炭素、マグネシウム、および亜鉛からなる群から選択された少なくとも1つであってもよい。

(もっと読む)

増幅素子

【課題】ECMのインピーダンス変換および増幅に、J−FETを入力としバイポーラトランジスタを出力とする増幅素子に、バックゲート構造のJ−FETを用いると、バックゲート−半導体基板間の容量が、増幅素子の入出力間の寄生容量(ミラー容量)となり、増幅素子の入力ロスが増大する問題に対し有効な半導体装置を提供する。

【解決手段】接地されたp型半導体基板11にp型半導体層12を積層し、p型半導体層12にn型チャネル領域22を有するJ−FETと、n型コレクタ領域33bを有するバイポーラトランジスタを設けた増幅素子とする。これにより、増幅素子の入出力間の寄生容量が発生しなくなるため、ミラー容量による入力ロスの増大を防止できる。また、J−FETのチャネル領域は、エミツタ拡散31と同時に形成できるため、IDSSSや、ピンチオフ電圧が安定し、増幅素子としての消費電流のばらつきが低減し、生産性が向上する。

(もっと読む)

制御可能なサージ電流耐性を有するパワースイッチング素子

半導体スイッチング素子は、ワイドバンドギャップパワートランジスタと、前記パワートランジスタと並列に接続されたワイドバンドギャップサージ電流トランジスタと、前記サージ電流トランジスタを駆動するように構成された駆動トランジスタを含む。前記半導体スイッチング素子の、オン状態での出力電流のほぼすべては、前記パワートランジスタのドレイン−ソース電圧が第一の電圧範囲内にあるときには、前記パワートランジスタのチャネルを通って流れる。当該第一の電圧範囲は、例えば、通常動作中に期待されるドレイン−ソース電圧に対応し得る。その一方で、前記半導体スイッチング素子は、さらに、オン状態で、前記パワートランジスタのドレイン−ソース電圧が第二の(より高い)電圧範囲内にあるときには、出力電流が、前記サージ電流トランジスタ、および前記パワートランジスタのチャネルの両方を通って流れるように構成される。 (もっと読む)

半導体装置及びその製造方法

【課題】高周波帯域で動作する半導体装置の特性の低下を抑制しつつ、製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、電界効果型トランジスタと、ヘテロ接合バイポーラトランジスタと、ヘテロ接合バイポーラトランジスタのGaAsベース層7を用いて形成されたベースエピ抵抗素子28と、電界効果型トランジスタのInGaAsチャネル層4を用いて形成された配線部26と、配線部26とベースエピ抵抗素子28とを絶縁する高抵抗化領域27と、配線部26の水平方向の周囲を囲う絶縁性の素子分離領域24とを含む。また、ベースエピ抵抗素子28は、半絶縁性GaAs基板1の主面に垂直な方向から見て、配線部26と交差しているベースエピ抵抗素子領域29を有する。

(もっと読む)

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】単一半導体基板上にHBTおよびFETのような異なる種類の複数デバイスを形成するに適した化合物半導体基板を提供する。

【解決手段】第1半導体110と、第1半導体上に形成された、電子捕獲中心または正孔捕獲中心を有するキャリアトラップ層130と、キャリアトラップ層上にエピタキシャル成長され、自由電子または自由正孔が移動するチャネルとして機能する第2半導体144と、第2半導体上にエピタキシャル成長したN型半導体/P型半導体/N型半導体で表される積層体、または前記第2半導体上にエピタキシャル成長したP型半導体/N型半導体/P型半導体で表される積層体を含む第3半導体160とを備える半導体基板。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体デバイス、半導体基板に分離されたポケットを形成する方法、半導体構成、PNPトランジスタ、横型NチャネルDMOSトランジスタ、横型トレンチDMOSトランジスタ

【課題】モジュール化された、相互作用しないやり方で、単一の半導体ウェハにともに接近して実装され、十分に分離された、最適化されたトランジスタまたは他のデバイスの任意の集合の作製を可能にする。

【解決手段】

一群の半導体デバイスが、エピタキシャル層を含まない基板に形成される。一実施例では、この一群は、5VのCMOSペア、12VのCMOSペア、5VのNPN、5VのPNP、いくつかの形状の横型トレンチMOSFET、および30V横型N−チャネルDMOSを含む。これらのデバイスの各々は、横方向かつ縦方向の双方において極めて小型であり、基板の他のすべてのデバイスから十分に分離され得る。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】バイポーラトランジスタの高速化に伴うMOSトランジスタの分離特性の低下を抑制する半導体装置を提供する。

【解決手段】半導体装置1000aは、第一導電型のバイポーラトランジスタ100及びMOSトランジスタ200を備え、MOSトランジスタ200は、第二導電型の半導体基板1と半導体基板1上に形成された第一導電型のエピタキシャル層2との界面付近に形成された、半導体基板1上面から第一の深さに不純物濃度のピークを持つ第一導電型埋込層16と、第一導電型埋込層16上に形成された第二導電型埋込層17及びウェル層18と、第二導電型ウェル層18に形成された第一導電型のソース層19及びドレイン層20と、第一の深さより浅い第二の深さに不純物濃度のピークを持つ第一導電型埋込層27とを有し、第一導電型埋込層27は、第一導電型埋込層16と接し、かつ、第二導電型埋込層17の外縁部を囲むように形成されている。

(もっと読む)

非単結晶半導体間隔部分がベース・リンク長を制御するバイポーラ接合トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体構成体がバイポーラトランジスタ(101)及び間隔構成体(265−1又は265−2)を包含している。

【解決手段】 該トランジスタはエミッタ(241)、ベース(243)、コレクタ(245)を有している。該ベースはベースコンタクト部分(243−1)、該エミッタの下側で且つ該コレクタの物質上方に位置されているイントリンシックベース部分(243I−1)、該イントリンシックベース部分とベースコンタクト部分との間に延在しているベースリンク部分(243L−1)を包含している。該間隔構成体は、間隔コンポーネント及び上部半導体表面に沿って延在する分離用誘電体層(267−1又は267−2)を包含している。該間隔コンポーネントは、該ベースリンク部分の上方で該誘電体層上に位置されており、好適には多結晶半導体物質であるほぼ非単結晶の半導体物質の横方向間隔部分(269−1又は269−2)を包含している。該横方向間隔部分の両側の第1及び第2下部端部(305−1及び307−1)は該ベースリンク部分の両側の第1及び第2上部端部(297−1及び299−1)に対して横方向に適合し、その長さを決定し且つそれにより制御する。

(もっと読む)

半導体装置

【課題】統合型のインテリジェントスイッチデバイス、統合型の入力信号・伝達ICまたは統合型のパワーICなどに用いられる横型MOSFETにおいて、複雑な分離構造を用いずに、より小さいチップ面積で高ESD耐量および高サージ耐量を具えた半導体装置を提供する。

【解決手段】P型半導体よりなるエミッタ領域25、ベース領域として機能するNウェル領域10およびP型エピタキシャル成長層13およびP型半導体基板12をコレクタとするベースオープンの縦型バイポーラトランジスタの表面電極26と、横型MOSFETのドレイン電極22とを金属電極配線27により電気的に接続し、高ESD電圧や高サージ電圧が印加されたときに、ベースオープンの縦型バイポーラトランジスタの動作によりESDおよびサージエネルギーを吸収するとともに、破壊に至る横型MOSFETの降伏耐圧以下の電圧に制限する。

(もっと読む)

半導体装置

【課題】高耐圧化及び高温動作を実現できる、HBTとFETを備える半導体装置を提供する。

【解決手段】本発明に係る半導体装置100は、基板101の上に順時積層されたn+型GaN層103及びn型GaN層104と、p型InGaN層105と、アンドープGaN層106及びn型AlGaN層107と、HBT領域121のn+型GaN層103と電気的に接続されたコレクタ電極114と、HBT領域121のp型InGaN層105と電気的に接続されたベース電極113と、HBT領域121のn型AlGaN層107と電気的に接続されたエミッタ電極112と、HFET領域120のn型AlGaN層107と電気的に接続されたソース電極109及びドレイン電極111と、n型AlGaN層107の上に形成されたゲート電極110とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

BiCDMOS構造及びその製造方法

【課題】DMOS電力回路、CMOSデジタル論理回路、及びコンプリメンタリバイポーラアナログ回路の全てを単一の集積化された回路チップ上に実現するBiCDMOS構造及びその製造方法を提供する。

【解決手段】基層10内に下向きに延出し、且つ基層の上に配置されたエピタキシャル層40内に上向きに延出し、かつエピタキシャル層の上側主面の下に配置された埋め込み絶縁領域21Bと、エピタキシャル層内のみに配置され、かつ埋め込み絶縁領域の上側主面から上向きに延出した埋め込みウェル領域44Bと、エピタキシャル層内に配置され、かつエピタキシャル層の上側主面からエピタキシャル層内に下向きに延出し、かつ埋め込みウェル領域の上側主面に接触する下側主面を備えたウェル領域51Bとを有し、バイポーラトランジスタがウェル領域内に形成され、MOSトランジスタがウェル領域外のエピタキシャル層の上側主面に形成される。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

21 - 40 / 142

[ Back to top ]