Fターム[5F140BF42]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 形状、配置 (2,388) | 断面形状 (1,038)

Fターム[5F140BF42]の下位に属するFターム

溝掘りゲート (564)

Fターム[5F140BF42]に分類される特許

41 - 60 / 474

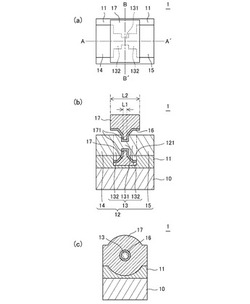

電界効果型トランジスタ、電界効果型トランジスタの製造方法、固体撮像装置、及び電子機器

【課題】 ゲート電極の微細化が可能な電界効果型トランジスタを提供する。

【解決手段】 本開示に係る電界効果型トランジスタは、基板10と、基板10上に形成され、フィン領域13と該フィン領域13の両端にそれぞれ形成されるソース領域14とドレイン領域15とを有する半導体層と、フィン領域13の少なくとも2面の一部と接する凸部171を有するゲート電極17と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことが可能な半導体装置、および半導体装置の製造方法を提供する。

【解決手段】サリサイド構造の半導体装置の高濃度ソース・ドレイン領域とゲート電極表面に形成される金属シリサイドを複数のアイランド状金属シリサイドからなる構成とする。これにより、全面に形成された金属シリサイド層よりも、シリコンと金属シリサイド層間の応力を緩和することができ、シリコンと金属シリサイド層間の応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことができる。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

半導体装置

【課題】トンネルトランジスタにおいて、その寄生容量を低減したゲート電極を提供する。

【解決手段】ゲート絶縁膜201を介して形成されたゲート電極202を挟むように形成された、第1導電型のソース領域121及び前記第1導電型とは逆導電型の第2導電型のドレイン領域122と、基板101内において前記ソース領域121と前記ドレイン領域122との間に形成された、第2導電型のチャネル領域123とを備える。そして、前記ゲート絶縁膜201は、前記ソース領域上に位置し、チャネル幅方向に平行な第1のエッジE1と、前記チャネル領域上又は前記ソース領域上に位置し、チャネル幅方向に平行な第2のエッジE2とを有し、第1の膜厚を有する第1の絶縁膜部分を有する。さらに、前記ゲート絶縁膜201は、前記第1の絶縁膜部分に対して前記ドレイン領域側に位置し、前記第1の膜厚よりも厚い第2の膜厚を有する第2の絶縁膜部分を有する。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置の製造方法

【課題】工程を簡素化して歩留まりを向上すると共に、安定した形状の電極を再現性よく得ることができる半導体装置の製造方法を提供する。

【解決手段】第1のレジスト膜11と、第1のレジスト膜11の開口よりも小さな開口を有する第2のレジスト膜12とを用いて、SiO2絶縁膜10を異方性ドライエッチングによってエッチングして、SiO2絶縁膜10にテーパ状の開口部101を形成する。このため、GaN層1を斜めに設置し直してSiO2絶縁膜10をエッチングする必要がなく、GaN層1を水平に設置したままSiO2絶縁膜10をエッチングすることができ、工程を簡素化できる。

(もっと読む)

MOSトランジスタおよびその製造方法

【課題】ドレイン端側においてゲート絶縁膜の膜厚を増大させる構成のMOSトランジスタにおいて、オン抵抗を低減し、耐圧を向上させる。

【解決手段】高電圧トランジスタ10のゲート電極構造をチャネル領域CHを第1の膜厚で覆う第1のゲート絶縁膜12G1と、第1の膜厚よりも大きい第2の膜厚で覆う第2のゲート絶縁膜12G2とし、第1のゲート絶縁膜12G1上の第1のゲート電極13G1と、第2のゲート絶縁膜12G2上の第2のゲート電極13G2の構成とする。更に、第1のゲート電極13G1と前記第2のゲート電極13G2とは、前記第1のゲート絶縁膜12G1から延在する絶縁膜12HKで隔てられる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】Y方向に延在するように半導体基板13に設けられ、底面18c及び対向する第1及び第2の側面18a,18bを有するゲート電極用溝18と、ゲート絶縁膜21を介して、ゲート電極用溝18の下部を埋め込むように配置されたゲート電極22と、ゲート電極用溝18を埋め込むように配置され、ゲート電極22の上面22aを覆う埋め込み絶縁膜24と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第1の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように、半導体基板13に設けられた第2の不純物拡散領域29と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】nチャネル型MISFET用のメタルゲート電極であるゲート電極GE1とpチャネル型MISFET用のダミーゲート電極GE2とを形成してから、nチャネル型MISFET用のソース・ドレイン領域とpチャネル型MISFET用のソース・ドレイン領域をそれぞれ形成する。その後、ダミーゲート電極GE2を除去し、ダミーゲート電極GE2が除去されたことで形成された凹部にpチャネル型MISFET用のメタルゲート電極を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】より良い製造工程で良好な特性の半導体装置を製造する技術を提供する。

【解決手段】導電性膜上に第1領域1Asを覆い、第1領域と隣接する第2領域1Adを開口したマスク膜を形成し、導電性膜中に不純物イオンを注入し、導電性膜を選択的に除去することにより、第1領域と第2領域との境界を含む領域にゲート電極GE1を形成する。その後、熱処理を施し、ゲート電極の側壁に側壁酸化膜7を形成し、ゲート電極の第2領域側の端部の下方に位置する半導体基板中にドレイン領域を形成し、ゲート電極の第1領域側の端部の下方に位置する半導体基板中にソース領域を形成する。かかる工程によれば、ドレイン領域側のバーズビーク部7dを大きくし、ソース領域側のバーズビーク部を小さくできる。よって、GIDLが緩和され、オフリーク電流を減少させ、また、オン電流を増加させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタにおいて、ホットエレクトロンのゲート絶縁膜へのトラップによるトランジスタ特性の経時劣化を減少させる。

【解決手段】N−−型の半導体層12の表面にボディ層19が配置されている。ボディ層19の表面にはN−型層23を含むソース層が配置されている。N−−型の半導体層12の表面には、N−型のドリフト層21が形成されている。このドリフト層21は、N型不純物濃度のピーク領域P1を有した第1の領域21Aと、この第1の領域21Aに隣接し、N型不純物濃度のピーク領域P1よりも深い位置にN型不純物濃度のピーク領域P2を有した第2の領域21Bとにより構成されている。第2の領域21Bの表面にはN+型のドレイン層25が形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ファインゲート構造を採用してゲート電極の微細化を図るも、ゲート電極の周辺における電界集中によるデバイス特性の変動・劣化を防止する、信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極8は、ファインゲート構造の幹状の下方部分8aと、下方部分8aの上端から当該上端よりも幅広に傘状(オーバーハング形状)に拡がる上方部分8bとが一体形成されており、下方部分8aは、下端を含む第1の部分8aaと、第1の部分8aa上の第2の部分8abとを有し、保護壁7は、第1の部分8aaの両側面のみを覆うように形成されている。

(もっと読む)

半導体装置の製造方法

【課題】複雑な工程を回避すると共に、高い有効仕事関数値を得ることにより、高歩留まり及び高性能の半導体装置を実現できるようにする。

【解決手段】ダミー電極22をマスクとして、n型活性領域13にp型の不純物イオンを導入することにより、n型活性領域13におけるダミー電極22の両側方にp型のソースドレイン領域25pを形成し、形成されたソースドレイン領域25pに熱処理を施す。熱処理を施した後に、n型活性領域13の上に、ダミー電極22を覆うように層間絶縁膜26を形成し、形成された層間絶縁膜26からダミー電極22を露出し、露出したダミー電極22を除去する。続いて、層間絶縁膜26におけるダミー電極22が除去された凹部26aに、第2の金属電極27を選択的に形成する。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル領域に応力を印加するよう作用する階段状のソース/ドレイン・エピタキシャル領域を、製造プロセスを有意に複雑あるいは冗長とすることなく形成する。

【解決手段】 ゲート電極をマスクとしてドーパントを注入し、半導体基板内にドーパント注入領域を形成する(S2)。サイドウォールの形成(S3)後、ゲート電極及びサイドウォールをマスクとして半導体基板内に第1のリセスを形成する(S4)。このとき、第1のリセスの内壁の一部からドーパント注入領域が露出される。その後、上記ドーパント注入領域を選択エッチングにより除去し、第1のリセスに連通し且つ第1のリセスより浅い第2のリセスを形成する(S5)。それにより、階段状のリセスが形成される。そして、第1のリセス及び第2のリセス内に、チャネル領域へのストレッサとして作用する半導体材料を成長させてソース/ドレイン領域を形成する(S6)。

(もっと読む)

半導体デバイス及びその製造方法

【課題】ゲート電極と上部導電層とのショートを防止した安定動作可能な縦型MOSトランジスタを有する半導体デバイスを提供する。

【解決手段】縦型MOSトランジスタを構成する半導体ピラー5Aは、第1の幅を有する上部5Aaと第2の幅を有する下部5Abを有し、上部5Aa側面は第2の絶縁膜6aと第3の絶縁膜6bで覆われ、下部5Abは側面から第2の絶縁膜6aまでゲート絶縁膜である第1の絶縁膜11Aで覆われており、ゲート電極13Aが第2及び第3の絶縁膜6により上部導電層18と絶縁されている。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置及びその製造方法

【課題】保護膜としてSiN膜が使用されている場合であっても、素子動作特性の変動を軽減することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置2は、ドレインドリフト領域12を有する半導体基板11と、ドレインドリフト領域12上に形成されたフィールド酸化膜17と、ゲート電極18と、中間絶縁膜17と、メタル層21,22と、これらを覆うSiN膜23と、SiN膜23上にO3−TEOSを用いたCVD法により形成され、カーボンを含有するPSG膜24とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】調整用金属を含む高誘電率膜を有するゲート絶縁膜を備えたMISトランジスタを有する半導体装置において、MISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、MISトランジスタnTrを備えている。MISトランジスタは、半導体基板10における素子分離領域11に囲まれた活性領域10aと、活性領域及び素子分離領域上に形成され、高誘電率膜15aを有するゲート絶縁膜16aと、ゲート絶縁膜上に形成されたゲート電極19aとを備えている。ゲート絶縁膜における素子分離領域上に位置する部分のうち、少なくとも一部分には、窒化領域20x,20yが設けられている。窒化領域20x,20yに含まれる窒素の窒素濃度をn1,n2とし、ゲート絶縁膜における活性領域上に位置する部分に含まれる窒素の窒素濃度をnとしたとき、n1>n、且つ、n2>nの関係式が成り立っている。

(もっと読む)

41 - 60 / 474

[ Back to top ]