Fターム[5J055DX03]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | バイポーラトランジスタ (323)

Fターム[5J055DX03]の下位に属するFターム

Fターム[5J055DX03]に分類される特許

41 - 60 / 189

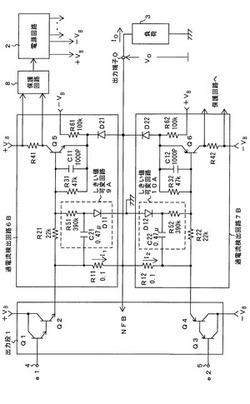

電力増幅器の過電流検出回路及びその方法

【課題】 しきい値を的確に可変して過電流検出の誤作動を防止する。

【解決手段】 過電流検出回路6Bは、Q2のエミッタと出力端子Oの間の電流検出抵抗R11の両端間に抵抗R21、R31が接続されている。R31の両端が過電流検出トランジスタQ5のベース−エミッタ間に接続されており、出力端子Oと−VB の間にダイオードD21、抵抗R61が接続されており、D21のカソードがQ5のエミッタと接続されている。R21とR31の接続点とグランド間には抵抗R51とD11が接続されており、R51とD11の接続点とQ2のエミッタの間にコンデンサC21が接続されている。R51、D11、C21のしきい値可変回路9Aは出力電圧の大きさが大きくなるとしきい値を大きくし、出力電圧の大きさが小さくなるとしきい値を小さくするが、C21とD11により、出力電圧の大きさが増加するときはしきい値を早く増大変化させ、減少するときはしきい値をゆっくり減少変化させる。

(もっと読む)

出力バッファ回路およびそれを用いたドライバ回路

【課題】 入出力信号が変化する際の過渡期間に出力バッファを構成するトランジスタへのバイアス電流を一時的に増強することで、バッファ回路全体の定常的なバイアス電流を抑制しつつ、高スルーレートが得られるバッファ回路を提供する。

【解決手段】 ドライバ回路200は信号レベル発生回路100により発生した信号SGOを出力バッファ回路110を駆動する回路150(プリバッファ回路)を介し、出力バッファ回路110により伝送線路120を駆動することで測定対象回路DUT140に伝える。プリバッファ回路150とこれを模擬したレプリカバッファ回路160とを互いに並列に備え、信号SGOが変化する際の入出力新信号の過渡期間において、レプリカバッファ回路160の出力電流に基づいて出力バッファ回路110の出力段トランジスタQN12、QP22の入力バイアス電流を一時的に増強する。

(もっと読む)

電子スイッチ装置

【課題】商用交流電源から電子機器への電力供給をオン又はオフするために使用者が操作するスイッチ部品として、各国の安全規格を満たさないスイッチ部品であっても自在に利用可能な電子スイッチ装置を提供すること。

【解決手段】本発明によれば、発振手段が、操作スイッチにより二次側コイルの両端が開放されると発振し、該二次側コイルの両端が短絡されると、一次側コイルのインダクタ値の減少に起因し発振が停止するので、二次側コイルの両端の状態が発振手段からの出力の出力態様に反映される。よって、かかる出力態様に基づくことにより、電力供給路の導通又は遮断を操作スイッチの操作状態に応じて行うことができる。ここで、操作スイッチが接続される二次側コイルは、一次側コイルに対して絶縁されているので、各国の安全規格を満たさないスイッチ部品を操作スイッチとして使用したとしても、操作スイッチを操作する使用者の安全を確保できる。

(もっと読む)

電源用逆流阻止回路

【課題】高電圧の回路に対応することができ、かつ、ICチップ化の可能な電源用逆流阻止回路を提供することを目的とする。

【解決手段】逆流阻止用FETのドレイン端子を入力端子に接続し、ソース端子を出力端子に接続し、ゲート端子をバイアス端子に接続し、逆流阻止用FETの出力側に一方の差動増幅用スイッチ素子を、入力側に他方の差動増幅用スイッチ素子を接続し、入力電圧が出力電圧より高いとき他方の差動増幅用スイッチ素子をオンして逆流阻止用FETを導通し、入力電圧が出力電圧より低いとき一方の差動増幅用スイッチ素子をオンして逆流阻止用FETを非導通とする逆流阻止回路において、入力端子と他方の差動増幅用スイッチ素子との間に、スイッチ素子保護用FETを、そのドレイン端子とソース端子を接続して挿入し、このスイッチ素子保護用FETのゲート端子を基準電圧発生回路に接続する。

(もっと読む)

センサ用出力ICおよびセンサ装置

【課題】センサ装置の回路規模および製造コストを従来よりも抑制しつつ、負荷短絡保護機能を実現する。

【解決手段】センサ用出力IC10は、センサからの検出信号に基づき、出力端子間をオン・オフするための出力用トランジスタ11を備える。センサ用出力IC10は、センサ用出力IC10内の温度が所定値以上になると、出力用トランジスタ11をオフ状態に維持する温度制限回路13と、出力用トランジスタ11のベース電位VBを所定値以下に制限する電圧制限回路15とを備えている。

(もっと読む)

ゲートドライブ回路

【課題】簡単な構成で、ワイドバンドギャップ半導体からなるスイッチ素子を駆動するゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体からなるスイッチ素子であって、ドレインとソースとゲートとを有し、前記ゲートをドライブする信号と前記ゲートとの間にコンデンサと抵抗の直列回路を介して接続され、前記ドレインと前記ゲートとの間に、ダイオードと電圧制限回路からなるゲート電圧クランプ回路とを備えることを特徴とする。

(もっと読む)

ゲート駆動回路の電源装置

【課題】初期充電回路が不要な自己給電形のゲート駆動回路の電源装置を提供することである。

【解決手段】電力用半導体スイッチ素子(3)に並列接続された、スナバダイオード(35)とスナバコンデンサ(37)とからなる直列回路と、端子電圧をゲート駆動回路(11)に電源電圧として印加する電源用コンデンサ(51)と、スナバコンデンサ(37)の正電位側端子と電源用コンデンサの正電位側端子間に介在されて、電源用コンデンサ(51)に充電電流を流すノーマリオンタイプのスイッチ素子(43)と、 ノーマリオンタイプのスイッチ素子(43)を制御するスイッチ制御回路と、を備える。スイッチ制御回路は、電源用コンデンサ(51)の端子電圧が所定値以上になったときにノーマリオンタイプのスイッチ素子(43)をオフさせるように構成される。

(もっと読む)

リセット装置

【課題】 従来より安価で簡単な回路構成で、確実に制御手段にリセット動作を実行させることができるリセット装置を提供する。

【解決手段】 制御手段にリセット信号を供給するリセット装置であって、ユーザによって操作可能である第1操作部及び第2操作部と、該第1操作部及び第2操作部が所定時間以上継続して同時に操作されているか否かを検出する検出部と、リセット信号を該制御手段に供給するリセット信号生成部とを備え、該第1操作部及び第2操作部が所定時間以上継続して同時に操作され、その後、同時に操作されなくなったときに、該リセット信号生成部がリセット信号を該制御手段に供給する。

(もっと読む)

電圧検出回路、及び電源装置

【課題】瞬停の度に電力を遮断せずともリセット用コンデンサを確実に放電可能とする。

【解決手段】スイッチング制御回路5への入力電圧の降下を検出し、当該スイッチング制御回路5に設けられたリセット用コンデンサC2を放電する放電回路55を作動させる電圧検出回路53であって、前記入力電圧の降下検出後の復電時から所定時間Ta後に電圧が復電判定値Vrに至る比較用信号を前記入力電圧から生成し、前記入力電圧の降下検出時から前記比較用信号の電圧が前記復電判定値Vrを超えるまで前記放電回路55の作動を継続して前記リセット用コンデンサC2を放電するようにした。

(もっと読む)

電圧駆動型半導体素子のゲート駆動装置

【課題】電圧駆動型半導体素子のスイッチング時に配線インダクタンスにより発生する素子間のサージ電圧を低減するためにゲート駆動回路のゲート抵抗を大きくすると、スイッチングの動作遅れ時間が長くなる。

【解決手段】電圧駆動型半導体素子のターンオフ時において、オフ信号によりゲート電荷を放電させる時にはオフ信号印加の初めに第1の抵抗体とコンデンサにより早く放電させることにより、スイッチング動作時間遅れの増加を防止し、その後第2の抵抗体に切換ることによりゲート電流を減少させることによって、素子間のサージ電圧を低減する。また、電圧駆動型半導体素子のターンオン時には、ダイオードが導通状態となることにより、該第1の抵抗体と該第2の抵抗体が並列構成となるので、前記第1の抵抗体の抵抗値により、早くゲート電荷を充電することができる。

(もっと読む)

スイッチング素子駆動装置

【課題】簡単な方式でスイッチング素子の導通損失の増加を抑えつつ、かつ駆動損失を低減できるスイッチング素子駆動装置を提供する。

【解決手段】1以上の電圧駆動型の半導体スイッチング素子Qを含む電力変換装置1と、前記半導体スイッチング素子のゲート制御信号を出力する制御装置5と、前記スイッチング素子の低ゲート電源電圧及び高ゲート電源電圧を駆動電源として供給するゲート電源回路6と、前記ゲート制御信号及び前記駆動電源に基づいて前記スイッチング素子を駆動するゲート駆動回路8とを備え、前記制御装置5は、前記ゲート制御信号のオンまたはオフの比率に基づいて前記ゲート駆動回路8に供給する前記低ゲート電源電圧及び高ゲート電源電圧を選択する構成を有する。

(もっと読む)

負荷制御装置

【課題】負荷への電力投入時における突入電流による素子の破壊又は劣化を防止しうる負荷制御装置を提供する。

【解決手段】操作スイッチ4から起動信号を受信したときに、制御部13は、第1電源部14への電力を供給する電源が第2電源部15から第3電源部16に切り替わる前に、主開閉部11に対して主スイッチ素子11aを導通させるための初期駆動信号を出力する。

(もっと読む)

負荷制御装置

【課題】スイッチ素子の発熱を抑制して小型化を図りつつ、開閉タイミングを正確に制御して、調光制御等の高度な負荷制御を行うことができる負荷制御装置を提供する

【解決手段】操作部28に入力された操作に応じて、制御部13が交流電源の1/2周期のうちトランジスタ構造の主開閉部11を導通させるために計数される主開閉部導通時間を設定し、電圧検出部18が第3電源部16に入力される電圧が所定の閾値に達したときから計数される第1所定時間と、主開閉部導通時間とが重複している時間だけ、主開閉部11を導通させることにより調光制御する。

(もっと読む)

電源回路、及び電子機器

【課題】FET内で発生するオン抵抗の上昇を抑制することで、使用するFETの耐性を下げ、以ってコストを低減する

【解決手段】FETをオン・オフするためのゲート電圧を所定タイミングで供給するゲートドライブ回路と、第一入力ラインと前記ゲートドライブ回路との間に介在して、第一入力ラインに供給されるゲートドライブ電圧の電圧値が一定の値になった場合に第一入力ラインとゲートドライブ回路とを導通させる第一のスイッチ回路と、スタート信号が前記FETのスイッチング動作をオフにすることを示すローレベルに変化した場合に、この信号変化に応じて第一入力ラインからゲートドライブ回路へのゲートドライブ電圧の供給を遮断する第二のスイッチ回路と、を有する。

(もっと読む)

半導体回路

【課題】低消費電流でノイズ耐性に優れた高圧側パワートランジスタを駆動する回路を提供する。

【解決手段】低圧側入力信号(HIN)に従って短い期間活性状態となるワンショットパルス(ON_B)を生成するワンショット回路(11)を設ける。第1および第2の電流供給部(14,16)により、入力信号およびワンショットパルスの発生するワンショットパルス信号に従って内部ノード(15)に電流を供給する。第1の内部ノードを流れる電流をウイルソンカレントミラー回路(20)で受け、電流検出部(R3)により電圧信号に変換し、ゲートドライバ(DRV)により、スイッチングパワートランジスタの駆動信号を生成する。

(もっと読む)

無電圧接点入力回路

【課題】 フォトカプラやDC−DCコンバータを用いない無電圧接点入力回路を提供する。

【解決手段】 信号入力部1に入力された無電圧接点信号が「開」か「閉」かを判断するCPU2と、入力された無電圧接点信号を、H/L信号としてCPU2に通知するためのインターフェース回路3とを有し、インターフェース回路3は、信号入力部1にコンデンサを設け、CPU2の入力ポートPiに無電圧接点信号の開/閉に対応するH/L信号を出力する出力トランジスタTr4と、コンデンサC1,C2を充電すると共に出力トランジスタTr4を起動するための起動トランジスタTr1と、コンデンサC1,C2の充電電荷を放電させるための放電トランジスタTr2とを備え、CPU2が入力ポートPiに入力される信号H/Lの状態を所定のタイミングで見ることで無電圧接点信号の開/閉を判断する。

(もっと読む)

受信装置

【課題】主に自動車のドアの施解錠などに用いられる受信装置に関し、安価であり、かつ受信装置単体で正負逆転した電圧に耐えうることを両立したものを提供することを目的とする。

【解決手段】保護手段35を、一つのツェナーダイオード34と複数の整流手段31〜33で構成し、ツェナーダイオード34のアノード電極をグランドに接続すると共に、カソード電極を、複数の整流手段31〜33の一端と接続し、複数の整流手段31〜33の他端はスイッチ手段5〜7と接続する。

(もっと読む)

スイッチ回路に給電する供給回路

エネルギ効率を改善するよう、スイッチ回路(2)に給電する供給回路(1)は、電源(7)から第1の量の入力電力を受けて、スイッチ回路(2)の制御部(3)を有する出力回路(5)へ第1の量の出力電力を供給する第1の供給モードと、第2の量の入力電力を受けて、第2の量の出力電力を供給する第2の供給モードとを有する。第1の量の出力電力は、第2の量の出力電力よりも大きい。第2の量の入力電力は、零よりも大きく、且つ、スイッチ回路(2)を動作させるのに必要なスイッチ電力の量よりも小さい。スイッチ回路(2)は、負荷(8)を切り換えるリレーを有してよい。第1の量の入力電力は、リレーの主接触部を介して到達してよい。スイッチ(47)は、出力信号レベルを切り替えてよい。リレーは、双安定リレーであってよい。  (もっと読む)

(もっと読む)

整流回路、該整流回路の制御回路及びこれらそれぞれの回路を内蔵した集積回路素子

【要 約】

【課 題】 低順方向電圧降下、逆流しない整流回路を実現する。

【解決手段】 第3半導体素子の電流路の他端の電位が第2半導体素子の電流路の他端の電位と同一又は超えるとき、該第2半導体素子の電流路は導通し該第2半導体素子の電流路の一端の電位が伝達される第1制御端の電位は低下し第1半導体素子の電流路は非導通であり、前記第3半導体素子の電流路の他端の電位が前記第2半導体素子の電流路の他端の電位未満のとき、該第2半導体素子の電流路は非導通し該第2半導体素子の電流路の一端の電位が伝達される前記第1制御端の電位は上昇し前記第1半導体素子の電流路が導通する前記第2半導体素子の電流路の他端と前記第3半導体素子の電流路の他端間を整流作用電流路とすることを特徴とする整流回路。

(もっと読む)

負荷回路の駆動装置

【課題】アンプAMP1が有するオフセット電圧による測定誤差を低減し、マルチソースFET(T1)を小型化することが可能な負荷回路の駆動装置を提供する。

【解決手段】アンプAMP1及び抵抗R1を備え、メインFET(T11)の両端電圧Vdsに比例して変化する参照電流I1を生成する参照電流生成回路11と、アンプAMP1と同一のオフセット電圧を備えたアンプAMP2及び抵抗R2を備え、サブFET(T12)の両端電圧に比例して変化する基準電流I2を生成する基準電流生成回路12を備える。そして、参照電流I1から基準電流I2を差し引いた差分電流(I1−I2)を生成し、この差分電流が正の値である場合にこの差分電流に応じた電圧を生成する。生成した電圧が閾値電圧に達した場合に、MOSFET(M3)、(M4)をオンとし、マルチソースFET(T1)の遮断状態を維持する。

(もっと読む)

41 - 60 / 189

[ Back to top ]