Fターム[5J056DD29]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | P型FETとN型FETの組合せ (1,723) | 相補動作するもの、CMOS (940)

Fターム[5J056DD29]に分類される特許

21 - 40 / 940

半導体装置

【課題】従来の半導体装置では、エンファシスの有無により消費電流が変動する問題があった。

【解決手段】本発明の半導体装置は、抵抗値を、エンファシスモードにおいて第1の抵抗値とし、非エンファシスモードにおいて第1の抵抗値よりも小さな第2の抵抗値とする可変抵抗30と、出力インピーダンスを、エンファシスモードにおいて第3の抵抗値とし、非エンファシスモードにおいて前記第3の抵抗値よりも大きな第4の抵抗値とする第1の駆動部10と、出力インピーダンスを、エンファシスモードにおいて第5の抵抗値とし、非エンファシスモードにおいて第5の抵抗値よりも大きな第6の抵抗値とする第2の駆動部11と、入力信号に応じて第1、第2の駆動部の導通状態を制御すると共に、エンファシスモードと非エンファシスモードとにおいて第1、第2の駆動部の出力インピーダンスと可変抵抗の抵抗値を切り換える制御部と、を有する。

(もっと読む)

出力駆動回路及びトランジスタ出力回路

【課題】本発明は、出力駆動回路及びトランジスタ出力回路を提供する。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

(もっと読む)

半導体装置

【課題】出力信号を高速に変化させかつオーバーシュートやアンダーシュートを抑制できるようにする。

【解決手段】入力信号を反転して出力する主ドライバ11に加えて、補助ドライバ12を設け、入力信号の電圧変化に応じて出力信号が第1の電圧レベルから第2の電圧レベルへ変化するときに、変化開始から主ドライバの出力信号がある電圧レベルを超えるまでの期間では信号変化を補助するように制御部15により補助ドライバの動作を制御し、主ドライバの出力信号がある電圧レベルを超えてから第2の電圧レベルになるまでの期間に信号変化を抑制するように制御部により補助ドライバの動作を制御するようにして、出力信号における信号変化の高速性を向上させ、かつオーバーシュートやアンダーシュートを抑制できるようにする。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

CMOS論理回路

【課題】貫通電流を抑制しつつ、ドライブ能力を向上することが可能なCMOS論理回路を提供する。

【解決手段】CMOS論理回路は、第1の電圧線に一端が接続され、印加される電圧に対して非線形となるインピーダンス特性を有する抵抗性素子と、第1、第2のMOSトランジスタで構成される第1のインバータ回路を備える。CMOS論理回路は、第3、第4のMOSトランジスタからなる第2のインバータ回路を備える。CMOS論理回路は、抵抗性素子と並列に接続され、ゲートが第3のMOSトランジスタP2の他端に接続された第5のMOSトランジスタを備える。CMOS論理回路は、第1の電圧線と第1の出力端子との間に接続され、ゲートが第3のMOSトランジスタの他端に接続された第6のMOSトランジスタを備える。

(もっと読む)

ニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器

【課題】回路規模の増大を抑制し、低消費電力化を実現するフラッシュ型AD変換器を提供すること。

【解決手段】本発明の一実施形態によると、第1のCMOS回路と、共通するローティングゲートを有し、3個のゲートが前記フローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路とに並列に接続する2n−1−1個(nは3以上の整数)のニューロンCMOS回路と、を備える量子化出力部と、前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、前記量子化出力部又は前記エンコード部に接続するn個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器が提供される。

(もっと読む)

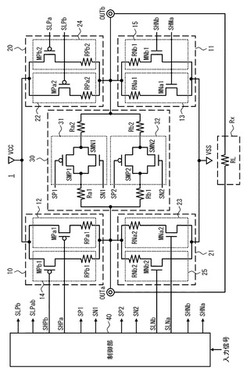

出力回路

【課題】差動出力電圧の振幅のばらつきを抑制した出力回路を提供する。

【解決手段】出力回路は,定電圧ノードと基準電源との間に,複数のスイッチ素子のオン,オフにより合成抵抗値が可変制御可能な複数の抵抗を有し,定電圧ノードに第1の電流を生成する定電流生成回路と,第1の電流をカレントミラーにより生成した第2の電流を,内部回路から供給される内部差動信号に応じて,出力端子対に出力する出力駆動回路と,出力端子対の出力差動電圧の差が所望の電圧差と一致するように,定電流生成回路の複数のスイッチ素子を制御するスイッチ素子制御信号を生成する出力振幅調整部とを有する。

(もっと読む)

CMOS論理集積回路

【課題】異なる論理レベルの信号を高速に伝達可能なCMOS論理集積回路を提供する。

【解決手段】レベルシフト回路とCMOS論理回路とを備えたことを特徴とするCMOS論理集積回路が提供される。前記レベルシフト回路は、第1の低電位と前記第1の低電位よりも高い第1の高電位との間で変化する第1の論理レベルの信号を前記第1の低電位と前記第1の高電位よりも高い第2の高電位との間で変化する第2の論理レベルの信号に変換する。前記CMOS論理回路は、前記第1の論理レベルの第1の信号がゲートに入力される第1のNチャンネル形MOSFETと、前記第1のNチャンネル形MOSFETに直列に接続され前記第1の信号と反転関係にある前記第2の論理レベルの第2の信号がゲートに入力される第2のNチャンネル形MOSFETとを有する。

(もっと読む)

半導体装置、及び出力バッファのインピーダンスを調整する方法

【課題】出力バッファのインピーダンスを制御する複数の制御ビットを転送するデータバスの配線面積を削減できる半導体装置、及び出力バッファのインピーダンスを調整する方法を提供する。

【解決手段】インピーダンス制御情報を生成するZQ回路(ZQ回路40)と、前記インピーダンス制御情報を受けて自身のインピーダンスが制御される出力バッファ(出力回路80)と、を備え、前記インピーダンス制御情報を構成する複数の制御ビット情報は前記ZQ回路からシリアルに転送される。

(もっと読む)

半導体装置

【課題】出力回路のインピーダンス調整の精度を向上する半導体装置を提供する。

【解決手段】各々が調整可能なインピーダンスを備える複数の単位バッファを含む出力回路(出力バッファ101)と、複数の単位バッファ回路のうちの1または複数個の単位バッファ回路を選択的に活性化する制御回路(出力制御回路150)と、複数の単位バッファのそれぞれのインピーダンスを調整するインピーダンス調整部であって、当該インピーダンス調整部は、制御回路によって選択的に活性化された1又は複数個の単位バッファ回路の個数が変化することに応じて複数の単位バッファのそれぞれのインピーダンスを調整する、インピーダンス調整部(インピーダンス調整部30)と、を備える。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

制御信号発生回路およびそれを用いた半導体装置

【課題】半導体装置の制御に好適な制御信号発生回路を提供する。

【解決手段】ジョンソンカウンタ31は、フリップフロップFF1〜FF4およびゲート回路41〜44を含み、順次入力されるスタート信号ST1〜ST4に応答してそれぞれ制御信号C1〜C4を「H」レベルにした後、順次入力されるストップ信号SP1〜SP4に応答してそれぞれ制御信号C1〜C4を「L」レベルにする。したがって、多数のフリップフロップを用いることなく、所望の時間間隔で制御信号C1〜C4を順次「H」レベルにし、順次「L」レベルにすることができる。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、第1及び第2の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、複数の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

半導体装置

【課題】新たな構成の半導体装置を提供する。

【解決手段】半導体装置は、p型の第1のトランジスタ、n型の第2のトランジスタ、第3のトランジスタ及び第4のトランジスタを有する。第3のトランジスタのソース又はドレインの一方は、第1の電位を供給することができる機能を有する配線に接続され、他方は、第1のトランジスタのソース又はドレインの一方に接続される。第2のトランジスタのソース又はドレインの一方は、第1のトランジスタのソース又はドレインの他方と接続され、他方は、第4のトランジスタのソース又はドレインの一方に接続される。第4のトランジスタのソース又はドレインの他方は、第1の電位よりも低い第2の電位を供給することができる機能を有する配線に接続される。第3のトランジスタ及び第4のトランジスタのチャネル形成領域には酸化物半導体材料が用いられる。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1乃至第4のノードを有する論理回路と、第1のノード、第2のノード、及び第3のノードと接続された第1の制御回路と、第1のノード、第2のノード、及び第4のノードと接続された第2の制御回路と、第1のノード、第1の制御回路、及び第2の制御回路に接続された第1の記憶回路と、第2のノード、第1の制御回路、及び第2の制御回路に接続された第2の記憶回路と、を有する記憶装置である。

(もっと読む)

半導体集積回路

【課題】記憶装置の消費電力を低減すること、記憶装置の面積を低減すること、記憶装置を構成するトランジスタの数を低減する。

【解決手段】第1の出力信号及び第2の出力信号の電位を比較する比較器と、第1の酸化物半導体トランジスタ及び第1のシリコントランジスタを有する第1のメモリ部と、第2の酸化物半導体トランジスタ及び第2のシリコントランジスタを有する第2のメモリ部と、当該第1の出力信号及び当該第2の出力信号の電位を確定する出力電位確定器とを有し、当該第1の酸化物半導体トランジスタのソース又はドレインの一方は、当該第1のシリコントランジスタのゲートに電気的に接続されており、当該第2の酸化物半導体トランジスタのソース又はドレインの一方は、当該第2のシリコントランジスタのゲートに電気的に接続されている記憶装置に関する。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な半導体装置を提供する。

【解決手段】レベルシフタ、第1のバッファ、及び第2のバッファと、第1のスイッチ及び第2のスイッチと、第1の端子、第1の端子から入力される信号の反転信号が入力される第2の端子、及び第1のスイッチ及び第2のスイッチの状態を制御するクロック信号が入力される第3の端子と、を備えるラッチ回路を有する。レベルシフタの第1の出力端子は、第1のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの一の入力端子と接続し、レベルシフタの第2の出力端子は、第2のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの他の入力端子と接続する。レベルシフタの第1の入力端子は、第1のバッファの出力端子と接続し、レベルシフタの第2の入力端子は、第2のバッファの出力端子と接続する。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

21 - 40 / 940

[ Back to top ]