Fターム[5J056DD29]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | P型FETとN型FETの組合せ (1,723) | 相補動作するもの、CMOS (940)

Fターム[5J056DD29]に分類される特許

61 - 80 / 940

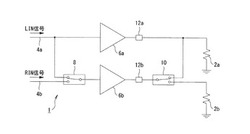

出力バッファー回路

【課題】出力バッファーの面積・体積・部品点数の増加を抑制するとともに、ドライブ能力を向上させることが可能な出力バッファー回路を提供する。

【解決手段】第一駆動信号LINを伝達する第一入力経路4a、第二駆動信号RINを伝達する第二入力経路4b、第一入力経路4aと対応する第一出力バッファー6a及び第二入力経路4bと対応する第二出力バッファー6bを備える出力バッファー回路1において、入力経路切り替え手段8が、ステレオモード及びモノラルモードのうち、モノラルモードでは、第一入力経路4aと第一出力バッファー6a及び第二出力バッファー6bとを電気的に接続させ、出力経路切り替え手段10が、第一出力バッファー6a及び第二出力バッファー6bと、第一入力経路4a及び第一出力バッファー6aと対応する第一負荷2aとを、電気的に接続させる。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】7Tr3Cで構成されるインバータ回路1において、入力端子IN1から印加される電圧に応じてオンオフするトランジスタT3と、制御素子10とを介して、入力電圧Vin2がトランジスタT2のゲートに入力される。入力電圧Vin1,Vin2がともにハイレベルの電圧Vddとなっている期間においては、入力電圧Vin3がハイレベルの電圧Vddとなっているときだけ、トランジスタT1,T2の双方のゲートにオン電圧が印加される。

(もっと読む)

半導体装置

【課題】可変抵抗回路の抵抗値の調整可能範囲が大きな半導体装置を提供する。

【解決手段】この半導体装置は、複数組の抵抗素子RA,RBおよび複数組のトランジスタP,Qを含む出力バッファDOBと、複数のレプリカ回路RPと、複数組の演算増幅器AP,ANとを備え、出力バッファDOBの出力インピーダンスZp,Znが所定値になるように、複数組のトランジスタP,Qのドレイン電流を調整する。したがって、製造プロセスなどの変動によって抵抗素子RA,RBの抵抗値が大きく変動した場合でも、出力インピーダンスZp,Znを所定値に設定できる。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、クロックツリーにおける消費電流を削減しながら、同期回路間の同期動作を行うことが難しかった。

【解決手段】本発明にかかる半導体装置は、動作クロック信号CLKに応じて第1のクロック信号を出力し、第1の応答時間で第1のクロック信号のエッジを変化させる第1のクロックバッファ(VCB11〜VCB14のうちの一つ)と、動作クロック信号CLKに応じて第2のクロック信号を出力し、第2の応答時間で第2のクロック信号のエッジを変化させる第2のクロックバッファ(VCB11〜VCB14のうちの他の一つ)と、第1のクロック信号に同期して動作し、第1の電圧レベルを閾値電圧とする第1の論理回路と、第2のクロック信号に同期して動作し、第2の電圧レベルを閾値電圧とする第2の論理回路と、を有し、第1、第2の論理回路は、動作クロック信号に応じて一のタイミングで動作する。

(もっと読む)

半導体装置

【課題】キャリブレーション回路に用いる基準電位生成回路を改良する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ110と、基準電位VREFを生成する基準電位生成回路200と、キャリブレーション端子ZQに現れる電位と基準電位VREFとを比較する比較回路151と、比較回路151による比較の結果に基づいてレプリカバッファ110の出力インピーダンスを変化させるコントロール回路140とを備える。基準電位生成回路200は、イネーブル信号ENに応答して活性化される電位発生部210と、イネーブル信号ENに関わらず活性化される電位発生部220とを含み、電位発生部210の出力ノードと電位発生部220の出力ノードが比較回路151に共通接続されている。これにより、イネーブル信号ENが活性化する前に正しく基準電位VREFを出力することができる。

(もっと読む)

半導体装置

【課題】切り替えスイッチのオンオフに伴うノイズがバイアスラインに重畳するのを防ぐ。

【解決手段】バイアス電流が流れるバイアスラインVLと、バイアス電流の量を制御信号DDに基づいて切り替える切り替えスイッチ70と、制御信号DDが供給される制御ラインとバイアスラインVLとの間の寄生容量を介して制御信号DDの変化時に生じるバイアスラインVLの電位変動を相殺する相殺回路91〜93とを備える。本発明によれば、切り替えスイッチ70のオンオフに伴ってバイアスラインVLに生じるノイズを相殺することが可能となる。

(もっと読む)

レベルシフト回路

【課題】入力信号のレベルが低電圧であっても、信号レベルの変換を高速かつ確実に行うことのできるレベルシフト回路を提供する。

【解決手段】 実施形態のレベルシフト回路は、厚膜のPMOSトランジスタTP1(TP2)および厚膜のNMOSトランジスタTN1(TN2)からなる一対の相補回路を有し、厚膜のNMOSトランジスタTN1(TN2)のゲートに入力された低電圧レベルの信号A(/A)を、厚膜のPMOSトランジスタTP2(TP1)を介して昇圧し、高電圧レベルの信号Z(/Z)を出力する。この一対の相補回路のそれぞれの出力端子と接地端子GNDとの間には、ブースター回路11(12)がそれぞれ接続されている。ブースター回路11(12)は、高電圧レベルの出力信号/Z(Z)の立ち下りを加速する。

(もっと読む)

出力バッファ回路

【課題】出力信号のデューティを保ちつつ消費電流の変化を低減する。

【解決手段】出力バッファ回路は、出力回路(300)と、第1入力回路(210)と、第2入力回路(220)と、第1クランプ回路(110)と、第2クランプ回路(120)とを具備する。出力回路(300)は、第1出力トランジスタ(P301)と第2出力トランジスタ(N301)とを備え、出力信号(VOUT)を出力する。第1クランプ回路(110)および第2クランプ回路(120)のそれぞれは、カスコード接続される第1導電型のトランジスタ(P111/P121)と、第2導電型のトランジスタ(N111/N121)とを備える。第1クランプ回路(110)は、所定の期間第1入力回路(210)の出力電圧(VA1)をクランプする。第2クランプ回路(120)は、所定の期間第2入力回路(220)の出力電圧(VA2)をクランプする。

(もっと読む)

低リーク電圧検出回路

【課題】ゲート電極駆動電圧信号が不十分な電圧のためにリーク電流が発生することのない低リーク電圧検出回路及び方法を提供する。

【解決手段】伝送ゲート202、フィードバック通路204、制御器200を備え、第1の電位によって給電された第1の装置と第2の電位によって給電された第2の装置との間に置かれた低リーク電圧検出回路である。第1の装置と第2の装置との間における電位のミスマッチは、リーク電流が第2の装置の入力段を流れることを招く可能性がある。低リーク電圧検出回路を採用することによって、第1の装置の発生した高論理レベルは、対応的にほぼ第2の電位の振幅と等しい高論理レベルに転換される。

(もっと読む)

出力回路

【課題】スキューの少ない出力信号を出力する回路の実現。

【解決手段】差動入力信号INN,INPを受けて、差動駆動信号を出力する駆動回路BF1,BF2;BF3,BF4と、共通の定電流源12に接続され、差動駆動信号に応じて逆相のスイッチ動作を行う2個のトランジスタMN1,MN2を有する差動出力部と、駆動回路の2個の駆動部の電源15,16の電位を、定電流源12と2個のトランジスタの接続ノードTailの電位に応じた電位にするレベル調整回路AMP1,AMP2と、を有する出力回路。

(もっと読む)

信号デスキュー方法および装置

【課題】超低圧VDDデジタル回路においては、クロックスキューは厳密な時間収率の劣化を招く大きな原因であるが、コンピュータによる設計の高度な自動化(EDA)手段の様々なプロセスが存在する中でのスキュー調和がとれたクロックツリーを実現する。

【解決手段】参照信号およびローカル信号を受信し、それらを比較して位相差を検出するための位相比較器、位相差の値に関連して制御信号のオン/オフを切り替えるための制御回路、およびローカル信号バッファーを有し、前記ローカル信号バッファーはnMOSトランジスタおよび/またはpMOSトランジスタを有しており、前記制御信号に応じてホットキャリアインジェクションストレスをnMOSトランジスタまたはpMOSトランジスタに掛けてnMOSトランジスタまたはpMOSトランジスタのしきい値電圧を増加させる。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

出力回路

【課題】回路規模が小さく、出力トランジスタのしきい値電圧がばらついてもノイズを抑えつつターンオフ時間を短縮する。

【解決手段】駆動信号SdがLの時、トランジスタT1がオン、T2がオフしてVGS(T3)がほぼ電源電圧Vccに等しくなりトランジスタT3がオンする。駆動信号SdがHになるとトランジスタT1がオフ、T2がオンする。トランジスタT4がオンするので抵抗R2がバイパスされ、トランジスタT3のゲート電荷はトランジスタT4、T2を通して急速に放電する。VGS(T3)がVth(T4)+VDS(T2)よりも低下すると、トランジスタT4はオフとなり、以後はトランジスタT3のゲート電荷が抵抗R2とトランジスタT2を通して緩やかに放電する。トランジスタT3、T4のしきい値電圧は一致する傾向があるので、VGS(T3)がVTH(T3)に低下した時点でトランジスタT4をオフできる。

(もっと読む)

半導体装置

【課題】 ゲート−ソース逆バイアス駆動の動作原理を定量化し、MOSTのしきい電圧と動作電圧の関係を明らかにすることにより、逆バイアス駆動の原理を活用した複数のMOSTの組み合わせを用いて、動作電圧1V以下の高速低電圧動作を可能にする。

【解決手段】 低VtのMOSTを含む回路のリーク電流を、MOSTのゲート(G)とソース(S)を逆バイアスする各種の駆動方式によって低減する。低VtのMOSTに各種のG−S逆バイアスを加えることにより、リーク電流の少ない1V以下の高速低電圧CMOS論理回路、あるいはメモリ回路が実現される。

(もっと読む)

半導体集積回路

【課題】

CMOS回路に中間電圧の入力信号が長時間連続して入力された場合にも貫通電流の発生を短時間にとどめることができる半導体集積回路を提供する。

【解決手段】

本発明の一実施態様に係る半導体集積回路は、入力端子と、出力端子と、ゲートが前記入力端子に接続されソースが高電位電源配線に接続された第1PMOSトランジスタ及びゲートが前記入力端子に接続されソースが低電位電源配線に接続された第1NMOSトランジスタを含み、当該第1PMOSトランジスタと当該第1NMOSトランジスタとが同時に導通しないように構成された第1CMOS回路と、入力端が前記第1CMOS回路に接続され出力端が前記出力端子に接続された第2CMOS回路と、この第2CMOS回路の出力端とと高電位電源配線及び高電位電源配線との間にそれぞれ配置された第2PMOSトランジスタと第2NMOSトランジスタと、を備える。

(もっと読む)

クロックバッファ回路及びクロック分配回路

【課題】クロック源の消費電力を増大させることなく、動作クロック周波数に応じて駆動能力を変化させることにより消費電力低減可能なクロックバッファ回路を提供すること。

【解決手段】クロック信号を伝達するバッファ部102と、クロック信号の参照クロック信号に対する逓倍数をカウントし、バッファ部102に対して逓倍数に基づいたイネーブル信号を出力する駆動能力切替部101と、を備え、バッファ部102は、当該バッファ部102の入力に接続された入力インバータ7と、イネーブル信号によりオンオフが可能であって、それぞれの出力が当該バッファ部の出力に共通に接続された複数の出力インバータ13〜28と、を備え、入力インバータ7が1個のCMOSインバータからなるクロックバッファ回路。

(もっと読む)

レベルシフト回路およびスイッチング電源装置

【課題】 高耐圧プロセスを使用することなく、回路的に高耐圧化したレベルシフト回路を実現できるようにする。

【解決手段】 一対のCMOSインバータを有し一方のインバータの出力ノードを他方のインバータのPチャネル型MOSトランジスタのゲート端子に交差結合してなるラッチ回路(22)と、該ラッチ回路のいずれか一方の出力ノードに接続されたCMOSインバータからなる出力段(23)とを有するレベルシフト回路において、ラッチ回路を構成する一対のCMOSインバータの各Pチャネル型のMOSトランジスタ(Mp1,Mp2)とNチャネル型のMOSトランジスタ(Mn1,Mn2)との間に、ゲート端子が電源電圧と接地電位の中間の電位が印加される第3電圧端子(FGND)に接続されたPチャネル型のMOSトランジスタ(Mp4,Mp5)をそれぞれ直列形態で設けた。

(もっと読む)

61 - 80 / 940

[ Back to top ]