Fターム[5J056DD29]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | P型FETとN型FETの組合せ (1,723) | 相補動作するもの、CMOS (940)

Fターム[5J056DD29]に分類される特許

41 - 60 / 940

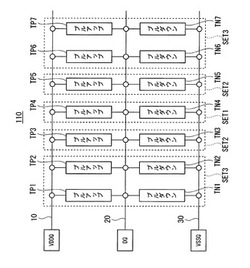

半導体装置

【課題】出力インピーダンスを切り替えた場合の出力トランジスタに対する電源配線抵抗等の見かけ上の変動を抑制し、出力インピーダンスを切り替えた際の出力インピーダンスの誤差を低減する。

【解決手段】本発明による半導体装置は、電源端子に接続された電源配線(10)と、出力端子に接続された信号配線(20)と、前記電源配線と前記信号配線との間に並列接続された複数のトランジスタ(TP1〜TP7,TN1〜TN7)と、前記複数のトランジスタのうち、特定のトランジスタ(TP4,TN4)を基準として前記電源配線および前記信号配線の長手方向において相互に対照をなす位置関係にあるトランジスタを単位として前記複数のトランジスタを選択的に活性化させる制御回路とを備える。

(もっと読む)

出力バッファ回路

【課題】 著しい遅延の増大を招くことなく、出力バッファ回路の貫通電流を防止する。

【解決手段】 出力段駆動部100は、出力信号VOUTを立ち下げる場合、Pチャネルトランジスタ201をOFFに遷移させ、そのドレイン電流が閾値電流Ith1を下回ったとき、Nチャネルトランジスタ202をONに遷移させ、出力信号VOUTを立ち上げる場合、Nチャネルトランジスタ202をOFFに遷移させ、そのドレイン電流が閾値電流Ith2を下回ったとき、Pチャネルトランジスタ201をONに遷移させる。閾値設定部130は、入力信号VINに出力信号VOUTを立ち下げる変化があったとき、Pチャネルトランジスタ201のドレイン電流に応じた値に閾値電流Ith1を設定し、閾値設定部140は、入力信号VINに出力信号VOUTを立ち上げる変化があったとき、Nチャネルトランジスタ202のドレイン電流に応じた値に閾値電流Ith2を設定する。

(もっと読む)

イネーブル信号生成回路

【課題】後段のイネーブル回路を確実に制御し、また電源電圧が高くなっても消費電流が増大しないようにする。

【解決手段】制御入力端子1にゲートが接続されソースがトランジスタMN2を介して接地に接続されたトランジスタMN1と、トランジスタMN1のドレインと電源VDDとの間に接続された抵抗R2と、抵抗R2の両端にソースとドレインが接続されたトランジスタMP1と、トランジスタのMP1ゲートとソース間に接続された抵抗R3と、ソースがトランジスタMP1のゲートに接続されゲートがトランジスタMP1のドレインに接続されドレインが負荷回路3に接続されたトランジスタMP2とを備え、トランジスタMP2のゲートを制御出力端子2に接続した。

(もっと読む)

演算回路及び演算回路の駆動方法

【課題】消費電力を低減する。

【解決手段】入力信号を元に論理演算処理を行い、論理演算処理の結果に応じて設定される電位を記憶データとして保持し、記憶データに応じた値の信号を出力信号として出力する機能を有し、論理演算処理を行う演算部と、出力信号の電位を、論理演算処理の結果に応じて値が設定される第1の電位に設定するか否かを制御する第1の電界効果トランジスタと、出力信号の電位を、基準電位である第2の電位に設定するか否かを制御する第2の電界効果トランジスタと、を備える。

(もっと読む)

半導体装置

【課題】貫通電流を少なくできる半導体装置を提供する。

【解決手段】データを出力する出力部を各々備えた複数の半導体チップと、出力部の各々と接続された配線と、配線を介して複数の半導体チップの各々からデータを受け付ける受付部と、を含み、出力部が順番に駆動する半導体装置にて、出力部の各々は、オン状態時の抵抗値を変更可能であり、自己の駆動開始時から自己の次に駆動を開始する出力部の駆動開始時の前のタイミングまでの第1期間の間は、オン状態時の抵抗値を第1抵抗値にしてデータを配線に出力し、第1期間が経過した時点から自己の駆動終了時までの第2期間の間は、オン状態時の抵抗値を第1抵抗値よりも大きい第2抵抗値にしてデータを配線に出力する。

(もっと読む)

回路及び回路の駆動方法

【課題】消費電力を低減する。

【解決手段】入力信号を元に論理演算処理を行い、論理演算処理の結果に応じて設定される電位を記憶データとして保持し、記憶データに応じた値の信号を出力信号として出力する機能を有する演算回路を具備し、演算回路は、論理演算処理を行う演算部と、記憶データの電位を、論理演算処理の結果に応じた電位に設定するか否かを制御する第1の電界効果トランジスタと、記憶データの電位を、基準電位に設定するか否かを制御する第2の電界効果トランジスタと、記憶データに応じた値の信号を出力信号として出力するか否かを制御する第3の電界効果トランジスタと、を備える。

(もっと読む)

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

半導体記憶装置

【課題】電源電圧の停止及び復帰を行う構成において、外部回路より半導体記憶装置を制御するための信号数を削減する。

【解決手段】酸化物半導体を半導体層に有するトランジスタを有する記憶回路と、記憶回路に保持されたデータを読み出すための電荷を蓄積する容量素子と、容量素子への電荷の蓄積を制御するための電荷蓄積回路と、データの読み出し状態を制御するデータ検出回路と、電源電圧が供給された直後の期間において、電源電圧の信号と電源電圧を遅延させた信号とにより、電荷蓄積回路による容量素子への電荷の蓄積をさせるための信号を生成するタイミング制御回路と、容量素子の一方の電極の電位を反転して出力するインバータ回路と、を有する構成とする。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

出力回路及びそのドライブ能力テスト方法。

【課題】容量性負荷が外部端子に接続されている場合でも、出力バッファのドライブ能力の診断が可能な出力回路とテスト方法を提供する。

【解決手段】外部負荷が接続される第1、第2の外部端子と、前記第1、第2の外部端子に接続される前記外部負荷を駆動する出力バッファ部と、第1の制御信号に応じてオン状態となることで、前記第1、第2の外部端子を導通させるスイッチ部と、テスト時において、前記出力バッファ部により、前記第1、第2の外部端子に対して互いに逆相の信号を出力させ、且つ、前記第1の制御信号により前記スイッチ回路をオン状態とするテスト制御部と、を有する出力回路。

(もっと読む)

半導体装置

【課題】 待機動作時のオフリーク電流を削減した論理回路を含む半導体装置を提供することを目的とする。

【解決手段】 半導体装置100は、第1の動作電圧または第1の動作電圧よりも小さい第2の動作電圧を供給する電源供給部110と、電源供給部110から第1または第2の動作電圧を受け取る低しきい値のP型トランジスタTpと、トランジスタTpと基準電位との間に接続されたN型トランジスタTnとを有し、トランジスタTp、Tnは、ゲートに入力された信号Dinに応じて出力信号Doutを生成する論理回路を構成する。電源供給部110は、通常動作時、第1の動作電圧をトランジスタTpのソースに供給し、待機動作時、第2の動作電圧をトランジスタTpのソースに供給する。第2の動作電圧は、トランジスタTp、Tnそれぞれのゲート・ソース間電圧の振幅がトランジスタTp、Tnのしきい値よりも大きくなるように設定される。

(もっと読む)

容量性スピーカ駆動回路

【課題】高音の音声信号が所定のレベル以上で所定時間以上入力されたときに、利得を低減させて高音過電流が発生することを防止する。

【解決手段】出力ドライバのパワートランジスタに流れる電流が所定時間以上にわたって所定値を超えた場合に高音過電流検出信号を発生する高音過電流検出手段と、前記高音過電流検出信号が発生されると前記プリアンプの通過周波数帯域を低くさせる通過周波数帯域切替手段とを設けた。

(もっと読む)

プリエンファシス電圧ジッターを減少させる装置および方法

【課題】データ送信における電圧ジッターを減少させる送信器回路を提供すること。

【解決手段】第一の電流源と、該第一の電流源と第一のノードとの間に結合されている第一のフィルタと、該第一の電流源と第二のノードとの間に結合されている第二のフィルタと、第二の電流源と、該第二の電流源と第三のノードとの間に結合されている第三のフィルタと、該第二の電流源と第四のノードとの間に結合されている第四のフィルタと、該第一のノード、該第二のノード、該第三のノードおよび該第四のノードに結合されているドライバースイッチ回路などを含む、送信器回路。

(もっと読む)

出力バッファ回路及び入出力バッファ回路

【課題】流入電流の発生を抑制することができる出力バッファ回路を提供する。

【解決手段】出力バッファ回路1は、第1の高電位電源VDD1レベル又は低電位電源VSSレベルの出力信号OUT1を出力する第1出力回路10と、第1出力回路10とワイヤードオア接続され、第1の高電位電源VDD1よりも低電位である第2の高電位電源VDD2レベル又は低電位電源VSSレベルの出力信号OUT2を出力する第2出力回路20とを有している。また、出力バッファ回路1は、第1の高電位電源VDD1及び第2の高電位電源VDD2のうち第2の高電位電源VDD2のみが投入される場合に、第1出力回路10の高電位側の第1出力トランジスタT16及び第2出力回路20の高電位側の第2出力トランジスタT26の少なくとも一方のトランジスタのゲート電圧及びバックゲート電圧を第2の高電位電源VDD2レベルに設定する制御回路50を有している。

(もっと読む)

クロック生成回路および撮像装置

【課題】シュミットトリガー回路と同様な機能を有し、シュミットトリガー回路と比較して貫通電流を低減する。

【解決手段】インバータ回路INV1は、前段回路の回路閾値よりも低い第1の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第1の回路閾値に応じた第1の出力信号を出力する。インバータ回路INV2は、前段回路の回路閾値よりも高い第2の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第2の回路閾値に応じた第2の出力信号を出力する。スイッチ回路SWは、第1の出力信号および第2の出力信号が入力され、第1の出力信号および第2の出力信号の論理状態が、異なる状態から同じ状態に変化したときに、異なる論理状態に対応した第1の電圧および第2の電圧のいずれか一方を出力クロックとして出力する。

(もっと読む)

半導体装置

【課題】電源制御領域を電源遮断状態から電源供給状態に切り換えた際に生じる突入電流と電源ノイズを低減した半導体装置を提供する。

【解決手段】第1、第2のスイッチセルSWa、SWbと、を有し、第1のスイッチセルSWaは、制御信号CNTに応じてグローバル電源配線GVDDからローカル電源配線LVDDへの電源電圧の供給を開始する第1のスイッチトランジスタ11と、制御信号CNTを伝達する第1の信号伝達部と、を有し、第2のスイッチセルSWbは、制御信号CNTの論理レベルに応じてグローバル電源配線GVDDからローカル電源配線LVDDへの電源電圧の供給を開始する第2のスイッチトランジスタ21と、ローカル電源配線LVDDの電圧値が閾値電圧に達するまでの期間、制御信号CNTの後段回路への伝達を遮断する第2の信号伝達部と、を有する。

(もっと読む)

スイッチング回路

【課題】スイッチング回路のデッドタイム制御における電力効率を向上させる。

【解決手段】スイッチング制御部2は、パルス信号Aがロウレベルの時に、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち上がったのを検出してから、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち上がるように、スイッチング部Wを制御し、パルス信号Aがハイレベルの時に、Nチャンネル電界効果トランジスタM4のドレイン電位G2が立ち下がったのを検出してから、Pチャンネル電界効果トランジスタM3のドレイン電位G1が立ち下がるように、スイッチング部Wを制御する。

(もっと読む)

集積回路装置

【課題】被電源遮断回路の十分な安定化容量を確保しつつ、総回路面積の低減を図る。

【解決手段】高電位電源線VDDと低電位電源線VSSとの間に設けられ、各々が電源遮断スイッチPSW1, PSW2と直列に接続された複数段の被電源遮断回路CC1, CC2を含む集積回路装置であって、奇数段の前記被電源遮断回路CC1と直列に接続された前記電源遮断スイッチPSW1は、第1導電型の第1MOSトランジスタであり、偶数段の前記被電源遮断回路CC2と直列に接続された前記電源遮断スイッチPSW2は、前記第1導電型とは異なる第2導電型の第2MOSトランジスタであり、前記偶数段の前記第2MOSトランジスタPSW2のゲートが、当該偶数段の前段の奇数段における前記第1MOSトランジスタと前記被電源遮断回路の第1電源端子との接続ノードN1に接続される。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

出力バッファー回路

【課題】出力バッファーの面積・体積・部品点数の増加を抑制するとともに、ドライブ能力を向上させることが可能な出力バッファー回路を提供する。

【解決手段】第一駆動信号LINを伝達する第一入力経路4a、第二駆動信号RINを伝達する第二入力経路4b、第一入力経路4aと対応する第一出力バッファー6a及び第二入力経路4bと対応する第二出力バッファー6bを備える出力バッファー回路1において、入力経路切り替え手段8が、ステレオモード及びモノラルモードのうち、モノラルモードでは、第一入力経路4aと第一出力バッファー6a及び第二出力バッファー6bとを電気的に接続させ、出力経路切り替え手段10が、第一出力バッファー6a及び第二出力バッファー6bと、第一入力経路4a及び第一出力バッファー6aと対応する第一負荷2aとを、電気的に接続させる。

(もっと読む)

41 - 60 / 940

[ Back to top ]