Fターム[5J056EE06]の内容

Fターム[5J056EE06]に分類される特許

121 - 140 / 803

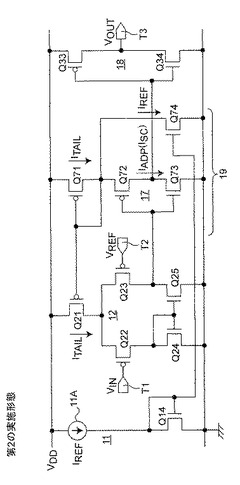

コンパレータ回路

【課題】低消費電力動作を実現しつつ信号処理に向けた論理判定時間を格段に削減することができる。

【解決手段】入力電圧と参照電圧とを比較して論理判定結果の出力電圧を発生して差動増幅器を含むコンパレータ回路において、微小電流であるバイアス電流を発生して差動増幅器に供給する電流源と、差動増幅器からの差動電圧を反転して反転信号を出力する第1のインバータ回路と、電流源のバイアス電流を検出し、第1のインバータ回路の貫通電流を検出し、検出したバイアス電流及び検出した貫通電流に基づいて、差動増幅器が論理判定を行わない期間はバイアス電流で差動増幅器を動作させる一方、差動増幅器が論理判定する期間はバイアス電流を増加させてなる適応バイアス電流を用いて差動増幅器を動作させるように適応バイアス電流制御を行うための適応バイアス電流を発生して差動増幅器に供給する適応バイアス電流生成回路とを備える。

(もっと読む)

半導体装置及び電子機器

【課題】消費電力を低減することができる半導体装置及びそれを用いた電子機器を提供す

ることを課題とする。

【解決手段】本発明の半導体装置は、高電位電源から第1の電位が供給され、低電位電源

から第2の電位が供給され、入力ノードに第1の信号が入力されると、出力ノードから第

2の信号を出力する。本発明の半導体装置は、第2の信号の電位差を、第1の電位と第2

の電位の電位差よりも小さくすることにより、配線の充電と放電に伴う消費電力を低減す

ることができる。

(もっと読む)

プログラマブル論理集積回路

【課題】 異なったLVTTL I/O規格に対して互換性を持つように集積回路の各I/Oを個別に再構成する回路を提供する。

【解決手段】 上述課題は1つのI/O電源電圧のみを用いて達成でき、この電圧は特定の用途に要求されるI/O電圧のうち最も高いものである。回路はI/Oセルの出力電圧を、適合されるべきLVTTL規格のVOHよりも高く最高VIHよりも低くなるように調節することによって動作する。I/Oセルは、I/O電源電圧とパッドの間に接続されるプルアップトランジスタと、該パッドの電圧と対応の規格に応じた基準電圧とを差動増幅する差動増幅器と、差動増幅器の出力信号と出力制御信号とにプルアップトランジスタを選択的にオン状態とするロジックゲートを備える。各I/Oセルは別個に再構成可能であるため、任意のI/Oを任意のLVTTL仕様に適合させることができる。

(もっと読む)

多値記憶手段、多値バッファ手段および双方向性スイッチング手段

【課題】C・MOS・FET等の相補型3端子スイッチング手段を用いたオン・オフ駆動手段も使用できる双方向性スイッチング手段を提供する。

【解決手段】どちらも両主電極の役割がその印加電圧の方向により互いに入れ換わることができ、どちらも互いに相補関係に有る2つのオン・オフ制御スイッチング手段が有って、その両オン・オフ制御スイッチング手段のうち一方の主電極と他方の主電極を接続し、一方の開放された主電極と一方の制御電極の間に一方のオン・オフ駆動手段を設け、一方の開放された主電極と他方の制御電極の間に他方のオン・オフ駆動手段を設け、その両オン・オフ制御スイッチング手段の直列回路を双方向性のスイッチとして使用する。

(もっと読む)

バッファリング回路および増幅回路

【課題】 回路のダイナミックレンジを圧迫しないと共に、チップサイズの増大を抑制することができるバッファリング回路及び増幅回路を提供する。

【解決手段】 入力端子及び出力端子を有するバッファリング回路でドレインが第1電圧ラインに接続され、ソースが前記出力端子に接続され、ゲートが前記入力端子に接続された第1プルアップドライバと、ソースが前記出力端子に接続され、ゲートが前記入力端子に接続された第2プルアップドライバと、前記第2プルアップドライバのドレインに定電流を供給する定電流回路と、前記出力端子と第2電圧ラインとの間に配置されたプルダウンドライバとを備え、前記プルダウンドライバは、前記定電流回路の定電流から前記第2プルアップドライバに流れる電流を減じた差電流に基づいた電流を流すように構成されている。

(もっと読む)

半導体集積回路

【課題】 ゲート酸化膜の信頼性を維持しながら、待機時のリーク電流を抑制でき、回路面積の増加を最小限にでき、欠陥を確実に検出することができる半導体集積回路を実現する。

【解決手段】 論理回路10と電源電圧Vddの供給端子との間にスイッチング回路20を設ける。動作時に、スイッチング回路20のトランジスタMP0のゲートに0Vの電圧を印加し、チャネル領域に電源電圧Vddと同じかまたは僅かに低いバイアス電圧VBを印加することで、トランジスタMP0のしきい値電圧を低くし、その電流駆動能力を大きくする。待機時にトランジスタMP0のゲートに電源電圧Vddと同じ電圧を印加し、ソースに電源電圧より低い電圧を印可し、チャネル領域に電源電圧Vddと同じかまたはそれより高いバルクバイアス電圧VBを印加し、トランジスタMP0のドレイン電流を最少化することにより、論理回路10の電流経路を遮断し、リーク電流の発生を抑制する。

(もっと読む)

レベル変換回路

【課題】第1及び第2入力信号の電圧レベルが変化する範囲に拘わらず、常時、適切なレベルで振幅する出力信号を出力することが可能なレベル変換回路を提供する。

【解決手段】N型トランジスタ21、22を入力差動対として有し、外部から入力される第1及び第2入力信号IN1、IN2をN型トランジスタ21、22のゲートに受ける第1差動増幅部2と、P型トランジスタ31、32を入力差動対として有し、第1及び第2入力信号IN1、IN2をP型トランジスタ31、32のゲートに受ける第2差動増幅部3と、第1及び第2入力信号IN1、IN2の電圧レベルを所定の基準電位VREFと比較し、各々の電圧レベルが基準電位VREFよりも高いか否かを判定する入力判定部4と、入力判定部4の判定結果に応じて第1及び第2差動増幅部2、3のいずれか一方の出力を選択する出力選択部5とを備えたレベル変換回路1。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

出力ドライバ回路

【課題】通信速度の高速化に加えて、消費電力の低減や、あるいは伝送波形品質の向上が図れる出力ドライバ回路を提供する。

【解決手段】例えば、正極および負極出力ノード(TXP,TXN)を電圧で駆動する電圧信号生成回路ブロックVSG_BKと、データ入力信号DIN_P,DIN_Nの遷移を受けてパルス信号を生成するパルス信号生成回路PGEN1,PGEN2と、当該パルス信号のパルス幅の期間でTXP,TXNを電流で駆動する電流信号生成回路ブロックISG_BKp1,ISG_BKn1を備える。電流信号生成回路ブロックは、TXP,TXNの寄生容量(Cp1,Cp2)を高速に充電すると共に、パルス幅に応じたプリエンファシスを行う。VSG_BKは、TXP,TXNにおける定常状態の電圧レベルを定めると共に、TXP,TXNをインピーダンスZ0で終端する。

(もっと読む)

半導体集積装置、及びその調整方法、並びに終端抵抗調整回路

【課題】第1の伝送路及び第2の伝送路間のDuty比の高精度化を実現できる終端抵抗調整回路、及び半導体集積回路を提供する。

【解決手段】本発明に係る終端抵抗調整回路71は、差動入力信号の第1及び第2の伝送路21、22それぞれに挿入され、制御信号に応じて抵抗値が調整される終端抵抗郡1,2と、第1及び第2の伝送路21、22の内、少なくともいずれかの伝送路であって、終端抵抗郡1,2の後段に挿入され、終端抵抗郡1、2を介して接続する伝送路の電位の調整を行う可変抵抗郡3と、可変抵抗郡3の後段、若しくは、当該可変抵抗郡3が配設されていない場合には終端抵抗郡1,2の後段に挿入され、第1及び第2の伝送路21、22の電位差を比較する比較器4と、比較結果に基づいて可変抵抗郡3の抵抗値を制御することによって伝送路の電位を調整する伝送路電位調整部5と、を備える。

(もっと読む)

半導体メモリのデータ出力回路及びその制御方法

【課題】カップリングノイズを減少させることができる半導体メモリのデータ出力回路およびその制御方法を提供すること。

【解決手段】複数のグローバルラインと、複数のデータを互いに異なるタイミングで複数のグローバルラインに出力するように構成されたセンスアンプブロックと、複数のグローバルラインを介して伝送された複数のデータを互いに異なるタイミングでラッチするように構成されたパイプラッチブロックと、アドレス信号を用いてセンスアンプブロックの出力タイミングとパイプラッチブロックのラッチタイミングとを制御するように構成された制御部とを備えることを特徴とする。

(もっと読む)

レベルシフタ回路及び半導体装置

【課題】電源電圧の低電圧化に対応可能とし高速化を実現するレベルシフタ回路の提供。

【解決手段】第1の電源と基準電源に対応した振幅の入力信号に応答してオン・オフが制御される第1のトランジスタと、入力信号の相補信号に応答してオン・オフが制御される第2のトランジスタと、縦積み接続された第3、第4、第5、第6のトランジスタと、を備え、第1及び第2のトランジスタは第1導電型で、第3乃至第6のトランジスタは第2導電型で、第1、第3、第5のトランジスタは、基準電源と、第1の電源電圧と異なる電圧の第2の電源との間に接続され、第2、第4、第6のトランジスタは、基準電源と、第2の電源との間に接続され、第1のノードは、第4トランジスタの入力端子と第5のトランジスタの入力端子に共通に接続され、第2のノードは、第3トランジスタの入力端子と第6のトランジスタの入力端子に共通に接続する。

(もっと読む)

電気光学装置、シフトレジスタ回路および半導体装置

【課題】ゲート線駆動回路の領域を効率よく利用できると共に、ゲート線選択信号の立ち上がり速度の低下(立ち上がり遅延)を防止できる電気光学装置、並びに、それに適した単一導電型のトランジスタで構成されたシフトレジスタ回路を提供する。

【解決手段】ゲート線駆動回路30は、複数のゲート線GLの奇数行を駆動する奇数ドライバ30aと、偶数行を駆動する偶数ドライバ30bとから成る。奇数および偶数ドライバ30a,30bの単位シフトレジスタSRの各々は、2行前の選択信号Gk-2を受け、その2水平期間遅れて自己の選択信号Gkを活性化させる。偶数ドライバ30bのスタートパルスSP1は、奇数ドライバ30aのスタートパルスSP2よりも1水平期間だけ位相が遅れている。

(もっと読む)

レベルシフト回路

【課題】バッテリの電源投入時等の電源電圧の急激なオーバーシュートに対する耐性を向上させるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、バッテリからの高電圧レベルの入力信号VINを入力するレベルシフト部10と、レベルシフト部10の中間信号Vmを一定以下に制限するクランプ部20と、中間信号をより低電圧のCMOSレベルで出力する出力バッファ部30とを備える。出力バッファ部30の初段においてpMOSトランジスタ31の負荷を抵抗32とすることにより、電源電圧のオーバーシュートに対する耐性を向上させる。

(もっと読む)

差動論理回路、分周回路、及び周波数シンセサイザ

【課題】動作電流を変えても直流出力電圧の変わらない差動論理回路及び分周回路、さらには、周波数シンセサイザにおける動作電流の調整方法を提供する。

【解決手段】複数対の差動論理信号を入力し論理演算を行ってその結果を一対の差動信号出力端子から出力する差動論理部と、差動論理部に電流を供給する電流源回路であって前記電流の大きさが制御可能な電流源回路と、差動信号出力端子に接続された負荷回路と、負荷回路に接続され、一対の差動信号出力端子の直流出力電圧が一定の電圧になるように負荷回路の負荷を制御する負荷制御回路と、を備える。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

レベルシフト回路

【課題】消費電力低下および速度向上が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路2は、第1入力端子11、第2入力端子12、第1出力端子21、第2出力端子22、第1PMOSトランジスタ31、第2PMOSトランジスタ32、第1NMOSトランジスタ41、第2NMOSトランジスタ42、第1ブートストラップ回路51および第2ブートストラップ回路52を備える。第1ブートストラップ回路51は、第1充電用スイッチ511,第1転送用スイッチ512,第1容量部513および第1インバータ回路514を含む。第2ブートストラップ回路52は、第2充電用スイッチ521,第2転送用スイッチ522,第2容量部523および第2インバータ回路524を含む。

(もっと読む)

PLD回路、集積回路装置及び電子機器

【課題】消費電力を低減できるPLD回路、集積回路装置及び電子機器等を提供すること。

【解決手段】PLD回路は、各トランジスター列が直列接続されたプログラマブルな複数のトランジスターを有する第1〜第m(mは2以上の整数)のトランジスター列TA1〜TAmを含む。第1〜第mのトランジスター列TA1〜TAmの一端に第1の非直流電源VS1が供給される。第1〜第mのトランジスター列TA1〜TAmの各トランジスター列は、複数の入力信号XP(X1P〜XiP)、XN(X1N〜XiN)によってオン・オフされる。第1の非直流電源VS1の電圧により規定される第1のホールド期間に、第1〜第mのトランジスター列TA1〜TAmの他端のノードである第1〜第mのノードNA1〜NAmの電圧レベルを各々出力する。

(もっと読む)

半導体スイッチ及び無線機器

【課題】オフ歪みを低減した半導体スイッチを提供する。

【解決手段】負の第1の電位を生成する電圧生成回路と、外部から入力される端子切替信号に応じて前記第1の電位を変化させる電圧制御回路と、電源電圧または電源電圧よりも高い正の第2の電位と前記第1の電位とが供給され、前記端子切替信号を入力し前記端子切替信号に基づいて前記第1の電位及び前記第2の電位の少なくとも一方を出力する駆動回路と、SOI基板に設けられ、前記駆動回路の出力により端子間の接続を切り替えるスイッチ部と、を備えたことを特徴とする半導体スイッチが提供される。

(もっと読む)

レベルシフト回路

【課題】レベル変換における動作範囲を広くする。

【解決手段】第1の電位(VDD1)の波高値を有する入力パルス信号(VIN)を入力するCMOSインバータ回路(P1、N1)と、第1の電位よりも高電位となる第2の電位(VDD2)の電源で動作し、一端(ND1)をCMOSインバータ回路の出力端に接続し、他端から第2の電位の波高値を有し入力パルス信号と同相の出力パルス信号(VOUT)を出力するラッチ回路(INV1、P3)と、第1の電位以上かつ第2の電位未満の電源供給をCMOSインバータ回路に対して行う電源供給回路(P2、INV2)と、を備え、電源供給回路は、入力パルス信号が少なくとも接地レベルとなる場合に電源供給を制限するように機能する。

(もっと読む)

121 - 140 / 803

[ Back to top ]