Fターム[5J106AA04]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583) | PLL(位相同期ループ回路) (1,412)

Fターム[5J106AA04]の下位に属するFターム

デジタルPLL (213)

Fターム[5J106AA04]に分類される特許

21 - 40 / 1,199

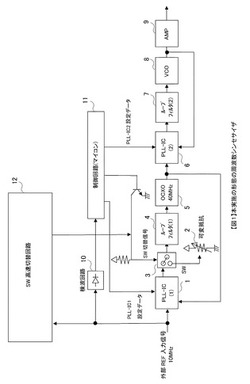

周波数シンセサイザ

【課題】 外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号「断」の場合には、SW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力し、スイッチ高速切替回路12が、外部基準入力信号の「断」を検出して制御回路11より高速にSW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力する周波数シンセサイザである。

(もっと読む)

アナログデジタル変換器及び無線受信機

【課題】アナログデジタル変換器のサンプリングクロックのジッタの影響を、低消費電力でデジタル補正する。

【解決手段】アナログデジタル変換器のサンプリングクロックを、サンプリングクロックよりも低周波数かつ低ジッタの基準クロックを源振とする位相同期ループ(PLL)により生成する。サンプリングクロックと基準クロックが同期するタイミングにおけるタイミング誤差を時間デジタル変換器(TDC)によりデジタル値に変換する。なお、基準クロックが存在しないサンプリングタイミングにおけるタイミング誤差については、検出されたタイミング誤差を補間して生成する。これにより、各サンプリングタイミングにおけるサンプリングクロックのジッタ値を取得する。当該ジッタ値からサンプリング電圧誤差を算出し、アナログデジタル変換器の出力をデジタル補正する。

(もっと読む)

情報処理システム

【課題】システムリセット時の起動時間を短縮可能な情報処理システムを提供する。

【解決手段】複数の機能モジュールの内の機能モジュール1では、システムリセット信号にてPLL回路10及び信号処理部12をリセットした後にPLL回路10へのリセットを解除する。リセット解除後にPLL回路10で生成された内部クロック信号がシステムクロック信号に位相ロックしていない場合には起動中を示す第1の起動状態信号を機能モジュール2に供給する。位相ロックしている場合には起動完了を示す第2の起動状態信号を機能モジュール2に供給すると共に信号処理部12へのリセットを解除する。機能モジュール2では、第1の起動状態信号にてPLL回路20及び信号処理部22をリセットする。そして、第2の起動状態信号にてPLL回路20へのリセットを解除し、リセット解除後に、位相ロックした時に信号処理部22へのリセットを解除する。

(もっと読む)

高周波信号処理装置および無線通信システム

【課題】ディジタル型PLL回路を備えた高周波信号処理装置および無線通信システムにおいて、スプリアスの影響を低減する。

【解決手段】例えば、ディジタル位相比較部DPFD、ディジタルロウパスフィルタDLPF、ディジタル制御発振部DCO、マルチモジュールドライバ部(分周部)MMDを備えたディジタル型PLL回路において、DLPFのクロック信号CKDLPFのクロック周波数が複数の選択肢の中から選択可能に構成される。当該クロック周波数は、基準発振信号Frefの整数倍の周波数の中から、DCOの発振出力信号RFdcoに対して規格上のどの周波数帯を設定するかに応じて選択される。

(もっと読む)

周波数調整回路、位相同期回路、通信装置及び記憶装置

【課題】帯域制限フィルタを含むPLLのロックアップ時間を短縮する。

【解決手段】実施形態によれば、周波数調整回路200は、レジスタ213と、デジタルアナログ変換器220と、帯域制限フィルタ250と、バッファアンプ240とを含む。レジスタ213は、第1の動作モードの終了時にデジタル制御コード12を保存し、第3の動作モードの開始時に出力する。第1の動作モードにおいて、制御電圧15を持つアナログ制御信号14が電圧制御発振器110の制御端子に供給される。第2の動作モードにおいて、アナログ制御信号14がバッファアンプ240に供給され、バッファアンプ240は帯域制限フィルタ250を駆動し、帯域制限フィルタ250は制御電圧15を生成する。第3の動作モードにおいて、アナログ制御信号14が帯域制限フィルタ250に供給され、帯域制限フィルタ250は制御電圧15を生成する。

(もっと読む)

発振回路およびそれを用いた電子機器

【課題】スペクトルのピークを抑制する。

【解決手段】発振回路2は、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。プログラマブル分周器18は、その分周比が少なくとも2値で切りかえ可能に構成され、出力クロック信号CKOUTを設定された分周比で分周し、分周クロック信号CKDIVを生成する。位相比較器10は、基準クロック信号CKREFと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。VCO(電圧制御発振器)14は、ループフィルタ12から出力される位相差信号S2に応じた周波数で発振し、出力クロック信号CKOUTを生成する。制御部20は、プログラマブル分周器18の分周比を、時分割的に切りかえることにより出力クロック信号CKOUTのスペクトルを拡散させる。

(もっと読む)

半導体装置

【課題】アナログ電圧を使用することなく、クロック信号を高精度且つ広範囲に遅延させる。

【解決手段】入力ノード110aと出力ノード110bとの間に直列接続された複数のワンショットパルス生成回路201〜20nを備える。ワンショットパルス生成回路201〜20nのそれぞれは、入力されたクロック信号の一方のエッジに応答して、ワンショットパルスを生成する。ワンショットパルスのパルス幅は、カウント値RCNTに基づいて可変である。これにより、カウント値RCNTを変化させることによって、ディレイライン110の遅延量を広範囲且つ高精度に変化させることが可能となる。しかも、アナログ電圧を使用しないことから、アナログ電圧の生成回路やその安定化回路などを設ける必要もなくなり、回路設計が容易となる。

(もっと読む)

周波数シンセサイザ

【課題】少数点逓倍の精度を向上させ、累積ジッタを低減した周波数シンセサイザを提供する。

【解決手段】位相比較器1と、チャージポンプ2と、ローパスフィルタ3と、電圧制御発振器4と、該電圧制御発振器の出力クロック信号を小数点分周して前記帰還クロック信号を生成する帰還回路とを備える。帰還回路は、電圧制御発振器4の出力クロック信号を分周する可変分周器5と、電圧制御発振器4の8相のクロック信号から1つの位相のクロック信号を選択するマルチプレクサ7と、マルチプレクサ7で選択した特定の位相のクロック信号により可変分周器5のクロック信号をリタイミングするリタイミング回路(DFF回路8,9とアンド回路10)とを備える。

(もっと読む)

クロック生成装置

【課題】 異なる複数の基準周波数に同期したクロックを生成でき、また、自走動作時に、ノイズの発生と消費電力を低減することができるクロック生成装置を提供する

【解決手段】 複数の外部基準クロックを入力可能とし、信号レベル検出回路24,25部が入力された外部基準信号の帯域毎にレベル検出し、マイクロコントローラ4が、検出された信号レベルに応じて、一つの外部基準信号のみが適正レベルであった場合に、自走制御信号によりクロック選択回路34の外部基準クロックの出力をイネーブルとし、選択制御信号により適正レベルであった外部基準クロックを選択させ、それ以外の場合には、自走制御信号によりクロック選択回路34の外部基準クロックの出力をディセーブルとすると共に、PLL−IC5をパワーダウンさせて、電圧制御発振器9に自走制御用直流電圧生成回路6からの電圧に基づいて自走発振を行わせるクロック生成装置としている。

(もっと読む)

発振装置

【課題】メモリの容量を抑えることができる発振装置を提供すること。

【解決手段】第1の発振回路の発振周波数をf1、基準温度における第1の発振回路の発振周波数をf1r、第2の発振回路の発振周波数をf2、基準温度における第2の発振回路の発振周波数をf2rとすると、f1とf1rとの差分に対応する値と、f2とf2rとの差分に対応する値と、の差分値に対応する差分対応値を求める周波数差検出部と、この周波数差検出部にて検出された前記差分対応値xに基づいて環境温度が基準温度と異なることに起因するf1の周波数補正値を取得する補正値取得部と、を備え、装置固有の除算係数をkとすると、前記補正値取得部は、x/kに相当する値であるXについてn次の多項式を演算することによりf1の周波数補正値を求める機能を備えるように装置を構成して、多項式の係数を小さくする。

(もっと読む)

位相周波数比較回路

【課題】雑音特性及び高速動作を維持しながら、消費電力を削減することができる位相周波数比較回路を得ることを目的とする。

【解決手段】出力バッファ回路3が、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力する。

(もっと読む)

遅延ロックループ/フェーズロックループにおける移相処理

【課題】

本開示は遅延ロックループ(DLL)及びフェーズロックループ(PLL)における移相処理に関する。

【解決手段】

DLLまたはPLLにおけるチャージポンプは、出力ノードに並列に接続されたキャパシタを備える。一次電流スイッチング回路は、ソース電流でキャパシタを充電し、シンク電流でキャパシタを放電する。補助ソース回路は、大きさの範囲を有する正の位相生成電流をソースする。正の移相生成電流の大きさは、少なくとも1つのソース選択信号により決定される。補助シンク回路は、大きさの範囲を有する負の移相生成電流をソースする。前記負の移相生成電流の大きさは、少なくとも1つのシンク選択信号により決定される。

(もっと読む)

PLL回路及びその制御方法

【課題】回路規模の増大を抑制しつつ、VCOの発振周波数を広い範囲で変化させることができるPLL回路及びその制御方法を提供すること。

【解決手段】本発明にかかるPLL回路1は、VCO11と、制御ロジック14と、位相比較器13と、を備える。VCO11は、両端の電位差に応じて容量値が変化する可変容量素子を有し、電位差に応じた発振周波数の出力信号を出力する。制御ロジック14は、可変容量素子の一端に所定の電圧を印加した状態で、基準信号と出力信号との周波数差に基づいて、当該可変容量素子の他端に印加する制御電圧Vtcを決定する。位相比較器13は、可変容量素子の他端の電圧を制御ロジック14により決定された制御電圧Vtcに固定した状態で、基準信号と出力信号との位相差に基づいて、可変容量素子の一端に印加する制御電圧Vtaを決定する。

(もっと読む)

無線受信機

【課題】PLLのループフィルタの帯域を大きくすることにより、局部発振器の位相雑音性能が大幅に改善し、隣接チャネル選択性能を改善する受信機を提供する。

【解決手段】受信信号と局部発振器から出力されるローカル信号とをミキサでミキシングし、生成された中間周波数(IF)信号をバンドパスフィルタで選択して復調する無線受信機において、局部発振器は、受信信号のチャネル周波数間隔のn倍(nは3以上の整数)の周波数間隔のローカル信号を切り替えて出力する構成であり、バンドパスフィルタは、受信信号の受信すべきチャネルによって通過帯域の中心周波数を切り替える構成である。

(もっと読む)

レベル調整装置

【課題】 基準発振器、VCO、位相比較器の純度が低くても位相雑音特性を良好にする。

【解決手段】 基準発振器28aが発振する基準周波数frefをBS放送波のチャンネル間隔とされる38.36MHzに設定する。そして、中間周波数を282.28(=7×38.36+13.76)MHzとした場合は、1049.48MHzのチャンネル周波数とされるBS−1チャンネルがアサインされるBS−IFレベル調整ユニット10では、局部発振器28の出力周波数foutが767.2MHzになり、分周器28eの分周数Nを20とすればよい。基準周波数frefを38.36MHzと高くすることができるため、局部発振器28の位相雑音特性が良好になる。

(もっと読む)

PLL回路

【課題】PLLのチャージポンプ回路からの出力電流ミスマッチにより、PLLの特性劣化に繋がるリファレンススプリアスが発生する問題がある。

【解決手段】基準信号とフィードバック信号との位相差に応じて第1、第2のパルス信号を出力する位相比較器と、第1の制御信号に応じて、前記第1、第2のパルス信号のパルス幅をそれぞれ調整した第3、第4のパルス信号を生成するパルス幅調整回路と、前記第3、第4のパルス信号に応じて出力電流を生成するチャージポンプと、前記チャージポンプの出力に接続され、電流を電圧に変換するループフィルタと、前記ループフィルタの変換した電圧を積分した検出結果を出力する検出回路と、前記検出結果に応じて、前記第1の制御信号を生成する制御回路と、を有するPLL回路。

(もっと読む)

クロック生成回路、クロック生成方法および半導体集積回路

【課題】占有面積や定常位相誤差の増大、並びに、クロックが安定するまでに長時間を要することなく、スペクトラム拡散クロックを生成してEMI対策を図る。

【解決手段】基準信号CK1を受け取って、立ち上がりエッジの傾き、または、立ち下がりエッジの傾き、または、立ち上がりエッジおよび立ち下がりエッジの傾きを、周期的に変化させた第1信号CK2を生成する第1回路4と、前記第1信号を受け取って、周期的に周波数が変化するクロックを生成する第2回路5と、を有する。

(もっと読む)

位相同期回路および位相同期回路を用いた半導体装置

【課題】スタンバイ状態からの復帰後、電圧制御発振器に入力される電圧信号が短時間で一定となる、消費電力の低減された位相同期回路を提供することを課題とする。

【解決手段】電圧制御発振器の入力端子とループフィルタを構成する容量素子の間に、酸化物半導体材料を用いて半導体層を形成したトランジスタを設け、通常動作状態の時には当該トランジスタをオン状態に、スタンバイ状態の時には当該トランジスタをオフ状態とする。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

発振器およびPLL回路

【課題】半導体集積回路上に小面積で形成でき、かつ、適切な周波数の発振信号を生成できる発振器と、これを用いたPLL回路を提供する。

【解決手段】発振器は、第1のノードと第2のノードと間に並列接続される抵抗と、反転増幅器と、半導体素子とを備える。前記半導体素子は、半導体基板と、前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、前記音響波伝播層上に形成され、前記第1のノードと電気的に接続される第1のコンタクトと、前記音響波伝播層上に前記第1のコンタクトとは離れて形成され、前記第2のノードと電気的に接続される第2のコンタクトと、を有する。前記第1のノードまたは前記第2のノードから発振信号を出力する。

(もっと読む)

21 - 40 / 1,199

[ Back to top ]