Fターム[5J106AA04]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583) | PLL(位相同期ループ回路) (1,412)

Fターム[5J106AA04]の下位に属するFターム

デジタルPLL (213)

Fターム[5J106AA04]に分類される特許

41 - 60 / 1,199

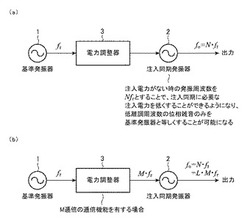

高周波発振源

【課題】位相雑音の劣化を抑制することができる高周波発振源を得ることを目的とする。

【解決手段】所定の周波数で発振する基準発振器1と、その基準発振器の出力波が注入されていない場合の発振周波数が、その基準発振器の出力波の周波数の整数倍に設定されている(または設定される)注入同期発振器とを備え、その基準発振器から注入同期発振器に注入される電力を、注入同期発振器の低離調周波数の位相雑音が基準発振器の位相雑音と(同じ周波数で比較した場合に)等しくなるように、かつ高離調周波数の位相雑音が注入電力がない時の注入同期発振器の位相雑音と(同じ周波数で比較した場合に)等しくなるように適切な注入電力とする電力調整手段を設ける。

(もっと読む)

位相比較回路

【課題】入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路を得る。

【解決手段】RF信号と基準信号との立ち上がりエッジを比較してアップ信号またはダウン信号を生成する位相比較コア回路1と、RF信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、RF信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前のRF信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成するマスク信号生成回路2と、位相比較コア回路1により生成されたアップ信号およびダウン信号を、マスク信号生成回路2により生成されたマスク制御信号MSK1に従いマスクする信号マスク回路3とを備えた。

(もっと読む)

クロック供給回路及び半導体集積回路

【課題】高速なクロックを内部回路に供給するためには、消費電力の高いクロックバッファを必要とする。そのため、高速なクロックを低消費電力で供給するクロック供給回路及び半導体集積回路が、望まれる。

【解決手段】クロック供給回路は、電圧制御発振器を含むPLL回路と、電圧制御発振器の発振周波数を制御する発振制御電圧に基づいて、電圧制御発振器の発振周波数と略同一の周波数を持つクロックを、PLL回路のリファレンスクロックに同期させて出力する自己発振型バッファ回路と、を備えている。

(もっと読む)

クロック生成装置、クロック生成方法及びプログラム

【課題】目的の周波数からずれた周波数のクロックをクロックの供給先に与える危険性の少ない、クロック生成装置を提供する。

【解決手段】各クロック供給部10,20に、水晶発振器であるVCXO11,21を目的の周波数で発振させるために設定された基準値と基準値が設定された時を示す設定時情報とを記憶するメモリ14,24と、VCXO11,21の生成するクロックを他のクロック供給部のVCXOの出力するクロックに同期させる同期手段とをそれぞれ備える。メモリ14,24の記憶内容に基づき、最も設定時情報が新しいVCXOを選別し、その選別したVCXOを基準値に基づいて発振させて目的の周波数のクロックを生成させる。他のVCXOには、選別したVCXOの生成したクロックに同期したクロックを生成させる。

(もっと読む)

発振器

【課題】PLL回路を有する発振器であって、小型化を図ることができる発振器を提供する。

【解決手段】発振器100は、基板110の上方に配置された第1MEMS振動子12を含み第1発振信号を出力する基準発振回路と、基板110の上方に配置された第2MEMS振動子52を含み制御信号で発振周波数が制御され第2発振信号を出力する電圧制御発振回路と、前記第2発振信号を分周して分周信号を出力する分周回路と、前記分周信号と前記第1発振信号との位相差に基づいた前記制御信号を出力する位相比較回路と、を含み、第1MEMS振動子12および第2MEMS振動子52の各々は、第1電極と、第2電極と、を有し、第2電極は、第1電極と対向配置された可動部を有し、基板の平面視において第1MEMS振動子12の可動部の面積は、第2MEMS振動子52の可動部の面積よりも大きい。

(もっと読む)

適応型受信システム、適応型送受信システム及び複数チャネル送受信システム

【課題】ロックポイント付近におけるサンプリングクロックの位相の調整と、イコライザ部の制御とを安定させ、ジッタトレランスを高める。

【解決手段】位相比較部は、サンプリングタイミングとサンプリングタイミングよりも第一の所定位相分前のタイミングとの間の第一区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LAG(n)を出力するとともに、サンプリングタイミングとサンプリングタイミングよりも第二の所定位相分後のタイミングとの間の第二区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LEAD(n)を出力する。判定部は、検出データパターンの各ビットに対応する位相比較信号LAG(n),LEAD(n)の出力パターンを所定の比較対象パターンと比較し、合致するか否かに基づいて、等化信号EQDATAの1ビットがサンプリングクロックCKの1周期よりも長いか短いかを判定する。

(もっと読む)

信号生成装置及び周波数シンセサイザ

【課題】PLLを用いた周波数シンセサイザにおいて、簡素な構成でありかつスプリアス特性が良好であること。

【解決手段】位相比較部に入力する参照周波数信号を、ディジタル信号からなる鋸波のゼロクロスポイントを検出したときのクロックに基づいて生成する。しかしこの場合ディジタル値が飛び飛びの値であることから正負の符号が逆転するときにディジタル値がゼロとなるとは限らない。そこで前記ディジタル値が徐々に変化する領域において正、負の符号が逆転するゼロクロス時の直前のディジタル値及び直後のディジタル値を読み出したクロック信号を夫々P1及びP2とし、クロック信号P2の次のタイミングのクロック信号をP3とすると、P1とP2で読み出されるディジタル値の比率に対応する比率でP1、P3を使用する。

(もっと読む)

PLL回路

【課題】サイクルスリップが発生することでPLL回路の引き込み時間が遅れるという問題がある。そのため、サイクルスリップを低減し、高速にロックを行なうPLL回路の提供が望まれる。

【解決手段】図1に示すPLL回路は、位相比較器と、位相比較器と接続されるチャージポンプと、を備えている。さらに、位相比較器は、基準クロックを遅延させたクロック及びフィードバッククロックを遅延させたクロックに基づき、チャージポンプの出力電圧を上昇させる第1のUP信号及びチャージポンプの出力電圧を下降させる第1のDW信号を生成する制御信号生成回路と、基準クロックに同期させ、第1のUP信号に基づきチャージポンプの出力電圧を上昇させる第2のUP信号を出力する第1の保持回路と、フィードバッククロックに同期させ、第1のDW信号に基づきチャージポンプの出力電圧を下降させる第2のDW信号を出力する第2の保持回路と、を含んでいる。

(もっと読む)

位相同期装置および位相同期回路の周波数キャリブレーション方法、並びにプログラム

【課題】アナログ特性を容易な設計で高速なデジタルアシストが可能な位相同期装置および位相同期回路の周波数キャリブレーション方法、並びにプログラムを提供する。

【解決手段】デジタルアシストキャリブレーション回路は、探索範囲を所定の値から順番に検索値を変更して、検索値と目的値との大小関係を確認する順次探索と、探索範囲の検索値の中央値と上記目的値との大小関係を確認し、目的値が含まれる側の半分の検索範囲に対してのみその半分の検索範囲の検索値の中央値と目的値との大小関係を確認して、目的値を検索していく二分探索と、を選択的に処理可能で、検索過程における最初の過程と最後の過程のうち、少なくとも最初の過程と最後の過程のいずれかにおいて二分探索を行い、残りの過程では順次探索処理を行う。

(もっと読む)

半導体集積回路およびその動作方法

【課題】ループフィルタをオンチップ化する際、トランジスタの素子サイズのバラツキによるPLL回路の特性バラツキを軽減して、回路規模と消費電力の増大を軽減する。

【解決手段】半導体集積回路は、位相周波数比較器1とループアッテネータ2とチャージポンプ3とループフィルタ4と電圧制御発振器5と分周器6を具備するフェーズロックドループ回路を内蔵する。アッテネータ2は、サンプリング回路21とカウンタ22とを含む。回路21にサンプリングパルスSPL_CLKと位相周波数比較器1から出力される第1と第2の出力信号が供給され、回路21はサンプリング出力信号を出力する。カウンタ22は回路21から出力される所定個数のサンプリングパルスのカウントアップを完了すると、カウントアップ完了出力信号を出力する。チャージポンプ3は、カウントアップ完了出力信号に応答してループフィルタ4に充電電流または放電電流を出力する。

(もっと読む)

PLL回路

【課題】短時間でかつ正確に、所望の周波数の発振信号にロック可能なPLL回路を提供する。

【解決手段】PLL回路は、粗調整ループ部と微調整ループ部を有する。前記粗調整ループ部は、前記複数の第1切替部の切替情報を記憶する切替情報記憶部と、複数の第1切替部の新たな切替情報を設定する切替情報設定部と、切替情報設定部で設定した複数の第1切替部の切替情報に基づいて調整した電圧制御型発振器の発振信号を分周した分周信号を生成する分周器と、分周信号の周波数と基準信号の周波数とを比較した結果に基づいて、切替情報設定部に対して切替情報の再設定を指示する発振周波数調整部と、切替情報設定部で設定した切替情報と、切替情報記憶部に記憶されている切替情報と、の差分情報を生成し、該差分情報が所定の閾値範囲内であれば、ループ制御部に粗調整の終了を報知し、差分情報が閾値範囲外の場合には、切替情報設定部に対して切替情報の再設定を指示する比較器と、を有する。

(もっと読む)

PLL周波数シンセサイザ

【課題】 フラクショナルN方式のPLL(Phase-locked loop;位相同期回路)周波数シンセサイザにおいて生じる、フラクショナルスプリアスを抑圧する。

【解決手段】 可変分周器の分周数を2つ以上の整数値で時間的に切り替えるフラクショナルN方式のPLL周波数シンセサイザにおいて、電圧制御発振器2とループフィルタ7の間に、抑圧周波数および減衰量の制御を可能とする可変ノッチフィルタ8を設けることで、フラクショナルスプリアスを抑圧することができる。

(もっと読む)

位相同期回路およびその制御方法

【課題】ばらつき条件(温度、電源電圧、経年変化等)下の安定動作を補償しかつ低ゲインの電圧−周波数特性を実現できる位相同期回路を提供する。

【解決手段】バラクタアレイを有するVCO101と、VCO101の特性をモニターするモニター回路102と、モニター結果に応じてバラクタアレイに供給するオフセット量を切り替えるオフセット発生回路103とを備える。ばらつき条件下のVCOの特性をモニターした結果からバラクタアレイのオフセット量を調整することで、位相同期回路の動作不良を防ぐ。

(もっと読む)

フラクショナルPLL回路

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を提供する。

【解決手段】フラクショナルPLL回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた移相量で変化させるように、位相選択回路6によって選択される移相クロック信号pi_outの立ち上がりエッジの位相を決定し、決定された位相を選択するように位相選択回路6を制御する。

(もっと読む)

サンプリングクロック生成回路、画像読取装置及び電子機器

【課題】アパーチャディレイをより小さくするアパーチャディレイ調整機能を有するサンプリングクロック生成回路を提供する。

【解決手段】SSCG11からの出力クロック信号に対して所定の遅延量だけ遅延してサンプリングクロック信号を発生してサンプリングホールド回路に供給する、遅延回路21,22及びクロック発生器23からなるサンプリングクロック生成手段と、SSCG11の出力クロック信号に基づいて生成されたCCD駆動クロック信号と、上記サンプリングクロック信号とを位相比較して位相比較結果を出力する遅延型フリップフロップ24と、上記位相比較結果に基づいて、上記駆動クロック信号と上記サンプリングクロック信号との位相差が実質的にゼロとなるように上記サンプリングクロック生成手段の遅延量を制御する制御ロジック回路20とを備えた。

(もっと読む)

多周波発振器

【課題】発振周波数の安定性及び周波数の過渡応答性において従来よりも優れた多周波発振器を提供する。

【解決手段】水晶振動子を少なくとも備え、変調信号発生器5から入力された変調信号によって水晶振動子の発振周波数を調整する基準信号発生器12と、位相比較器6、ループフィルタ7及び電圧制御発振器8を少なくとも備え、基準信号発生器11の出力と電圧制御発振器8の出力とを位相比較器6で位相比較するPLL11とを具備する。

(もっと読む)

クロック生成回路

【課題】従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供する。

【解決手段】基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えた。

(もっと読む)

VCO利得補償及び位相ノイズ低減のためのプログラマブルバラクタ

【課題】電圧制御発振器の制御利得を発振周波数に対して比較的一定に維持し、位相ノイズを低減したプログラマブルバラクタ装置を提供する。

【解決手段】プログラマブルバラクタ装置100は、複数のデジタルバラクタビットB0、B1、B2によって制御される複数のバイナリ重み付けバラクタ104,106,108を含み得る。プログラマブルバラクタ装置は、複数のバイナリ重み付けバラクタと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとする制御とを含み得る。プログラマブルバラクタ装置の実効容量を変化させる方法は、複数のバイナリ重み付けバラクタを設けることと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとすることとを含み得る。

(もっと読む)

電流−モード利得分割デュアル−パスVCO

【課題】大きな電圧制御オシレータ(VCO)利得を効率的に取り扱うための技術の提供。

【解決手段】VCOの中心周波数を調節する平均制御電流を供給するための低速高利得パス、及び通常動作の間VCO周波数を調節する瞬間的な制御電流を供給するための高速低利得パス、を利用する。1つのデザインでは、VCOは、電圧−電流コンバータ252、電流増幅器254、総和器256、及び電流制御オシレータ(ICO)260を含む。電圧−電流コンバータは、制御電圧VCTRLを受け取り、そして第1電流I1と第2電流I2とを発生する。電流増幅器は、第1電流を増幅しそしてフィルタし、そして第3電流I3を発生する。総和器は、第2電流と第3電流を合算し、そして制御電流を発生する。ICOは、制御電流CTRLを受け取り、そして制御電流により決定される周波数を有するオシレータ信号を発生する。

(もっと読む)

周波数追尾装置

【課題】異なるコヒーレント加算時間で算出した積算パワーの平方根の差分によって周波数ずれ量を算出することで、高精度な周波数ずれ量を算出する。

【解決手段】 所望の衛星信号yを加算時間MAでコヒーレント加算し、NA回ノンコヒーレント加算をして、積算パワー|yA|2を算出する積算器17と、衛星信号yを加算時間MAと異なる加算時間MBでコヒーレント加算し、NB回ノンコヒーレント加算をして、積算パワー|yB|2を算出する積算器18と、積算器17によって算出される積算パワーの平方根|yA|と、積算器18によって算出される積算パワーの平方根|yB|との差分から、周波数ずれ量Δf2を算出する周波数ずれ演算器20と、を備え、周波数ずれ演算器20で算出された周波数ずれ量Δf2に基づいて、所望の衛星信号yを追尾する。

(もっと読む)

41 - 60 / 1,199

[ Back to top ]