Fターム[5J106CC21]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788)

Fターム[5J106CC21]の下位に属するFターム

Fターム[5J106CC21]に分類される特許

141 - 160 / 1,193

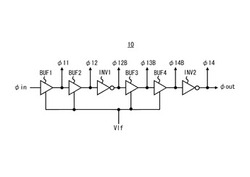

DLL回路

【課題】従来のDLL回路では、クロック信号の立ち上がりエッジと立ち下がりエッジとで遅延時間に差が生じる問題があった。

【解決手段】本発明のDLL回路は、入力クロック信号φinに制御電圧Vlfに応じた遅延量を与える遅延バッファBUF1〜BUF4と、入力クロック信号φinを反転させるインバータとINV1、INV2、を含み、入力クロック信号φinを遅延させた出力クロック信号φoutを生成するディレイライン10と、入力クロック信号φinと前記出力クロック信号φoutとの位相差に基づいて制御電圧Vlfを生成する制御電圧生成部とを有し、ディレイライン10は、インバータINV1と遅延バッファBUF1、BUF2とを含む第1の遅延部と、第1の遅延部の後段に設けられ、第1の遅延部と同数のインバータ及び遅延バッファ(INV2、BUF3、BUF4)を含む第2の遅延部と、を有する。

(もっと読む)

位相同期回路

【課題】位相同期回路においてロックアップを高速化する。

【解決手段】位相同期回路100は、基準信号の周波数にXを乗じて得られる出力周波数を有し、基準信号源180と、電圧制御発振器110と、位相比較器120と、第1チャージポンプ130と、ループフィルタ150と、カウンタ161と、第2チャージポンプ170と、制御回路164とを備える。電圧制御発振器110は、第1信号、および逆相の第2信号を生成する。スイッチ140は、第1チャージポンプ130で生成された電流信号をループフィルタ150に供給する。カウンタ161は、基準信号の1周期期間に含まれる、第2信号のサイクル数をカウントする。第2チャージポンプ170は、互いに反対符号の第1電流信号と第2電流信号をループフィルタ150に供給可能である。制御回路164は、サイクル数とXの値との比較に基づき、スイッチ140および第2チャージポンプ170を制御する。

(もっと読む)

局部発振器

【課題】PVTに依存しない安定した位相雑音特性を短時間で得ることができる局部発振器を提供する。

【解決手段】局部発振器は、デジタル制御発振器と、位相データ生成器と、減算器と、ループフィルタと、乗算器と、係数算出器と、を備える。前記デジタル制御発振器は、第1の発振器制御値により発振信号の発振周波数を制御可能である。前記発振周波数は、前記第1の発振器制御値と、前記第1の発振器制御値の単位値あたりの前記発振周波数の変化量と、の積に等しい。設定周波数データは、設定周波数を基準信号の基準周波数で除算して得られる。前記乗算器は、前記ループフィルタからの規格化制御値に第1の係数を乗算した前記第1の発振器制御値を出力する。前記係数算出器は、前記発振周波数が前記設定周波数に略等しくなった時の前記第1の発振器制御値を、前記設定周波数データで除算し、その除算結果を新たな前記第1の係数として前記乗算器に設定する。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

分周回路及び集積回路

【課題】分周器の発振を防止する分周回路を提供する。

【解決手段】クロック信号Vcを所定の分周比にて分周する分周器20を備え、分周器の発振を防止する分周回路1であって、クロック信号のピーク電圧Vcpを検出してピーク値を保持するピーク検出器30と、分周器が正常動作するために必要なクロック信号の振幅vpに対応した参照電圧Vrefを出力する参照電圧発生器40と、ピーク検出器により検出されたピーク値と参照電圧とを比較する比較器50と、を備え、分周器に分周開始を指示する制御信号を入力する制御端子を備え、制御端子に比較器の出力信号Veを接続し、ピーク値が参照電圧を超えたときに、比較器は、分周器の制御端子に分周開始を指示する制御信号を出力する

(もっと読む)

クロック発生回路

【課題】 PLLを動作させた状態で、同期外れを起させず、入力クロックの切り替えおよびそれに伴う分周比の切り替えを行うことが可能なクロック発生回路を提供する。

【解決手段】 タイミング制御部8は、入力クロックを指定するクロック選択情報が切り替わった後、分周器1がリファレンスクロックCLKREFを出力するのに応じて、クロック選択指令SELCKを切り替える動作と、分周器1に1個のリファレンスクロックCLKREFを出力させるための入力クロックの個数Rと、分周器6に1個のフィードバッククロックCLKFBを出力させるための出力クロックCLKOの個数Fのうちの少なくとも一方の設定を切り替え、切り替え後の設定個数Rに対応した入力クロックの分周器1によるカウント動作および切り替え後の設定個数Fに対応した出力クロックの分周器6によるカウント動作の両方を開始させる。

(もっと読む)

信号処理回路

【課題】内部回路の内部クロックと内部回路の入力信号との位相関係により内部回路の出力が変動する場合であっても、安定した回路動作とすることができる信号処理回路を得る。

【解決手段】入力信号と位相制御信号とを受け、前記入力信号及び前記位相制御信号の位相差に基づき位相比較信号を出力する位相比較手段と、前記位相比較信号を受け、前記位相比較信号に基づく周波数で発振する発振信号を出力する発振手段と、前記発振信号を受け、前記位相制御信号を出力する位相制御信号発生手段とを備え、同時に前記位相制御信号を出力信号とし、該位相制御信号を内部クロックとして供給することを特徴とする位相差制御回路である信号処理回路等を提供する。

(もっと読む)

位相同期ループ回路

【課題】必要な特性を満たしつつ、回路構成を簡素化し、省面積化を可能とするデジタルPLLの提供。

【解決手段】リファレンスクロック信号FRと分周クロック信号FDの位相差を検出するTDC101、FDとFRの進み遅れを出力するFF103、位相誤差演算器102、位相誤差(PERR)を平滑化するデジタルフィルタ104、出力クロック信号FOを出力するDCO105、FOを分周したFDを出力するN分周器106、N分周器106内のカウンタ値をFRに応答してサンプルするレジスタ107を備え、TDC101は、位相差検出測定範囲がFOの1周期以内とされ、FRとFDの位相差をFOの1周期に換算した小数で出力し、位相誤差演算器102は、FDとFRの位相差が、FOの周期の整数倍以上のときは、レジスタ107出力と符号情報signから、FOの1周期内のときは、TDCの出力と符号情報signからPERRを演算出力する。

(もっと読む)

位相同期回路および無線通信装置

【課題】周波数補正ミスをなくせ、電圧対周波数変換利得Kvcoを低く抑えることが可能で、PLL位相ノイズ設計を緩和できる位相同期回路および無線通信装置を提供する。

【解決手段】キャリブレーション部190は、電圧制御発振器184の出力発振信号の周波数をカウントするカウンタ回路191と、カウンタ回路のカウント結果を保持しておくための第1および第2の記憶回路193,194と、カウンタ回路とターゲット周波数を比較し大小を判定する比較回路195と、比較回路の結果を受けカウンタ回路のカウント結果と第1の記憶回路の保持結果を比較し、電圧制御発振器の容量バンクを制御する制御回路106と、電圧制御発振器にキャリブレーション電圧を生成し与える電圧生成回路197と、カウンタ回路のカウント結果と第1および第2の記憶回路の結果より演算を行い、演算結果に応じて電圧生成回路を制御する処理回路198と、を含む。

(もっと読む)

クロックデータリカバリ回路

【課題】簡易な構成で、データおよびクロック間のタイミングスキューの制約をなくすとともに、データの周波数可変範囲を広くとることができるCDR回路を提供する。

【解決手段】CDR回路は、基準クロック信号を用いてクロック信号を所望の周波数にロックするLTモードと、クロック信号をデータ信号に位相同期させる通常動作モードとを有する。CDR回路は、VCOと、入力信号を平滑化して制御電圧を生成してVCOに出力するLPFと、LTモード時に、基準クロック信号とクロック信号との周波数比較を行ない、該比較結果に応じた信号をLPFに出力する周波数ループと、通常動作モード時に、データ信号とクロック信号との位相比較を行ない、該比較結果に応じた信号をLPFに出力する位相ループと、基準クロック信号の周波数カウント値に応じてVCOに設定する周波数レンジを調整する周波数検出回路とを備える。

(もっと読む)

半導体集積回路

【課題】チップサイズの大型化を防止することができる半導体集積回路。

【解決手段】同一のリセット信号が入力されることにより、互いに同期が取られる複数の送信ブロックを備える半導体集積回路。各送信ブロックは、基準クロック信号とフィードバッククロック信号との位相差に応じた制御電圧に基づいて周期Tの第1のクロック信号を発振する電圧制御発振器と、第1のクロック信号がN(Nは自然数)分周された第2のクロック信号が入力され、当該第2のクロック信号から、第1の送信用クロック信号と当該第1の送信用クロック信号よりも周波数の低い第2の送信用クロック信号とを生成し、リセット信号に応じて少なくとも第2の送信用クロック信号を出力するリセット機能付き分周器と、第1及び第2の送信用クロック信号が分配される複数の送信機と、を備える。

(もっと読む)

PLLシンセサイザ

【課題】温度補償ループフィルタのキャパシタの容量値を小さくする。

【解決手段】PLLシンセサイザは,位相比較器PDと,ループフィルタLFと,電圧制御発振器VCOとを有する。さらに,温度補償ループとして,周波数制御電圧が制御電圧範囲から外れたときに比較信号30を出力する比較器CMPと,比較信号30を積分してMビットの第1のデジタル信号32を生成するデジタルフィルタDFと,第1のデジタル信号32を入力し,前記Mビットより少ないNビットで、前記第1のデジタル信号32に対応する第2のデジタル信号34を生成するΣΔ変調器12、10と,第2のデジタル信号34を電流信号36に変換する温度補償チャージポンプCPtと,前記電流信号36を温度補償制御電圧に変換する温度補償ループフィルタTFとを有し,電圧制御発振器VCOは温度補償制御電圧ftに基づいて出力クロックCKoutの周波数を制御する。

(もっと読む)

多相信号を生成する方法及び回路

【課題】2つの結合されたLCVCOにおいて生じる多相クロック信号の位相誤差を改善し、制御可能な位相オフセットでクロック信号を生成する方法を提供する。

【解決手段】方法は、LCVCOによって第1のLCタンクの共振周波数に基づく第1の位相を有する第1の周期信号を生成するステップと、第2のLCVCOによって第2のLCタンクの共振周波数に基づく第2の位相を有する第2の周期信号を生成するステップと、第1及び第2の周期信号に基づいて第1及び第2のLCタンクの間の位相オフセットを決定するステップと、決定された位相オフセットに基づいて第1及び第2の出力信号を生成するステップと、所定の位相オフセットと略等しくなるよう位相オフセットを調整するステップとを有する。調整ステップは、第1の出力信号に基づいて第1のLCタンクの第1のインピーダンスを変調するステップ、及び/又は、第2の出力信号に基づいて第2のLCタンクの第2のインピーダンスを変調するステップを有する。

(もっと読む)

クロック生成回路および電子機器

【課題】クロック生成回路の回路規模を抑制しつつ、クロック信号の周波数スペクトルを好適に拡散する。

【解決手段】クロック生成回路1の電流制御発振部13は、供給される電流に応じた遅延量で信号を遅延する複数の電流制御遅延回路11を含む閉ループ12によりクロック信号を生成する。位相制御部15〜18は、クロック信号と基準信号とを比較する比較器15を有し、これらの信号の位相差を減らすように変化する制御電流を、複数の電流制御遅延回路11に供給する電流として出力する。拡散電流生成部19は、複数の電流制御遅延回路11の一部に対して、制御電流の替わりに、制御電流と異なる電流値のスペクトラム拡散電流を供給する。

(もっと読む)

PLL周波数シンセサイザ、無線通信装置およびPLL周波数シンセサイザの制御方法

【課題】安価な構成とするとともに、性能を向上させることができるPLL周波数シンセサイザ、無線通信装置およびPLL周波数シンセサイザの制御方法を提供する。

【解決手段】PLL周波数シンセサイザは、基準周波数信号と分周信号との位相を比較する位相比較部101からの信号と位相誤差補償信号とに応じて、電流パルス信号を生成するCPDAC102と、電流パルス信号を電圧信号に変換するループフィルタ103と、電圧信号に応じた発振周波数の信号を出力するVCO104と、VCO104からの出力を分周して分周信号として出力する分周器105と、分数分周のための分周比のデータに基づいて、分周比制御信号を生成するデルタシグマ変調器107および加算器106と、分周比のデータから少なくとも2つの位相誤差補償用のデータを生成し、生成したデータを異なるタイミングで利用して、位相誤差補償信号を生成する制御部108とを備える。

(もっと読む)

CDR回路、受信装置、および通信システム

【課題】簡易な回路構成で、高速かつジッタ入力に強く、信号エラーの発生を抑止することが可能なCDR回路、受信装置、および通信システムを提供する。

【解決手段】CDR回路310は、遅延素子312−1〜312−4を含み、定期的に信号遷移の挿入されたデータ入力をトリガとしてクロックを抽出する分周器320と、分周器で抽出されたクロックに同期して入力データ信号をラッチするラッチ315−1〜315−8とを有する。

(もっと読む)

周波数シンセサイザ装置及び変調周波数変位調整方法

【課題】2つの変調経路を有する周波数シンセサイザ装置において、DACから電圧制御発振器に出力される制御電圧の振幅を適切に調整することができる。

【解決手段】周波数シンセサイザ装置10は、入力電圧に応じた発振周波数で発振する電圧制御発振器14、電圧制御発振器14からの信号を分周するプログラマブル分周器20、分周信号と基準クロックとの位相差を電圧制御発振器14に出力する周波数位相比較器22、送信データに応じて目標周波数変位分周波数を変位させる場合の調整電圧を電圧制御発振器14に出力するDAC12、調整電圧の校正時に、電圧制御発振器14を基準電圧電源に接続するスイッチ32、任意の送信データをDAC12に出力して発振させた状態で分周信号の周波数をカウントしたカウント値に基づいて、目標周波数変位に対応する調整電圧に対応した調整データを設定する変調周波数変位校正回路30を備える。

(もっと読む)

電圧制御発振回路

【課題】従来のノイズ除去手段にはノイズ原因となる一定の高調波成分を有するパルス信号を一旦生成してから、ノイズ除去のための変調をかける為、ノイズ除去のための変調をかける前の信号がノイズの原因となる。

【解決手段】電圧制御発振回路10を、車両に設置された電子機器に供給する交流電圧を出力する電圧制御発振回路10であって、電圧制御発振回路10は入力信号の電圧に応じた周波数の交流電圧を出力し入力信号は三角波かまたは正弦波であることを特徴とするものとする。

(もっと読む)

チャージポンプ回路

【課題】充放電電流の立ち上がりを高速にし、かつ誤動作のおそれがないチャージポンプ回路を提供する。

【解決手段】ダイオード接続されたトランジスタMp1と、トランジスタMp2と、指令信号UPbで制御されてMp1,Mp2のゲート間を接続するトランジスタMp3とで第1のカレントミラー回路が構成されている。トランジスタMp2のゲート電極と電源VDDの間には指令信号UPbで制御されるトランジスタMp4が接続されている。また、ダイオード接続されたトランジスタMn1と、トランジスタMn2と、指令信号DNで制御されてMn1,Mn2のゲート間を接続するトランジスタMn3とで第2のカレントミラー回路が構成されている。Mn2のゲート電極と接地の間には、指令信号DNbで制御されるトランジスタMn4が接続されている。

(もっと読む)

リファレンスリークの発生や位相ノイズを低減できるPLL回路

【課題】リファレンスリークを低減することができ、位相ノイズを抑制することができるPLL回路を提供する。

【解決手段】切り替え機能付き周波数位相比較器は、入力されるロック検出信号に基づいて、入力される2つの信号の立ち上がりエッジを検出することにより当該2つの信号の位相差を検出する周波数比較と、入力される2つの信号の電圧レベルを検出することにより当該2つの信号の位相差を検出する位相比較とを切り替えて行う。

(もっと読む)

141 - 160 / 1,193

[ Back to top ]