Fターム[5J106CC21]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788)

Fターム[5J106CC21]の下位に属するFターム

Fターム[5J106CC21]に分類される特許

201 - 220 / 1,193

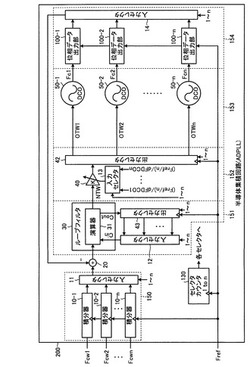

半導体集積回路

【課題】チップ面積の更なる縮小化を図ることができる半導体集積回路を提供する。

【解決手段】ディジタル制御発振器50−1〜50−nと、位相データ出力部100−1〜100−nと、積分処理部150と、フィルタ部151と、フィルタ部151からの時分割された出力信号に所定の係数を乗算した値を発振器制御値OTWとして出力する乗算器(第1の乗算器)40と、リファレンス周波数Frefに同期して、発振器制御値OTWを各ディジタル制御発振器50−1〜50−nに振り分ける出力セレクタ(制御値分離部)42と、を備える。

(もっと読む)

光受信装置及びクロック生成方法

【課題】分散値の調整を簡易かつ迅速に行うとともに、分散値の調整時にアンロック状態が発生することを回避すること。

【解決手段】分散補償部は、設定された分散値を用いて光信号の波長分散を補償する。位相差信号生成部は、分散補償部によって補償された光信号に含まれるクロックである外部クロックと、自装置内で用いるクロックである内部クロックとの位相差を算出することにより位相差信号を生成する。分散値調整部は、分散補償部に設定された分散値を調整する。抑制部は、分散値調整部によって分散値が調整された場合に、位相差信号生成部によって生成された位相差信号に現れる変動を抑制する。クロック生成部は、抑制部によって抑制された位相差信号に基づいて、外部クロックの位相と同期した内部クロックを生成する。

(もっと読む)

基準信号発生装置及び方法

【課題】 GPS信号の受信障害が発生しても、内蔵オシレータよりも高い周波数安定度の基準信号を発生することと、受信障害の発生前後で連続性の高い基準信号を出力することとを両立した基準信号発生装置を提供する。

【解決手段】 GPS受信機にて取得したGPS受信時刻と、そのGPS受信時刻の直前或いはその直後に標準電波受信機にて取得した標準電波受信時刻との時刻差を、予め定められた時間間隔毎に算出し、算出した時刻差と日時とを関連づけた時刻差データベースを構築する。GPS受信障害の発生を未検出のときGPS受信時刻に基づいて電圧制御発振器を制御して基準信号を発生し、GPS受信障害の発生を検出中は、時刻差データベースから取得した現在の日時に対応する時刻差に基づいて標準電波受信時刻を補正して電圧制御発振器を制御して基準信号を発生する。

(もっと読む)

PLL回路

【課題】ノイズフィルタ回路の特定を適切に自動設定可能なPLL回路を提供する。

【解決手段】PLL回路は、第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、信号遅延に応じて第3のクロック信号を発振する発振回路とを含み、フィルタ回路は、第1の遅延回路と同一構成であり制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、第2の遅延回路により第1のクロック信号をフィルタ処理して第2のクロック信号を生成する。

(もっと読む)

クロック切り替え回路

【課題】クロック切り替えの時間を短縮すること。

【解決手段】本発明は、光ケーブルを介して入力された光信号から抽出したクロック信号と、自回路内部のクロック源からのクロック信号との切り替えを行うクロック切り替え回路に適用される。本発明のクロック切り替え回路は、光信号からクロック信号を抽出するクロック抽出部と、前記クロック抽出部にて抽出されたクロック信号を、互いに異なる分周数で分周する複数の分周器と、前記複数の分周器にそれぞれ対応して設けられ、対応する分周器にて分周されたクロック信号のクロック周波数が所定のクロック周波数と一致する場合に同期信号を出力する複数の同期検出部と、光ケーブル接続が切断された場合、同期信号を出力した同期検出部に対応する分周器にて分周されたクロック信号から、当該クロック信号と同じクロック周波数成分を持ったクロック源からのクロック信号への切り替えを行うスイッチと、を有する。

(もっと読む)

クロック生成回路と半導体装置及びクロック生成方法

【課題】スペクトルの抑圧効果の高い変調波形を得ることができ、Hershey−kissによる変調方式と比べ、回路規模を小さくするクロック生成回路の提供。

【解決手段】変調波形生成部20は、SSCG変調波形として、tan波形またはtan+三角波を生成し、PLLループの低域パスフィルタ14の出力に、該SSCG変調波形を合成した信号を発振器(VCO)15に与える。

(もっと読む)

クロック制御回路及びこれを備える半導体装置

【課題】高速且つ正確にDLL回路をロックさせる。

【解決手段】外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相判定回路140と、位相判定信号PD0の論理レベルに基づいてカウント値が更新されるカウンタ回路130と、カウント値に基づいて外部クロック信号CLKを遅延させることにより、内部クロック信号LCLKを生成するディレイライン110と、位相判定信号PD0が変化しない期間においてはカウンタ回路130の更新ピッチを最小ピッチの2倍に設定し、位相判定信号PD0が変化したことに応答してカウンタ回路130の更新ピッチを最小ピッチに設定するピッチ調整回路300と、を備える。これにより、高速且つ正確にDLL回路をロックさせることが可能となる。

(もっと読む)

PLL回路のジッタ補正装置

【課題】PLL回路から発生するクロックジッタを検出し、基準クロック周波数と同期するPLL回路のジッタ補正装置を提供する。

【解決手段】ジッタ検出回路2がPLL回路1に入力する基準クロック周波数とPLL周波数とを比較したジッタ情報をマイコン3およびメモリ4に出力し、前記ジッタ情報に基づいてマイコン3は設定されているジッタ幅しきい値を超えるジッタ情報を基準クロック周波数との時間差からジッタ補正値を演算、PLL回路1に出力し、PLL回路1は補正後のPLL周波数を出力する。

(もっと読む)

半導体集積回路及びそれを用いた電子機器

【課題】低速ディジタル回路において発生するノイズがアナログ回路に与える影響を小さくし、回路ブロック毎のレイアウト変更を容易にする。

【解決手段】半導体集積回路は、(a)第1及び第2のVCOと、第1及び第2のVCOによって生成される信号を分周する第1及び第2の分周回路と、2つの分周信号の内の一方を選択する選択回路と、選択された分周信号に基づいて制御電圧を生成する制御電圧生成回路とを含むアナログ回路ブロックと、(b)変復調回路を含む第1のディジタル回路ブロックと、(c)制御回路を含む第2のディジタル回路ブロックとを備え、アナログ回路ブロックが、基板の第1及び第2の辺に沿って配置され、第2のディジタル回路ブロックが、基板の第3及び第4の辺に沿って配置され、第1のディジタル回路ブロックが、アナログ回路ブロックと第2のディジタル回路ブロックとの間に配置されている。

(もっと読む)

PLL回路

【課題】 ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路を提供する。

【解決手段】 VCO1からの出力周波数Foutを分周して基準信号との位相を比較して位相差を制御電圧としてVCO1に帰還させるPLL IC2を備え、制御回路6が、基準周波数FrefとDDS回路5における出力周波数Fddsの双方の周波数を細かく設定可能とし、両者の組み合わせによって、Fref及びその逓倍周波数に対するFddsの折り返し信号をDDS回路5で生成し、第1のAMP7で増幅し、可変フィルタ8によって所望のFdds(desired)を選択し、第2のAMP9で増幅して基準信号としてPLL IC2に供給し、制御回路6が、分周比NもPLL IC2に供給するPLL回路である。

(もっと読む)

PLL回路

【課題】 位相ノイズを低減し、設計が容易なPLL回路を提供する。

【解決手段】 PLL3が、基準周波数とVC−TCXO4からの出力を入力し、ロック動作を行い、ロック状態となると、セレクタ6は基準周波数を分周する第1の分周器2の出力を選択し、PLL3が、基準周波数入力断又はロック外れを検出すると、アラーム信号をセレクタ6に出力し、セレクタ6が、PLL3からのアラーム信号が入力されると、第1の分周器2の出力から、VC−TCXO4の出力を分周する第2の分周器5の出力に切り替えて出力し、PLL7が、セレクタ6の出力とVCXO8の出力とを入力し、ロック動作を行うPLL回路である。

(もっと読む)

通信システム

【課題】製造ばらつき・温度変動に依存することなく、受信状態又は送信状態を良好に保つ事が出来る通信システムを提供すること。

【解決手段】電圧制御発振部(106)の発振周波数を制御するように、位相同期回路(100)からの周波数制御信号(c1)を用いて、第2のLCタンク回路及び第3のLCタンク回路の少なくとも1つの同調周波数を制御することで、受信周波数の同調を行い、Q値制御回路(110)からのQ値制御信号(b1)を用いて第2のLCタンク回路及び第3のLCタンク回路の少なくとも1つのQ値制御用可変抵抗の抵抗値を可変することにより、第2のLCタンク回路及び第3のLCタンク回路の少なくとも1つのQ値を制御して、受信帯域の最適化を行う。

(もっと読む)

デジタルクロック再生器

サンプリング装置(110)は、変動する周期時間を有する入力クロック信号(CLKin)を受信し、入力クロック信号(CLKin)の平均周波数より実質的に高い周波数を有するサンプリングクロック信号(CLKsmpl)に基づいて、入力クロック信号(CLKin)をサンプリングする。サンプリング装置(110)は、入力クロック信号(CLKin)の各周期に対して、各周期長値(PL)を生成する。平均化装置(120)は、いくつかの周期長値(PL)をサンプリング装置(110)から受信し、それに基づき、前記数の周期長値(PL)に等しい周期数を含む平均化期間に渡って、入力クロック信号(CLKin)に対して平均周期時間を表す平均周期長値(PLavg)を生成する。出力装置(151)は、平均周期長値(PLavg)およびサンプリングクロック信号(CLKsmpl)に基づいて、安定した出力クロック信号(CLKout)を生成する。 (もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

基準周波数信号源

【課題】大幅なハードウエア変更を必要とすることなく、異なる基準信号に対応可能な基準周波数信号源を得る。

【解決手段】基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいてクロック信号および局部発振信号を生成する周波数変換回路10と、クロック信号に同期して、周波数制御データに応じた周波数信号を生成するDDS2と、DDS2からの周波数信号に含まれる不要波成分を抑圧するフィルタ3と、局部発振信号と電圧制御発振器の出力信号とを周波数混合するミクサ8と、ミクサ8からの混合信号に含まれる不要波成分を抑圧するフィルタ9と、フィルタ3を介した周波数信号とフィルタ9を介した混合信号との位相差を検出する位相比較器5と、位相比較器5からの位相差信号を濾波するループフィルタ6と、ループフィルタ6を介した位相差信号に応じて出力信号を生成する電圧制御発振器7とを備える。

(もっと読む)

記憶装置およびDLL回路制御方法

【課題】セルフリフレッシュ動作後にDLL回路がロック動作を実行しない状況での記憶装置の評価を行うことが可能な記憶装置を提供する。

【解決手段】通常モードとテストモードとを有しセルフリフレッシュ動作を行う記憶装置は、DLL回路と制御部とを含む。DLL回路は、入力信号を受け付けると入力信号を遅延した遅延信号を出力し、また、入力信号と遅延信号との位相差が所定値になるように遅延信号の遅延量を設定するロック動作を行い、その後、位相差が所定値である状態を維持する。制御部は、通常モード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させ、テストモード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させない。

(もっと読む)

デューティ補正回路、遅延同期ループ回路、カラムA/D変換器、固体撮像素子およびカメラシステム

【課題】デューティ比が50%より大きい場合も小さい場合も両方を一つの素子で対応が可能であり、素子数を削減できるだけではなく、スイッチング回数を削減することが可能で、消費電流を削減することができるデューティ補正回路、DLL回路、カラムA/D変換器、固体撮像素子、およびカメラシステムを提供する。

【解決手段】デューティ補正回路10は、第1入力および第2入力を有するC素子11と、C素子11の第2入力に接続されたインバータ12と、を有し、C素子11は、入力が両方とも論理“1”になると出力が論理“1”になり、入力が両方とも論理“0”になると出力が論理“0”になり、その他の状態では出力は前の状態を保持し、C素子11の第1入力およびインバータ12にそれぞれ互いに位相差がほぼ半周期の相補クロックが入力される。

(もっと読む)

PLLロック検出回路、及びPLLロック検出回路を有するPLLシンセサイザ回路

【課題】適切にPLL回路ロックがなされているか否かを検出する。

【解決手段】PLL回路ロックがなされているか否かを検出するPLLロック検出回路を構築する。ここにおいて、そのPLLロック検出回路は、基準発振器から供給される基準発振周波数を示す基準発振周波数信号と、前記基準発振周波数を分周して得られたリファレンス周波数を示し位相比較器に供給されるリファレンス周波数信号と、VCOから供給される電圧制御発振周波数を分周して得られた比較周波数を示し前記位相比較器に供給される比較周波数信号とを受ける、そして、前記リファレンス周波数信号と前記比較周波数信号とに基づいて、前記PLL回路ロックを示すロック検出信号を出力する。

(もっと読む)

同期信号生成装置、同期信号生成方法

【課題】ホールドオーバ状態からGPS通信衛星の電波を捕捉できる状態に復帰した場合、もしくはGPS通信衛星の電波を捕捉している状態からホールドオーバ状態に移行した場合、高精度の同期を迅速に行う同期信号生成装置、同期信号生成方法を提供することを課題としている。

【解決手段】同期信号生成装置1は、同期信号抽出部11と、制御部12と、同期部13と、DAC部(デジタル信号−アナログ信号変換部)14と、発振部15とを備えている。また、同期信号生成装置1には、GPS通信衛星アンテナ3と、基地局5とが接続されている。

(もっと読む)

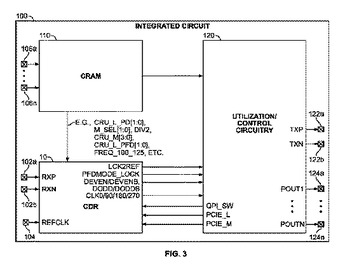

オートスピードネゴシエーションおよび他の可能な特徴を有するクロック・データ再生回路

集積回路(「IC」)は、入力データ信号からデータ情報を再生するためのクロック・データ再生(「CDR」)回路を含んでもよい。CDR回路は、参照クロックループと、データループとを含んでもよい。CDR回路によって出力される時刻変更(再生)データ信号は、その信号に含有される通信変更要求について、IC上の他の制御回路によって監視される。そのような要求に応答して、制御回路は、CDR回路の動作パラメータ(例えば、上述のループのうちのいずれか一方で使用される周波数分割ファクター)を変更することができる。これは、オートスピードネゴシエーションを採用するICサポート通信プロトコルに役立つことができる。  (もっと読む)

(もっと読む)

201 - 220 / 1,193

[ Back to top ]