Fターム[5J106CC21]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788)

Fターム[5J106CC21]の下位に属するFターム

Fターム[5J106CC21]に分類される特許

181 - 200 / 1,193

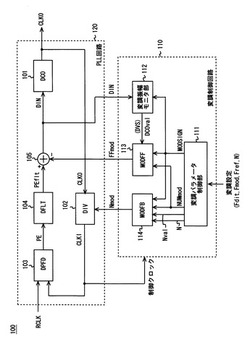

スペクトラム拡散クロック生成回路及びその制御方法

【課題】変調度が安定しない。

【解決手段】周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路。

(もっと読む)

半導体装置及びその測定方法

【課題】従来の測定方法では、測定電流の精度を十分に確保できない問題があった。

【解決手段】本発明の半導体装置の測定方法は、外部端子TMと、出力信号の位相及び周波数に応じてチャージポンプ回路12を制御する位相周波数比較器11と、周波数制御電圧生成ノードVNDに対する電流を出力するチャージポンプ回路12と、チャージポンプ回路12が出力する電流に応じて周波数制御電圧を周波数制御電圧生成ノードVNDに生成するループフィルタ14と、周波数制御電圧に応じて出力信号の周波数を制御する電圧制御発振器15と、を有する半導体装置の測定方法であって、外部端子TMを介してチャージポンプ回路12の出力電流を含む第1、第2の測定電流のいずれか一方を測定し、外部端子TMに流れるリーク電流を含む第3の測定電流を測定し、第1、第2の測定電流とリーク電流との差分に基づき流出電流IS1又は流入電流IS2の電流値を算出する。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】ジッタトレランスの低下、引き込み時間の増大、引き込みが不能等の問題を解消するクロックアンドデータリカバリ回路を提供する。

【解決手段】多相の抽出クロック信号で入力データをサンプリングするデータサンプリング回路11からのサンプリングデータ信号群の比較結果に基づきクロック信号の位相を進める信号(UP1)又は位相を遅らせる信号(DOWN1)、エラー検出時エラー信号(ERR)を出力する位相検出器12と、UP1/DOWN1信号を積分する第1の積分器13と、第2の積分器14と、第1の積分器の出力値(PPM)に基づき所定のパターンを生成するパターン発生器15と、第2の積分器の出力とパターン発生器の出力を合成する混合器16と、入力クロックを入力し前記混合器の出力信号に基づき位相を可変させた前記多相の抽出クロックを生成する位相補間器17から構成される。

(もっと読む)

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

デジタルPLL

【課題】位相差情報をデジタル値で出力するデジタルPLLにおいて、消費電力を抑えたデジタルPLLを提供することにある。

【解決手段】デジタルPLL100は、発振器10、整数位相算出部20、小数位相算出部30、位相差算出部40、位相差変化量モニタ部50、および発振器制御部60を有する。PLLにおいては発振器の出力周波数が、分周比により設定された所望の周波数に近づく、即ちロック状態に近づくにつれ位相差の変化量は減少していくことから、位相差変化量モニタ部50にて位相差の変化量をモニタし、変化量が整数位相算出部20の1LSB未満である「1」未満になった時点で整数位相算出部20におけるカウンタ動作を停止する。

(もっと読む)

半導体回路

【課題】DCC回路を備えたDLL回路の消費電力を低減させる。

【解決手段】制御信号DCCENに基づいて活性化・非活性化が制御されるデューティ変更検出回路21であって、入力されたクロック信号に基づいて生成されたクロック信号のデューティとあらかじめ設定されたデューティとを比較しその結果を出力するデューティ変更検出回路21と、デューティ変更検出回路の出力が生成されたクロック信号のデューティがあらかじめ設定されたデューティである目標値近傍にあることを示すときにはデューティ変更検出回路21を非活性化する制御信号DCCENを出力すると共に目標値近傍に無いときにはデューティ変更検出回路21を活性化する制御信号DCCENを出力するデューティ判定回路23とを備える。

(もっと読む)

基準信号発振器

【課題】優れた長期安定度を有する高安定発振器を用いた基準信号発振器において、高安定発振器に短時間の障害が発生したときにおいても、継続して安定して基準信号を出力すること。

【解決手段】高安定発振器としてルビジウム発振器やセシウム発振器を用い、これら発振器に比べて長期間の周波数安定度が劣るが、短期間の周波数安定度が高い準安定発振器であるOCXOをバックアップとして用いる。高安定発振器に異常が発生してからの経過時間と、両発振器の使用の重み付け(利用比率)とを対応させたテーブルを用意し、このテーブルを用いることで、高安定発振器が復帰した後、初めは準安定発振器の発振周波数を100%利用するが、その後段階的に準安定発振器の使用の重み付け(利用比率)を小さくし、高安定発振器の利用比率を大きくする。

(もっと読む)

DLL回路およびそれに使用されるレプリカ回路

【課題】 レイアウト的な制限がないDLL回路を提供すること。

【解決手段】 DLL回路に使用されるレプリカ回路は、第1の電源電圧が供給され、クロックバッファへの入力クロック信号が入力され、レプリカクロック信号を出力する遅延回路を含む。遅延回路は、第1乃至第MのCMOSインバータ回路および第(M+1)乃至第NのCMOSインバータ回路が縦続接続された回路である。複数のトランジスタは、遅延回路の後段側の第(M+1)乃至第NのCMOSインバータ回路のnチャネルMOSトランジスタのソースにそれぞれ接続されている。ローパスフィルタ回路は、第1の電源電圧と異なる第2の電源電圧を低域通過濾波して、その低域濾波した電源電圧を複数のトランジスタの制御端子へ供給する。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

電圧電流変換回路及びこれを備えたPLL回路

【課題】電源電圧依存性が小さい電圧電流変換回路及びこれを備えたPLL回路を提供する。

【解決手段】電圧電流変換回路は、第1電圧が供給される第1導電型のトランジスタで構成され、第1電流に基づいて第2電流を生成するカレントミラー回路と、前記第1電流が流れる第2導電型の第1のトランジスタと、一端が前記第1のトランジスタのソースに接続され、他端に第2電圧が供給され、入力された制御電圧に応じて抵抗値が変化する可変抵抗と、前記第2電流が流れ、ドレインとゲートとが前記第1のトランジスタのゲートに接続され、ソースに前記第2電圧が供給され、ゲート幅Wとゲート長Lとの比W/Lが前記第1のトランジスタの比W/Lより小さい第2導電型の第2のトランジスタと、前記第1電流または前記第2電流に基づいて出力電流を出力する電流出力部と、を備える。

(もっと読む)

クロック生成回路及びこれを備える半導体装置、並びに、クロック信号の生成方法

【課題】クロック信号の周波数に依存しないデューティ調整回路が搭載されたDLL回路を提供する。

【解決手段】内部クロック信号ICLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を指定するカウンタ回路123と、カウンタ回路123のカウント値を調整するカウンタ制御回路122と、内部クロック信号ICLKとレプリカクロック信号RepCLKのライズエッジが一致する第1及び第2のカウント値との差分を演算する減算回路133とを備え、得られた差分の1/2に相当する値に基づいて、内部クロック信号LCLKのフォールエッジを調整する。これにより、キャパシタを交互にディスチャージするタイプのデューティ調整回路を用いた場合のように、適用可能な周波数帯域が限られることがない。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

PLL回路

【課題】 安定した位相雑音特性を得ることができるPLL回路を提供する。

【解決手段】 基準発振器4からの基準周波数(Fref)信号のレベルを検波回路7で検出し、制御回路5が、検出したレベルが特定値に比べて小さい場合は可変ATT6の減衰量を小さくし、検出したレベルが特定値に比べて大きい場合は可変ATT6の減衰量を大きくする制御信号を可変ATT6に出力し、可変ATT6では制御回路5からの制御信号に従って基準周波数信号の減衰を行い、PLL IC2への基準周波数信号の入力レベルを安定化させ、位相雑音特性の劣化を防止し、更にアンロックを防止できるPLL回路である。

(もっと読む)

周波数シンセサイザ

【課題】 スプリアスを低減すると共にDDS回路本来の出力周波数帯域を十分に活用して所望の基準周波数信号を出力することができる周波数シンセサイザを提供する。

【解決手段】 DDS回路22の出力に、帯域制御電圧に応じて通過周波数帯域を可変とする帯域可変型フィルタ24を備え、制御回路21が、周波数の値と帯域制御電圧の値とを対応付けた制御電圧テーブルを記憶しており、外部からDDS回路22の出力周波数が設定されると、制御電圧テーブルを参照して、設定された出力周波数に対応する制御電圧を帯域可変型フィルタ24に出力して、帯域可変型フィルタ24をDDS回路からの出力周波数に応じたフィルタ特性としてスプリアス成分を除去する周波数シンセサイザとしている。

(もっと読む)

PLL装置

【課題】外部からの基準周波数信号の振幅レベルの適正範囲内を特定し、その適正範囲の内外に応じて電圧制御発振器に制御電圧を供給するPLL装置において、温度により動作が不安定になることを防ぐこと。

【解決手段】制御電圧出力部に供給される信号を位相比較部と予備信号供給部との間で切り替える切り替え部と、前記基準周波数信号の信号路とアースとの間に設けられ、当該基準周波数信号の振幅レベルを規制するために、ダイオードを逆並列に接続した保護回路と、この保護回路の雰囲気温度を検出する温度検出部と、外部からの前記基準周波数信号の振幅レベルを検出するレベル検出部と、を備えるようにPLL装置を構成し、検出温度に応じて前記切り替えの基準となるしきい値を設定し、前記ダイオードの温度特性により前記振幅レベルが変わることに対応する。

(もっと読む)

半導体集積回路

【課題】チップ面積の更なる縮小化を図ることができる半導体集積回路を提供する。

【解決手段】ディジタル制御発振器50−1〜50−nと、位相データ出力部100−1〜100−nと、積分処理部150と、フィルタ部151と、フィルタ部151からの時分割された出力信号に所定の係数を乗算した値を発振器制御値OTWとして出力する乗算器(第1の乗算器)40と、リファレンス周波数Frefに同期して、発振器制御値OTWを各ディジタル制御発振器50−1〜50−nに振り分ける出力セレクタ(制御値分離部)42と、を備える。

(もっと読む)

アナログ及びデジタルフィードバック制御を備えた位相ロック・ループ(PLL)

PLL回路

【課題】ループフィルタの容量値を抑え、且つ動作を安定させることが可能なPLL回路を提供することを目的としている。

【解決手段】入力信号の位相と電圧制御発振回路の出力信号の位相とを比較し、位相差に応じた信号を出力する位相比較器と、前記位相比較器の出力信号に応じて充放電電流を生成するチャージポンプ回路と、前記チャージポンプ回路の出力を平滑し第一の制御電圧を生成するループフィルタと、前記ループフィルタから出力される前記第一の制御電圧を所定の電圧になるよう第二の制御電圧を生成する制御電圧生成回路と、を備え、前記第一の制御電圧と前記第二の制御電圧とが前記電圧制御発振回路に入力される。

(もっと読む)

位相同期ループ回路、半導体集積回路、電子機器、位相同期ループ回路の制御方法

【課題】位相同期ループ回路において、制御応答の改善や消費電力の低減を図る。

【解決手段】発振器制御部255と分周器制御部257は、発振制御信号と分周制御信号が、引込み過程およびロック時の双方において、ループフィルタ電圧に基づいて比例関係を持って連動して変化するようにする。発振部210と分周部220が引込み過程およびロック時の双方において連動した動作をする。引込み過程およびロック時の双方における任意のループフィルタ電圧に対応する分周部220の最高動作周波数が発振部210の発振出力信号の周波数よりも常に高くなるように各制御信号の関係を設定する。ロック時の分周制御信号は、引込み過程における発振部210の発振出力信号の最高周波数と対応するループフィルタ信号に基づくバイアス電流よりも小さなバイアス電流を分周部220に自動的に設定するようになる。このことにより、ロック時の電力消費を低減できる。

(もっと読む)

181 - 200 / 1,193

[ Back to top ]