Fターム[5J106CC21]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788)

Fターム[5J106CC21]の下位に属するFターム

Fターム[5J106CC21]に分類される特許

341 - 360 / 1,193

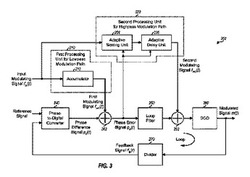

アキュムレータおよび位相デジタル変換器を使用する2ポイント変調のデジタル位相同期ループ

2ポイント変調をサポートするデジタル位相同期ループ(DPLL)が説明される。1つの設計において、DPLLは、位相デジタル変換器、ループ内で動作するループフィルタ、ローパス変調パスのための第1の処理ユニットおよびハイパス変調パスのための第2の処理ユニットを含む。第1の処理ユニットは、入力変調信号を受信し、位相デジタル変換器の後でループフィルタより前のループの内部の第1のポイントに対して第1の変調信号を供給する。第2の処理ユニットは、入力変調信号を受信し、ループフィルタより後のループの内部の第2のポイントに対して第2の変調信号を供給する。第1の処理ユニットは、周波数を位相に変換するために入力変調信号を累算するアキュムレータを含み得る。第2の処理ユニットは、可変利得で入力変調信号をスケールするスケーリングユニットを含み得る。 (もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

位相調整装置及び無線受信装置

【課題】効率的に且つ比較的低消費電力で目的の信号との位相を調整するのに好適な位相調整装置及び無線受信装置を提供する。

【解決手段】位相調整装置100を、遅延量を可変可能なインバーター回路IV1〜IVNをループ構成に接続してなる遅延段回路10と、遅延段回路10の遅延量を一定に保持する位相同期用回路20と、遅延段回路10の各接続部に入力端子が電気的に接続された接続切替回路SW1〜SWMを含む接続切替回路群30と、切替制御回路40と、信号出力回路50とを含む構成とし、切替制御回路40は、遅延段回路10における各インバーター回路に対応する接続切替回路を1つずつ且つ周回して選択し、選択した接続切替回路SWからのみ遅延信号を出力するように制御すると共に、偶数番目に選択された接続切替回路SWからの遅延信号を反転して後段の回路に供給するように信号出力回路50を制御する。

(もっと読む)

通信装置、位相同期ループ、移動体および通信方法

【課題】通信装置、位相同期ループ、移動体および通信方法を提供すること。

【解決手段】受信信号の同期保持を行うための位相同期ループ254を備え、前記位相同期ループは、n次の位相同期ループ用の回路構成nを包含する、m次の位相同期ループ用の回路構成m(m>n)、を有するループフィルタ109と、前記ループフィルタにおいて有効化される回路構成を、前記回路構成nと前記回路構成mとで切替える切替部と、を含む、通信装置。

(もっと読む)

位相調整装置及び無線受信装置

【課題】効率的に且つ低消費電力で目的の信号との位相を調整するのに好適な位相調整装置及び無線受信装置を提供する。

【解決手段】位相調整装置100を、制御電圧によって遅延量を可変可能なインバーター回路IV1〜IVNをループ構成に接続してなる遅延段回路10と、遅延段回路10の遅延量を一定に保持する位相同期用回路20と、遅延段回路10の各接続部に入力端子が電気的に接続された接続切替回路SW1〜SWMを含む接続切替回路群30と、切替制御回路40とを含む構成とし、切替制御回路40は、遅延段回路10における1つおきに且つ周回して順に並ぶ各インバーター回路に対応する接続切替回路を1つずつ選択し、選択した接続切替回路が、遅延信号を後段の回路に供給するように、その他の接続切替回路が遅延信号を後段の回路に供給しないようにする切替制御信号を生成し、これを各接続切替回路に供給する。

(もっと読む)

位相同期回路

【課題】位相誤差および周波数精度等の性能に優れ、かつ低価格で、広い制御電圧入力範囲を持つ電圧制御発振器を利用したPLL回路を提供する。

【解決手段】位相比較器11とチャージポンプ12は、低電圧トランジスタで構成され、電源電圧VLの可変電圧源16と電源電圧VDC(=VL+VCC1)の可変電圧源17から与えられる差の電圧VCC1(例えば、5V)で動作する。チャージポンプ12の出力電流をループフィルタ14で積分して生成された制御電圧VCは、0〜VCC2(例えば、16V)を制御電圧入力範囲とする電圧制御発振器15に与えられる。このとき、制御電圧VCの変化範囲は5V以下となるが、可変電圧源16,17の出力電圧VL,VDCを制御することで変化範囲を0〜16Vに拡大し、電圧制御発振器15から所望の周波数の出力信号OUTを出力させることができる。

(もっと読む)

チャージポンプ、周波数シンセサイザ、及び、制御方法

【課題】出力電圧が変化したときでも、電流値の変化を抑制できるチャージポンプを提供する。

【解決手段】電流源101は、出力端子157に向けて電流を流し、電流源102は、出力端子157から電流を引き抜く。電流調整回路108は、電流源101及び102の電流を制御する。電流調整回路108は、電流源102を所定の電流が流れるように制御しつつ電流源101を電流源102を流れる電流とバランスするように制御する第1のモードと、電流源101を所定の電流が流れるように制御しつつ電流源102を電流源101を流れる電流とバランスするように制御する第2のモードとを切り替え可能である。判定回路105は、出力端子157の電圧に応じて、第1のモードと第2のモードとを切り替える。

(もっと読む)

発振器及びそれを用いた周波数生成回路並びに無線通信システム

【課題】LC型発振器において、高調波歪みによる位相雑音の劣化が小さく、かつ発振振幅の増大化を図り、これにより良好な低位相雑音特性を有する発振器及びそれを用いた通信システムを提供する。

【解決手段】トランジスタからなる少なくとも1つ以上の電圧-電流変換部と、1対の容量性素子と誘導性素子からなるLCタンクを2つ有している共振器とを具備して成り、前記の電圧-電流変換部の出力端子は、前記の共振器に接続され電流-電圧変換されたのちに、前記電圧-電流変換部の入力端子に接続されることにより、帰還ループが構成されて成り、前記共振器を構成している2つのLCタンクを構成する誘導性素子が相互誘導結合されており、前記相互結合係数がおおよそ-0.6であることを特徴とする。

(もっと読む)

DLL回路

【課題】LPF出力の変化に対するロック周波数の変化量のゲイン設定のばらつきの抑制でジッタ精度をより向上できるDLL回路の提供。

【解決手段】遅延クロックを生成する遅延回路101と、遅延クロックと入力クロックの位相差信号を出力する位相比較回路10と、位相差信号対応の位相差電圧を出力するチャージポンプ回路20と、チャージポンプ回路出力の高周波成分を除去するローパスフィルタ回路30と、ローパスフィルタ回路の出力電圧を電流に変換する第1電圧−電流変換回路40及び基準電圧Vrefを電流に変換する第2電圧−電流変換回路50を含み、第1電圧−電流変換回路の出力電流から第2電圧−電流変換回路の出力電流を減算した結果を変換した電圧とオフセット電流Idを変換した電圧とを含み、位相差電圧が基準電圧より小の場合、オフセット電流を変換した電圧を制御電圧Vcontとして遅延回路に出力する遅延制御回路102と、を備える。

(もっと読む)

原子発振器

【課題】原子セルに入射するレーザー光の光量依存性を抑えた高精度の原子発振器を提供すること。

【解決手段】レーザー光源10から射出されるレーザー光の発光強度が変化しても、レーザー光源10と原子セル20との間に位置した透過光量可変手段40およびそれを制御する透過光量制御回路41によって原子セル20に入射するレーザー光の強度を一定にできる。したがって、基準発振周波数制御手段60によって、VCXO50の基準周波数をレーザー光検出器30で検出された射出光の強度に基づいて制御する際に、レーザー光の発光強度の変化に影響されることがなく、高精度な原子発振器100を得ることができる。

(もっと読む)

クロック供給装置

【課題】運用系および待機系システムクロックの位相を、バックボード間の配線遅延量、温度変化および電圧変動に起因するバッファ遅延の変化量を含め一致させたシステムクロック供給装置を提供する。

【解決手段】システムクロック1に位相同期した運用系および待機系システムクロック6を出力する冗長構成とされた運用系および待機系システムクロック供給部200と運用系および待機系システムクロックを装置内各部へ分配するためのバックボード8を有する。システムクロック1に位相同期したクロック22を生成するPLL210は、運用系システムクロックを基準とし、待機系システムクロックの位相を制御する位相差調整部211を含んだ構成とする。

(もっと読む)

PLL回路及びチャージポンプ回路

【課題】簡単な構成でPLL回路がロック時にオフリーク電流が生じるのを低減することが可能なチャージポンプ回路及びそのチャージポンプ回路を用いたPLL回路を提供することを課題とする。

【解決手段】P型トランジスタMP1及びN型トランジスタMN1と並列に常にオフにしたP型トランジスタMP2及びN型トランジスタMN2を設ける。P型トランジスタMP1とN型トランジスタMN2が共にOFFのときオフリーク電流はP型トランジスタMP2及びN型トランジスタMN2を介して逃げる。また常にオフにしたP型トランジスタMP2及びN型トランジスタMN2の代りに動的にオン/オフを切替えるP型トランジスタやN型トランジスタを設けたり、P型トランジスタMP1及びN型トランジスタMN1のオフ抵抗と同じ抵抗値の抵抗器を設けても良い。

(もっと読む)

電圧制御発振器、並びにそれを用いた無線通信システム及び位相同期回路。

【課題】 位相雑音特性の良好な電圧制御発振器、並びにそれを用いた無線通信システム及び位相同期回路を提供することを目的とする。

【解決手段】

電圧制御発振器10は、共振器Resと、共振器Resに入力側が接続された増幅器AMP1と、増幅器AMP1の出力側と共振器Resとの間に接続されたキャパシタC1aと、増幅器AMP1の入力側と出力側の間に、互いに直列になるように接続されたキャパシタC1bとインダクタL1を備える。さらに、共振器Resに入力側が接続された増幅器AMP2と、増幅器AMP2の出力側と共振器Resとの間に接続されたキャパシタC2aと、増幅器AMP2の入力側と出力側の間に、互いに直列になるように接続されたキャパシタC2bとインダクタL2とを備える。

(もっと読む)

非重複クロック生成のための技術

【解決手段】望ましい周波数範囲にわたって、正確な非重複時間及びクロックフェーズ遅延時間を生成する技術が提供される。一構成において、装置はそれに結合されるクロック生成回路への制御電圧を順に生成する遅延ロックループ(DLL)回路を含む非重複クロック生成回路を備えている。制御電圧はクロック生成回路によって生成される非重複遅延クロック信号の正確なタイミング関係を維持するように動作する。一態様において、DLL回路は知られたデューティサイクルによる入力クロックを受信し、入力クロックサイクルの特定の部分へのユニット遅延をフィックスする出力制御電圧を得る。更なる態様において、クロック生成回路は製造プロセス変化とは関係ない非重複時間(tnlp)でクロック信号の第1のセットから遅延されたクロック信号の第2のセット及びクロック信号の第1のセットを生成するDLL回路に結合される複数の電圧制御遅延セルを備えている。 (もっと読む)

PLL回路

【課題】VCOのVT端子側から見えるバラクタダイオード数を減少させることによりリファレンスリークを低減するPLL回路を提供する。

【解決手段】PLL回路を構成するループフィルタから出力されるVCO制御電圧とVCOを予め関連付けて設定し、ループフィルタのVCO制御電圧に基づいて対応するVCOを選択し、該VCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を制御する切替信号を生成するVCO切替回路と、切替信号に基づいて、選択されたVCOのみの電圧制御発振器制御電圧端子とループフィルタの出力端子を接続し、他のVCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を解除するVT選択回路と、を備えるVCOの制御電圧端子にバラクタダイオードが接続された、発振周波数帯域の異なる複数のVCOを備えるPLL回路である。

(もっと読む)

半導体装置

【課題】リード動作時における位相調整精度を低下させることなく、DLL回路の消費電力を低減する。

【解決手段】ODT機能を有するデータ入出力回路80と、データ入出力回路80の動作タイミングを規定する内部クロックLCLKを生成するDLL回路100とを備える。DLL回路100は、内部クロックLCLKを高精度に位相制御する第1のモードと、低消費電力で動作する第2のモードとを有し、データ入出力回路80がODT動作を行っていない場合には第1のモードで動作し、データ入出力回路80がODT動作を行っている場合には第2のモードで動作する。このように、ODT動作の有無によってDLL回路100の動作モードを切り替えていることから、厳密な位相制御が不要なODT動作時における消費電力を低減することが可能となる。

(もっと読む)

信号処理装置

【課題】 温度によるクロックの変動を抑える。

【解決手段】 クロックを用いて信号を生成する信号処理部と、外部からの入力信号と前記信号処理部から出力された信号との位相差を検出し、前記位相差を示す信号を出力すると共に前記入力信号が無くなるとその直前の位相差の信号を出力する位相差検出部と、温度補償型の発振器からの出力信号に応じて前記位相差検出部からの出力に応じた値をカウントし、前記カウント値に基づいて基準信号を生成するデジタル発振器と、前記デジタル発振器からの基準信号と前記クロックを分周した信号との位相差に応じて前記クロックを生成するクロック生成部とを備える。

(もっと読む)

データ再生回路

【課題】バースト光信号が入力された場合のロックアップ動作を高速に行うデータ再生回路を得ること。

【解決手段】本発明にかかるデータ再生回路は、VCO4で生成したクロックと入力データとを比較し、比較結果に基づいてVCO4への入力電圧を調整するPLL回路(周波数・位相比較器1,フィルタ処理回路2,VCO4)と、VCO4で生成されたクロックを利用して入力データを識別再生する識別回路6と、各子局装置からの送信スケジュールに基づいて、データ入力区間を特定する受信タイミング生成回路8と、を備え、PLL回路は、第1のデータ入力区間が終了後、その次の第2のデータ入力区間が開始するまでの区間では、第1のデータ入力区間に含まれるEOB区間でVCO4への入力としていた電圧信号を、VCO4へ継続して入力させる。

(もっと読む)

PLL回路

【課題】本発明の課題は、PLL回路のリファレンスリークと位相雑音を低減することである。

【解決手段】チャージポンプ回路14は、ロック状態監視回路19から出力される、PLL回路11がロック状態か否かを示す信号に基づいてチャージポンプ電流を切り換える。PLL回路11がアンロック状態のときには、第1及び第2の電流供給回路からチャージポンプ電流を供給し、ロック状態となると、第2の電流供給回路からのみチャージポンプ電流を供給する。

(もっと読む)

遅延固定ループ回路の遅延ライン部及び遅延固定ループ回路におけるクロック信号の遅延固定方法

【課題】レイアウトの大きさを増大させず、速やかに位相を固定させることができる遅延固定ループ及び遅延固定ループにおけるクロック遅延固定方法を提供すること。

【解決手段】遅延ライン部は、第1の遅延時間d1を各々有する複数の第1の単位遅延セルを有し、クロック信号clkを遅延する第1遅延ラインと、第2の遅延時間d2を各々有する複数の第2の単位遅延セルを有し、第1遅延ラインにおいて遅延固定動作が達成されない場合に、クロック信号clkを遅延する第2遅延ラインと、第3の遅延時間d3を各々有する複数の第3の単位遅延セルを有し、第2遅延ラインにおいて遅延固定動作が達成されない場合に、クロック信号clkを遅延する第3遅延ラインとを備え、第1の遅延時間d1が第2の遅延時間d2より短く、第2の遅延時間d2が第3の遅延時間d3より短い。

(もっと読む)

341 - 360 / 1,193

[ Back to top ]