Fターム[5J106CC21]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788)

Fターム[5J106CC21]の下位に属するFターム

Fターム[5J106CC21]に分類される特許

361 - 380 / 1,193

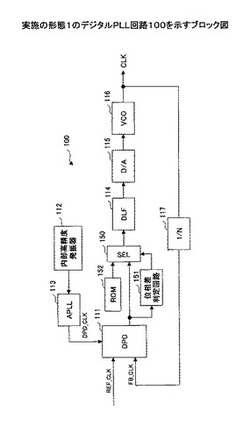

デジタルPLL回路

【課題】

映像信号をサンプリングするためのサンプリングクロック信号として用いても、映像に乱れを生じさせないクロック信号を生成することのできるデジタルPLL回路を提供することを課題とする。

【解決手段】

映像信号のサンプリングに用いるサンプリングクロック信号として、入力電圧に応じた発振周波数のクロック信号を出力する電圧制御発振回路と、映像信号の制御に用いられる複合同期信号と、前記電圧制御発振回路の出力に基づく帰還信号との位相差を検出する位相差検出部と、前記位相差検出部で検出される位相差が所定の範囲内にある場合は当該位相差を選択して出力し、前記位相差検出部で検出される位相差が前記所定の範囲内にない場合は前記位相差検出部で検出される位相差の目標値を出力する出力部とを含み、前記出力部の出力に基づいて、前記電圧制御発振回路の入力電圧を制御する。

(もっと読む)

PLL回路

【課題】本発明の課題は、PLL回路のリファレンスリークと位相雑音を低減することである。

【解決手段】チャージポンプ回路14は、ロック状態監視回路19から出力される、PLL回路11がロック状態か否かを示す信号に基づいてチャージポンプ電流を切り換える。PLL回路11がアンロック状態のときには、第1及び第2の電流供給回路からチャージポンプ電流を供給し、ロック状態となると、第2の電流供給回路からのみチャージポンプ電流を供給する。

(もっと読む)

発振器および位相同期ループ

【課題】発振器の位相雑音を低減し、位相同期ループの消費電力および位相雑音を低減する。

【解決手段】発振器は、共振回路の容量値に応じて発振周波数が可変する構成であって、外部から入力する外部クロックと設定データに応じて、オーバーフロー信号を間欠的に出力するアキュムレータ11と、オーバーフロー信号の間欠入力に応じてオン・オフするスイッチ12と、スイッチ12を介して共振回路に接続される固定容量値を有する容量素子C2とを備え、設定データに応じて間欠的に出力されるオーバーフロー信号の入力によりスイッチ12がオンとなるオン時間における発振周波数と、オーバーフロー信号が入力されないときにスイッチ12がオフとなるオフ時間における発振周波数との間で、オン時間とオフ時間の時間割合に応じた平均発振周波数を可変させる。

(もっと読む)

水晶発振器

【課題】実装スペースとコストの更なる低減のため、電子機器内の水晶部品を1つに集約するためには、消費電流や周波数精度の問題があった。

【解決手段】本発明の水晶発振器は、音叉型水晶振動体と、この振動体の温度による発振周波数の変化を、時間領域で連続的に補正するための温度補償回路を含んだ発振回路とを備え、この発振回路の出力を源振として高周波クロック信号を出力する、複数のPLL(フェイズロックループ)回路を備える。このような構成にすることにより、電子機器内で必要とされる全てのクロック信号を、精度良く提供することができる。

(もっと読む)

ディザ処理型クロック発生器

【課題】 位相分解能を高くし周波数スペクトラムのピークを低減したスペクトラム拡散クロック発生器を提供する。

【解決手段】 本発明のスペクトラム拡散クロック発生器100は、基準クロック信号と帰還クロック信号の位相差を検出する位相比較器20、チャージポンプ22、ループフィルタ24、多相のクロック信号を発生する多相VCO22、多相VCO26からの隣合う位相のクロック信号の位相を補間する位相補間部120、位相補完部120の位相選択を制御する位相選択部130、一定のステップ幅で段階的に変化する1周期分の変調波形データを記憶する変調データ部140、ディザステップ信号DSを出力するディザ処理部150、変調波形データとディザステップ信号を加算する加算器160を有する。位相選択部130は、ディザステップ信号が加算された変調波形データに基づき位相の補間を行う。

(もっと読む)

発振回路、発振回路を持つ装置、および発振方法

【課題】局部発振周波数を制御する制御電圧を得る際に用いられる電源回路(DC/DCコンバータ)の内部発振周波数に起因する障害を回避する。

【解決手段】電源回路10と電圧制御発振器13と基準発振器15と電圧制御発振器の発振周波数f(VCO)を電圧制御する制御回路16を備える。電源回路10は内部発振器11の発振信号Voから所定電圧Vzを提供する。電圧制御発振器13は可変容量ダイオード14に印加される制御電圧Vcontによって発振周波数が変化する。制御回路16は、基準発振器15の発振周波数f(REF)に基づく比較周波数f(COMP)とf(VCO)に基づく検査周波数f(CHK)との比較結果によりVcontを制御する。Vcontは所定電圧Vzを用いて生成される。ここで、Nを自然数としたときに、内部発振器11の発振周波数f(DD)が比較周波数f(COMP)のN倍より高くN+1倍より低くなるようにする。

(もっと読む)

PLL装置及びその制御方法

【課題】 基準入力期間に対して基準信号断期間が長期間継続しても、基準信号に同期して安定した信号を出力することが可能な、制御が容易で安価なPLL技術を提供する。

【解決手段】 基準発信源から入力される基準信号に対して所定の位相差を有する出力信号を生成するPLL装置は、前記基準信号と前記出力信号との位相を比較して、当該位相の位相差に対応する位相差信号を出力する比較手段と、基準となる位相差に対応する基準位相差信号を保持する保持手段と、前記位相差信号、又は、前記基準位相差信号を制御信号として選択する選択手段と、前記選択手段が選択した制御信号に応じた周波数の前記出力信号を発振して出力する発振手段と、を備え、前記選択手段は、前記基準発信源から前記基準信号が入力されている期間は前記位相差信号を選択し、前記基準発信源から前記基準信号が入力されていない期間は前記基準位相差信号を選択する。

(もっと読む)

PLL回路、送受信器及び携帯情報端末

【課題】長時間使用等の発熱でも周波数ロックが外れないPLL及びその制御方法を提供する。

【解決手段】本発明の基準周波数生成ブロックはPLL5、RF制御回路14及びBB制御回路24の3つから構成される。PLL5のループフィルタ102から引き出す検出信号(VTUNE)131が所定の電圧レンジから外れるとLKDETB信号61がPLL5からBB制御回路14に対して出力される。BB制御回路24はその後、RF制御回路14を介してPLL5の検出信号131の処理を止め、その後RF制御回路14にオートバンドセレクト動作を実行させる。この処理により、送受信を止めることなく実行し続ける無線LAN等の送受信器のVCOの温度特性の調整を行うことが可能となる。

(もっと読む)

基準周波数発生システム及び基準周波数発生装置

【課題】冗長化された基準周波数発生システムにおいて、現用側と予備側での出力切替時に出力信号のタイミングが急激に変動するのを防止する。

【解決手段】現用側の基準周波数発生装置51においては、自機のGPS受信機21aが生成する1PPS信号がPLL回路22aに供給される。予備側の基準周波数発生装置52においては、現用側の基準周波数発生装置51のGPS受信機21aからケーブル101を介して出力された1PPS信号がPLL回路22bに供給される。予備側に入力された1PPS信号は、ケーブル101と遅延量が等しいケーブル102を介して現用側に戻される。現用側の基準周波数発生装置51は、自機のGPS受信機21aからの1PPS信号と、予備側に出力して戻された1PPS信号と、の時間差に基づき補正用信号を出力する。予備側の基準周波数発生装置52は、補正用信号に基づいて、PLL回路22bの出力信号の位相を調整する。

(もっと読む)

クロック位相調整回路

【課題】実装面積や消費電力を低減させることができるクロック位相調整回路を提供すること。

【解決手段】n個の第1の遅延素子15を多段に接続し、入力クロック信号INCLKをその周期の1/nずつ遅延させたクロック信号をそれぞれ出力するDLL回路2と、n個の第1の遅延素子15から出力されるクロック信号のうち1つのクロック信号を選択して出力する第1のセレクタ回路3と、この第1のセレクタ回路3から出力されるクロック信号CLK1を遅延させる遅延部4を備えている。遅延部4は、1又は複数の直列に接続された遅延回路20を有しており、この遅延回路20は、前段の遅延回路10に設けられた第1の遅延素子15の遅延量に対して1/2の遅延量を有する第2の遅延素子21と、入力されたクロック信号CLK1と第2の遅延素子21により遅延されたクロック信号のいずれかを選択して出力する第2のセレクタ回路22とを備える。

(もっと読む)

基準周波数発生器

【課題】リファレンス信号を取得できている状態において動作環境が通常のものから一時的に外れた場合でも、自走用制御信号を精度良く得ることができる基準周波数発生器を提供する。

【解決手段】基準周波数発生器は、電圧制御発振器と、位相比較器と、温度センサと、制御部と、を備える。制御部は、GPS受信機からの1PPS信号が供給されなくなると、ループフィルタから出力される制御電圧信号に代えて、自走用制御電圧信号を生成して電圧制御発振器を制御する。制御部は、電圧制御発振器が動作している経過時間に応じて、前記自走用制御電圧信号を決定する。また、この制御部は、1PPS信号を取得できているときに時系列で記憶された制御電圧信号から、温度センサの検出値が設定温度範囲から外れたときの制御電圧信号を除外した上で、残りの制御電圧信号の変化に基づいて前記自走用制御電圧信号を決定することができる。

(もっと読む)

原子発振器

【課題】安価な原子発振器を構成する。

【解決手段】原子共鳴器10が発生する共鳴信号54を増幅する増幅器18と、所定の周波数の低周波信号LWVを出力する低周波位相変調信号発生器21と、共鳴信号54と低周波信号LWVとに基づき制御電圧VCを出力する位相弁別器20と、制御電圧VCに基づき原子共鳴器10が正常に動作しているか否かを示すアラーム信号ALMを出力するアラーム回路30と、所定の電圧VDを発生する電圧発生部32と、アラーム信号ALMに基づき原子共鳴器10が正常に動作している場合は制御電圧VCを出力し、正常に動作していない場合は所定の電圧VDを出力するスイッチ回路34と、スイッチ回路34の出力に基づき出力信号OUTの周波数が制御される電圧制御水晶発振器23と、出力信号OUTと低周波信号LWVとに基づき逓倍及び合成したマイクロ波MWVを出力する周波数逓倍合成変調部22と、を含む原子発振器1。

(もっと読む)

遅延ロックループのための初期化回路

【課題】遅延ロックループのための起動回路を提供する。

【解決手段】遅延ロックループにおける初期化回路は、電源投入または他のリセットの後、クロック端縁が適切な動作のために適切な順序で位相検出器によって受取られることを確実にし、遅延ロックループのリセット後、初期化回路は、遅延線における遅延を増加(または減少)させるように位相検出器をイネーブルするより先に基準クロックの少なくとも1つの端縁が受取られることを確実にし、フィードバッククロックの少なくとも1つの端縁が受取られた後、初期化回路は位相検出器をイネーブルして、遅延線における遅延を減少(または増加)させる。

(もっと読む)

半導体装置

【課題】従来のデューティ検出回路では、キャパシタに対するプリチャージ後の充放電動作が、通常のデューティ検出動作中の充放電動作とは異なるものとなり、正確なデューティ検出ができなかった。

【解決手段】内部クロック信号CLKがハイレベルを取る期間とロウレベルを取る期間との比(デューティ比)を積算し、電気的に記憶する記憶部(キャパシタC1,C2)と、記憶部(キャパシタC1,C2)における積算動作(デューティ検出動作)を制御する積算動作制御回路42と、一端が積算動作制御回路42と接続され、他端が電源線(VDD,GND)に接続された定電流回路(バイアストランジスタBTr1,BTr2)と、積算結果を初期化するプリチャージ回路43とを備え、プリチャージ回路43による初期化の実施中に電流回路(バイアストランジスタBTr1,BTr2)に電流を流すようにする。

(もっと読む)

シンセサイザと、これを用いた受信装置及び電子機器

【課題】シンセサイザにおけるデジタル的な周波数制御に起因した位相雑音性能の悪化。

【解決手段】本発明のシンセサイザは、基準発振器から出力された基準発振信号が入力される比較器と、比較器の出力側に接続されたフィルタと、フィルタの出力側に接続されて発振信号を出力する発振器と、発振器の出力信号を制御部からの制御信号に基づいて分周する分周器とを備え、比較器は、分周器からの出力信号と基準発振器からの出力信号とを比較してこの比較結果を示す信号をフィルタに出力すると共に、制御部は、温度を検出する検出器の検出結果に基づいて分周器の分周比を時間間隔Tで制御し、時間間隔Tとフィルタのカットオフ周波数fcとの関係は、1/T≧fcを満たす構成である。

(もっと読む)

原子発振器

【課題】光源の輝度劣化の影響を回避する。

【解決手段】第1の励起光52を出力する励起光出力部12と、第1の励起光52を分光し第2の励起光152を出力する分光器24と、第1の励起光52により励起される第1のガスセル13を含み第1の周波数信号O1を出力する第1の原子発振部100と、第2の励起光152により励起される第2のガスセル113を含み第2の周波数信号O2を出力する第2の原子発振部200と、第1の周波数信号O1と第2の周波数信号O2とを混合した混合信号301を出力する周波数混合器310と、混合信号301の周波数を変換した出力信号OUTを出力する周波数変換部300と、を含む原子発振器1。

(もっと読む)

基準信号発生装置

【課題】演算処理能力の低い安価なCPUを用いても、ホールドオーバー時における位相差を抑制して、保守作業の時間的制限等の自走発振に係わる課題を解決することができる基準信号発生装置を実現する。

【解決手段】制御部10は、1PPSが入力されている間に同期型制御電圧信号のレベルを経時的に観測し、記憶する。制御部10は、リファレンス信号の入力断を検出すると、自走用第1制御電圧信号を生成し、電圧制御発振器14へ与える。また該自走用第1制御電圧信号を用いて前記電圧制御発振器を制御している期間において、自走用第2制御電圧信号の算出を開始する。そして前自走用第2制御電圧信号の記算出が完了し次第、自走用制御電圧補正値を算出し、位相差を相殺しながら制御を続ける。以後、H.O.が終了するまで、自走用第N制御電圧信号の算出を繰り返し、高精度な基準周波数信号を発生させる。

(もっと読む)

PLL回路及び発振装置

【課題】クロック信号を安定的に生成するPLL回路及び発振装置を提供すること。

【解決手段】水晶発振回路1は、同水晶発振回路1に設けた駆動可変部の駆動能力をPLL回路50aのループフィルタ59から出力される制御信号Slfの電圧値に応じて制御する。

(もっと読む)

リングオシレータ及びそれを用いたPLL回路

【課題】 リングオシレータで発生した高調波ノイズによる干渉を抑制できるリングオシレータ及びそのリングオシレータを備えたPLL回路を提供する。

【解決手段】 リングオシレータは、無線装置に内蔵され、複数段のインバータゲートからなる発振回路と、発振回路に接続された切り替えスイッチとを備える。発振回路が発生する高調波ノイズと無線装置の受信周波数とが干渉し、通信感度が低下する場合には、切り替えスイッチによりインバータゲートのリング状に接続される段数を切り替える。リングオシレータが発生する高調波ノイズの周波数を変えることで、無線装置の受信周波数との干渉を抑制する。

(もっと読む)

対称性負荷遅延セル発振器(symmetricloaddelaycelloscillator)

【解決手段】発振器は、制御回路と、対称性負荷遅延セルのリングとを含む。各遅延セルは、2つの新規な対称性負荷を含む。各負荷は、レベルシフト回路と、電流ソース接続されたトランジスタと並列に結合されたダイオード接続されたトランジスタとを含む。制御回路は、発振器入力信号をバイアス制御信号に変換し、バイアス制御信号は、対称性負荷の実効的な抵抗を、遅延セルの遅延が入力信号の関数であるように制御する。制御回路は、発振遅延セル出力信号が一定の振幅を有するように遅延セルのレベルシフト回路を制御するため、制御ループの対称性負荷レプリカを用いる。第1の有利な側面では、この一定の振幅により、発振器は広い周波数レンジで動作可能である。第2の有利な側面では、発振器入力信号は出力信号発振周波数に対して、実質的に線形の関係を有する。 (もっと読む)

361 - 380 / 1,193

[ Back to top ]