積層チップパッケージおよびその製造方法

【課題】積層チップパッケージを、低コストで短時間に大量生産できるようにする。

【解決手段】積層チップパッケージ1は、本体2と複数の貫通電極21とを備えている。本体2は、積層された複数の階層部分10と、それぞれ複数の階層部分10の全てを貫通する複数の貫通孔とを含んでいる。複数の貫通電極21は、本体2における複数の貫通孔内に設けられて複数の階層部分10の全てを貫通している。複数の階層部分10の各々は半導体チップを含んでいる。複数の階層部分10のうちの少なくとも1つは、半導体チップと複数の貫通電極21とを電気的に接続する配線31を含んでいる。配線31は、それぞれ複数の貫通孔のいずれかの壁面において露出してその貫通孔を通過する貫通電極21に接触する複数の導体32を含んでいる。

【解決手段】積層チップパッケージ1は、本体2と複数の貫通電極21とを備えている。本体2は、積層された複数の階層部分10と、それぞれ複数の階層部分10の全てを貫通する複数の貫通孔とを含んでいる。複数の貫通電極21は、本体2における複数の貫通孔内に設けられて複数の階層部分10の全てを貫通している。複数の階層部分10の各々は半導体チップを含んでいる。複数の階層部分10のうちの少なくとも1つは、半導体チップと複数の貫通電極21とを電気的に接続する配線31を含んでいる。配線31は、それぞれ複数の貫通孔のいずれかの壁面において露出してその貫通孔を通過する貫通電極21に接触する複数の導体32を含んでいる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、積層された複数の半導体チップを含む積層チップパッケージおよびその製造方法、ならびに積層チップパッケージの製造に用いられる基礎構造物に関する。

【背景技術】

【0002】

近年、携帯電話やノート型パーソナルコンピュータに代表される携帯機器では、軽量化と高性能化が求められている。それに伴い、携帯機器に用いられる電子部品の高集積化が求められている。また、デジタルカメラや映像記録装置等の画像・映像関連機器の発達に伴い、半導体メモリの大容量化、高集積化が求められている。

【0003】

近年、高集積化された電子部品として、システム・イン・パッケージ(System in Package;以下、SiPと記す。)、特に複数の半導体チップを積層する3次元実装技術を用いたSiPが注目されている。本出願において、積層された複数の半導体チップ(以下、単にチップとも記す。)を含むパッケージを、積層チップパッケージと呼ぶ。この積層チップパッケージには、高集積化が可能になるという利点に加え、配線の長さの短縮が可能になることから、回路の動作の高速化や配線の浮遊容量の低減が可能になるという利点がある。

【0004】

積層チップパッケージを製造するための3次元実装技術の主なものには、基板上に複数のチップを積層し、各チップに形成された複数の電極と、基板に形成された外部接続端子とを、ワイヤボンディングによって接続するワイヤボンディング方式と、積層される各チップにそれぞれ複数の貫通電極を形成し、この貫通電極によってチップ間の配線を行う貫通電極方式とがある。

【0005】

特許文献1には、貫通電極方式を用いて構成された積層メモリが記載されている。

【0006】

特許文献2には、積層された複数のチップ間の配線を、貫通電極に類似した配線プラグを用いて行うようにした3次元積層型半導体装置が記載されている。この3次元積層型半導体装置は、積層された複数のユニット半導体装置を含んでいる。1つのユニット半導体装置は、チップ電極を有する半導体チップと、配線パターンと、モールドレジンと、配線プラグとを備えている。配線パターンの一方の面には、チップ電極がマウントされている。モールドレジンは、半導体チップおよび配線パターンを覆っている。配線プラグは、モールドレジンを半導体チップの外側で貫通している。配線プラグの一端は配線パターンの一方の面に接触し、配線プラグの他端はモールドレジンから露出している。配線パターンの他方の面は、モールドレジンの表面に露出している。この3次元積層型半導体装置では、下段のユニット半導体装置の配線プラグを上段のユニット半導体装置の配線パターンの露出面に接触させることによって、複数の半導体チップ間の配線を行っている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2008−187061号公報

【特許文献2】特開2003−163324号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

ワイヤボンディング方式では、ワイヤ同士の接触を避けるために電極の間隔を小さくすることが難しいという問題点や、ワイヤの高い抵抗値が回路の高速動作の妨げになるという問題点がある。

【0009】

貫通電極方式では、上記のワイヤボンディング方式における問題点は解消される。しかし、従来の貫通電極方式では、チップに貫通電極を形成するために多くの工程が必要であることから、積層チップパッケージのコストが高くなるという問題点がある。すなわち、従来の貫通電極方式では、チップに貫通電極を形成するために、後に切断されることによって複数のチップとなるウェハに、複数の貫通電極用の複数の穴を形成し、次に、この複数の穴内およびウェハの上面上に絶縁層とシード層を形成し、次に、めっき法によって複数の穴内にCu等の金属を充填して複数の貫通電極を形成し、次に、余分なシード層を除去するという一連の工程が必要である。

【0010】

特許文献2に記載されている3次元積層型半導体装置では、従来の貫通電極方式における上記の問題点と同様に、配線プラグを形成するために多くの工程が必要であり、その結果、コストが高くなるという問題点がある。

【0011】

本発明はかかる問題点に鑑みてなされたもので、その目的は、積層された複数の半導体チップを含む積層チップパッケージを、低コストで短時間に大量生産できるようにした積層チップパッケージおよびその製造方法、ならびに積層チップパッケージの製造に用いられる基礎構造物を提供することにある。

【課題を解決するための手段】

【0012】

本発明の積層チップパッケージは、本体と複数の貫通電極とを備えている。本体は、積層された複数の階層部分と、それぞれ複数の階層部分の全てを貫通する複数の貫通孔とを含んでいる。複数の貫通電極は、本体における複数の貫通孔内に設けられて複数の階層部分の全てを貫通している。複数の階層部分の各々は半導体チップを含んでいる。複数の階層部分のうちの少なくとも1つは、半導体チップと複数の貫通電極とを電気的に接続する配線を含んでいる。

【0013】

本発明の積層チップパッケージにおいて、配線は、複数の貫通電極にそれぞれ電気的に接続された複数の導体を含み、複数の導体は、それぞれ、複数の貫通孔の壁面に現れて貫通電極の外面に接触する端面を有していてもよい。この場合、複数の導体は、それぞれ、複数の貫通電極が通過する電極通過孔を有し、電極通過孔の壁面が上記端面を構成していてもよい。

【0014】

また、本発明の積層チップパッケージにおいて、複数の階層部分の各々は、半導体チップを貫通するように形成された複数の絶縁材充填孔と、複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含み、複数の貫通孔は、複数の階層部分の絶縁層を貫通していてもよい。この場合、絶縁材は、主成分として樹脂を含んでいてもよい。絶縁材は、更に、樹脂に混合された絶縁性の粒状物を含んでいてもよい。

【0015】

また、本発明の積層チップパッケージにおいて、複数の階層部分は、1つ以上の第1の種類の階層部分と、1つ以上の第2の種類の階層部分とを含んでいてもよい。第1の種類の階層部分における半導体チップは正常に動作するものであり、第2の種類の階層部分における半導体チップは正常に動作しないものである。また、第1の種類の階層部分は配線を含むが、第2の種類の階層部分は配線を含まない。

【0016】

また、本発明の積層チップパッケージにおいて、複数の階層部分の各々は、半導体チップの周囲に形成された絶縁層を含み、複数の貫通孔は、複数の階層部分の絶縁層を貫通していてもよい。

【0017】

本発明の積層チップパッケージの製造方法は、

本体となる部分である本体形成部分を少なくとも1つ備え、本体形成部分は、複数の階層部分と、複数の貫通電極が設けられていない状態の複数の貫通孔とを含む基礎構造物を作製する工程と、

基礎構造物の本体形成部分における複数の貫通孔内に複数の貫通電極を形成する工程とを備えている。

【0018】

本発明の積層チップパッケージの製造方法において、基礎構造物は、少なくとも1つの本体形成部分として、複数の階層部分が積層された方向に直交する方向に配列された複数の本体形成部分を備えていてもよい。この場合、積層チップパッケージの製造方法は、更に、複数の貫通電極を形成する工程の後で、複数の本体形成部分を互いに分離して複数の本体を形成する工程を備えていてもよい。

【0019】

また、本発明の積層チップパッケージの製造方法において、複数の貫通電極は、めっき法によって形成されてもよい。

【0020】

また、本発明の積層チップパッケージの製造方法において、配線は、複数の貫通電極にそれぞれ電気的に接続された複数の導体を含み、複数の導体は、それぞれ、複数の貫通孔の壁面に現れて貫通電極の外面に接触する端面を有していてもよい。この場合、複数の導体は、それぞれ、複数の貫通電極が通過する電極通過孔を有し、電極通過孔の壁面が上記端面を構成していてもよい。

【0021】

また、本発明の積層チップパッケージの製造方法において、基礎構造物を作製する工程は、後に複数の貫通孔が形成されることによって基礎構造物となる初期基礎構造物を作製する工程と、初期基礎構造物に複数の貫通孔を形成して、基礎構造物を形成する工程とを含んでいてもよい。

【0022】

初期基礎構造物は、複数の貫通孔が形成される前の複数の階層部分である複数の初期階層部分を含んでいる。複数の初期階層部分の各々は、半導体チップを貫通するように形成された複数の絶縁材充填孔と、複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含んでいてもよい。この場合、基礎構造物を形成する工程において、複数の貫通孔は、複数の初期階層部分の絶縁層を貫通するように形成されてもよい。絶縁材は、主成分として樹脂を含んでいてもよい。絶縁材は、更に、樹脂に混合された絶縁性の粒状物を含んでいてもよい。

【0023】

複数の初期階層部分の各々が、上記の複数の絶縁材充填孔と絶縁層とを含んでいる場合において、基礎構造物は、少なくとも1つの本体形成部分として、複数の階層部分が積層された方向に直交する方向に配列された複数の本体形成部分を備えていてもよい。この場合、初期基礎構造物を作製する工程は、それぞれ、各々が本体に含まれる半導体チップのいずれかとなる予定の、配列された複数の半導体チップ予定部を含む複数のチップアレイを作製する工程と、複数のチップアレイを積層して初期基礎構造物を形成する工程とを含んでいてもよい。この場合、積層チップパッケージの製造方法は、更に、複数の貫通電極を形成する工程の後で、複数の本体形成部分を互いに分離して複数の本体を形成する工程を備えていてもよい。

【0024】

複数のチップアレイを作製する工程は、1つのチップアレイを作製するための一連の工程として、

互いに反対側を向いた第1および第2の面を有すると共に、配列された複数の半導体チップ予定部を含むアレイ前ウェハを作製する工程と、

アレイ前ウェハに対して、第1の面において開口し、後に複数の絶縁材充填孔となる複数の溝を形成する工程と、

複数の溝内に絶縁材を充填して、アレイ前ウェハの第1および第2の面に対応する第1および第2の面を有する研磨前アレイを形成する工程と、

複数の溝が複数の絶縁材充填孔となるように、研磨前アレイに対して、複数の溝が露出するまで、研磨前アレイの第2の面から研磨を行う工程とを含んでいてもよい。

【0025】

また、基礎構造物が複数の本体形成部分を備えている場合、複数の本体形成部分のうちの少なくとも1つにおける複数の階層部分は、1つ以上の第1の種類の階層部分と、1つ以上の第2の種類の階層部分とを含んでいてもよい。第1の種類の階層部分における半導体チップは正常に動作するものであり、第2の種類の階層部分における半導体チップは正常に動作しないものである。また、第1の種類の階層部分は配線を含むが、第2の種類の階層部分は配線を含まない。この場合、複数のチップアレイを作製する工程は、複数の半導体チップ予定部について、正常に動作する半導体チップ予定部と正常に動作しない半導体チップ予定部とを判別する工程と、正常に動作しない半導体チップ予定部では配線を形成することなく、正常に動作する半導体チップ予定部では配線を形成する工程とを含んでいてもよい。

【0026】

また、本発明の積層チップパッケージの製造方法において、初期基礎構造物は、複数の貫通孔が形成される前の複数の階層部分である複数の初期階層部分を含み、複数の初期階層部分の各々は、半導体チップの周囲に形成された絶縁層を含んでいてもよい。この場合、基礎構造物を形成する工程において、複数の貫通孔は、複数の初期階層部分の絶縁層を貫通するように形成されてもよい。

【0027】

本発明の基礎構造物は、積層チップパッケージを製造するために用いられるものである。この基礎構造物は、本体となる部分である本体形成部分を少なくとも1つ備えている。本体形成部分は、複数の階層部分と、複数の貫通電極が設けられていない状態の複数の貫通孔とを含んでいる。本発明の基礎構造物は、後に本体形成部分における複数の貫通孔内に複数の貫通電極が形成されるものである。

【0028】

本発明の基礎構造物は、少なくとも1つの本体形成部分として、複数の階層部分が積層された方向に直交する方向に配列された複数の本体形成部分を備えていてもよい。この場合、複数の本体形成部分は、複数の貫通電極が形成された後に、互いに分離されて複数の本体となる。複数の本体形成部分のうちの少なくとも1つにおける複数の階層部分は、1つ以上の第1の種類の階層部分と、1つ以上の第2の種類の階層部分とを含んでいてもよい。第1の種類の階層部分における半導体チップは正常に動作するものであり、第2の種類の階層部分における半導体チップは正常に動作しないものである。また、第1の種類の階層部分は配線を含むが、第2の種類の階層部分は配線を含まない。

【0029】

また、本発明の基礎構造物において、配線は、複数の貫通電極が形成されたときに複数の貫通電極にそれぞれ電気的に接続される複数の導体を含み、複数の導体は、それぞれ、複数の貫通孔の壁面に現れて貫通電極の外面に接触する端面を有していてもよい。この場合、複数の導体は、それぞれ、複数の貫通電極が形成されたときに複数の貫通電極が通過する電極通過孔を有し、電極通過孔の壁面が上記端面を構成していてもよい。

【0030】

また、本発明の基礎構造物において、基礎構造物に含まれる複数の階層部分の各々は、半導体チップを貫通するように形成された複数の絶縁材充填孔と、複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含み、複数の貫通孔は、複数の階層部分の絶縁層を貫通していてもよい。この場合、絶縁材は、主成分として樹脂を含んでいてもよい。絶縁材は、更に、樹脂に混合された絶縁性の粒状物を含んでいてもよい。

【0031】

また、本発明の基礎構造物において、基礎構造物に含まれる複数の階層部分の各々は、半導体チップの周囲に形成された絶縁層を含み、複数の貫通孔は、複数の階層部分の絶縁層を貫通していてもよい。

【発明の効果】

【0032】

本発明の積層チップパッケージまたはその製造方法、あるいは基礎構造物によれば、複数の階層部分の全てを貫通する複数の貫通孔内に、複数の階層部分の全てを貫通する複数の貫通電極を形成することによって、少ない工程数で、複数の貫通電極を備えた積層チップパッケージを製造することが可能になる。従って、本発明によれば、積層チップパッケージを、低コストで短時間に大量生産することが可能になるという効果を奏する。

【図面の簡単な説明】

【0033】

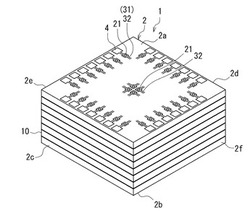

【図1】本発明の第1の実施の形態に係る積層チップパッケージの斜視図である。

【図2】下面側から見た図1の積層チップパッケージを示す斜視図である。

【図3】図1における1つの階層部分を示す斜視図である。

【図4】図1に示した積層チップパッケージの断面図である。

【図5】半導体チップに含まれるデバイスの一部を示す断面図である。

【図6】本発明の第1の実施の形態に係る積層チップパッケージの製造方法における一工程で作製されるアレイ前ウェハを示す平面図である。

【図7】図6に示したアレイ前ウェハの一部を示す断面図である。

【図8】図6に示した工程に続く工程を示す断面図である。

【図9】図8に示した工程に続く工程を示す断面図である。

【図10】図9に示した工程に続く工程を示す断面図である。

【図11】図10に示した工程に続く工程を示す断面図である。

【図12】図11に示した工程に続く工程を示す断面図である。

【図13】図12に示した工程に続く工程を示す断面図である。

【図14】図13に示した工程で作製される初期基礎構造物を示す斜視図である。

【図15】図13に示した工程に続く工程で作製される基礎構造物の一部を示す断面図である。

【図16】図15に示した基礎構造物における配線の一部を示す斜視図である。

【図17】図15に示した工程に続く工程を示す断面図である。

【図18】図17に示した工程で形成される貫通電極を示す斜視図である。

【図19】図17に示した工程の変形例を示す斜視図である。

【図20】本発明の第1の実施の形態における、複数の本体形成部分を分離して複数の本体を形成する工程を示す説明図である。

【図21】本発明の第2の実施の形態に係る積層チップパッケージの斜視図である。

【図22】本発明の第2の実施の形態における配線および貫通電極の一部を示す斜視図である。

【図23】本発明の第3の実施の形態に係る積層チップパッケージの斜視図である。

【図24】図23における1つの階層部分を示す斜視図である。

【図25】図23に示した積層チップパッケージの断面図である。

【図26】本発明の第3の実施の形態に係る積層チップパッケージの製造方法における一工程を示す断面図である。

【図27】図26に示した工程に続く工程を示す断面図である。

【図28】図27に示した工程に続く工程を示す断面図である。

【図29】図28に示した工程に続く工程を示す断面図である。

【図30】図29に示した工程に続く工程を示す断面図である。

【図31】図30に示した工程に続く工程を示す断面図である。

【図32】図31に示した工程に続く工程を示す断面図である。

【発明を実施するための形態】

【0034】

[第1の実施の形態]

以下、本発明の実施の形態について図面を参照して詳細に説明する。始めに、図1ないし図4を参照して、本発明の第1の実施の形態に係る積層チップパッケージの構成について説明する。図1は、本実施の形態に係る積層チップパッケージの斜視図である。図2は、下面側から見た図1の積層チップパッケージを示す斜視図である。図3は、図1における1つの階層部分を示す斜視図である。図4は、図1に示した積層チップパッケージの断面図である。

【0035】

図1、図2および図4に示したように、本実施の形態に係る積層チップパッケージ1は、ほぼ直方体形状の本体2を備えている。本体2は、上面2a、下面2bおよび4つの側面2c,2d,2e,2fを有している。本体2は、積層された複数の階層部分10を含んでいる。図1および図2には、一例として、本体2が、8つの階層部分10を含んでいる例を示している。しかし、本体2に含まれる階層部分10の数は8つに限らず、複数であればよい。上下に隣接する2つの階層部分10は、絶縁性の樹脂よりなる接着剤によって接合されている。

【0036】

積層チップパッケージ1は、更に、本体2の上面2aに配置された複数の端子4と、本体2の下面2bに配置された複数の端子5とを備えている。なお、積層チップパッケージ1は、複数の端子4と複数の端子5の一方のみを備えていてもよい。

【0037】

図4に示したように、本体2は、更に、本体2に含まれる複数の階層部分10の全てを貫通する複数の貫通孔20を含んでいる。積層チップパッケージ1は、更に、本体2における複数の貫通孔20内に設けられて複数の階層部分10の全てを貫通する複数の貫通電極21を備えている。貫通電極21は、例えばCu、Au、Ni、CrまたはZnによって形成されている。

【0038】

図3および図4に示したように、複数の階層部分10の各々は半導体チップ30を含んでいる。半導体チップ30は、上面、下面および4つの側面を有している。半導体チップ30の4つの側面は、それぞれ、本体2の側面2c,2d,2e,2fにおいて露出している。

【0039】

図3および図4には示していないが、複数の階層部分10の各々は、半導体チップ30を貫通するように形成された複数の絶縁材充填孔と、この複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含んでいる。そして、複数の貫通孔20は、複数の階層部分10の絶縁層を貫通している。複数の絶縁材充填孔と絶縁層については、後で詳しく説明する。

【0040】

本体2に含まれる複数の階層部分10のうちの少なくとも1つは、半導体チップ30と複数の貫通電極21とを電気的に接続する配線31を含んでいる。配線31は、複数の貫通電極21にそれぞれ電気的に接続された複数の導体32を含んでいる。複数の導体32は、それぞれ、複数の貫通孔20の壁面に現れて貫通電極21の外面に接触する端面を有している。導体32は、例えばCuによって形成されている。

【0041】

本体2に含まれる複数の階層部分10のうちの他の少なくとも1つは、配線31を含まないものであってもよい。以下、配線31を含む階層部分10を第1の種類の階層部分と呼び、符号10Aを付して表す。また、配線31を含まない階層部分10を第2の種類の階層部分と呼び、符号10Bを付して表す。第1の種類の階層部分10Aにおける半導体チップ30は正常に動作するものであり、第2の種類の階層部分10Bにおける半導体チップ30は正常に動作しないものである。以下、正常に動作する半導体チップ30を良品の半導体チップ30と言い、正常に動作しない半導体チップ30を不良の半導体チップ30と言う。図4には、本体2に含まれる複数の階層部分10のうち、上から3番目の階層部分10が第2の種類の階層部分10Bであり、他の7つの階層部分10が第1の種類の階層部分10Aである例を示している。

【0042】

1つの本体2において最も上に配置された階層部分10が第1の種類の階層部分10Aである場合には、複数の端子4は、その階層部分10における複数の導体32のそれぞれの一部によって構成されていてもよいし、複数の導体32に電気的に接続された他の複数の導体によって構成されていてもよい。1つの本体2において最も上に配置された階層部分10が第2の種類の階層部分10Bである場合には、複数の端子4は、本体2の上面2aに位置する複数の貫通電極21の上端部に電気的に接続された複数の導体によって構成される。複数の端子5は、本体2の下面2bに位置する複数の貫通電極21の下端部に電気的に接続された複数の導体によって構成されている。

【0043】

図3では、複数の導体32のうち、複数の端子4となる部分を破線で示している。複数の端子4が、最も上に配置された階層部分10における複数の導体32の一部によって構成されている場合、他の階層部分10における複数の導体32は、図3において破線で示した部分を含んでいてもよいし含んでいなくてもよい。

【0044】

半導体チップ30は、フラッシュメモリ、DRAM、SRAM、MRAM、PROM、FeRAM等のメモリを構成するメモリチップであってもよい。この場合には、複数の半導体チップ30を含む積層チップパッケージ1によって、大容量のメモリを実現することができる。また、本実施の形態に係る積層チップパッケージ1によれば、積層チップパッケージ1に含まれる半導体チップ30の数を変えることにより、64GB(ギガバイト)、128GB、256GB等の種々の容量のメモリを容易に実現することができる。

【0045】

半導体チップ30が複数のメモリセルを有する場合、半導体チップ30が1つ以上の欠陥のあるメモリセルを含んでいても、冗長技術によって正常に動作させることができる場合には、その半導体チップ30は、良品の半導体チップである。

【0046】

半導体チップ30は、メモリチップに限らず、CPU、センサ、センサの駆動回路等の他のデバイスを実現するものであってもよい。本実施の形態に係る積層チップパッケージ1は、特にSiPを実現するのに適している。

【0047】

次に、図5を参照して、半導体チップ30に含まれるデバイスの一例について説明する。ここでは、一例として、半導体チップ30に含まれるデバイスが、メモリを構成する複数のメモリセルを含む回路である場合について説明する。図5は、複数のメモリセルのうちの1つを示している。このメモリセル40は、P型シリコン基板41の表面の近傍に形成されたソース42およびドレイン43を備えている。ソース42およびドレイン43は、共にN型の領域である。ソース42とドレイン43は、これらの間にP型シリコン基板41の一部よりなるチャネルが形成されるように、所定の間隔を開けて配置されている。メモリセル40は、更に、ソース42とドレイン43の間において基板41の表面上に順に積層された絶縁膜44、浮遊ゲート45、絶縁膜46および制御ゲート47を備えている。メモリセル40は、更に、ソース42、ドレイン43、絶縁膜44、浮遊ゲート45、絶縁膜46および制御ゲート47を覆う絶縁層48を備えている。この絶縁層48には、ソース42、ドレイン43、制御ゲート47のそれぞれの上で開口するコンタクトホールが形成されている。メモリセル40は、それぞれ、ソース42、ドレイン43、制御ゲート47の上方の位置で絶縁層48上に形成されたソース電極52、ドレイン電極53、制御ゲート電極57を備えている。ソース電極52、ドレイン電極53、制御ゲート電極57は、それぞれ、対応するコンタクトホールを通して、ソース42、ドレイン43、制御ゲート47に接続されている。

【0048】

次に、本実施の形態に係る積層チップパッケージ1の製造方法について説明する。積層チップパッケージ1の製造方法は、基礎構造物を作製する工程を備えている。後で詳しく説明するが、基礎構造物は、本体2となる部分である本体形成部分を少なくとも1つ備えている。本体形成部分は、複数の階層部分10と、複数の貫通電極21が設けられていない状態の複数の貫通孔20とを含んでいる。積層チップパッケージ1の製造方法は、更に、基礎構造物の本体形成部分における複数の貫通孔20内に複数の貫通電極21を形成する工程を備えている。

【0049】

基礎構造物を作製する工程は、後に複数の貫通孔20が形成されることによって基礎構造物となる初期基礎構造物を作製する工程と、初期基礎構造物に複数の貫通孔20を形成して、基礎構造物を形成する工程とを含んでいる。

【0050】

基礎構造物は、上記の少なくとも1つの本体形成部分として、複数の階層部分10が積層された方向に直交する方向に配列された複数の本体形成部分を備えていてもよい。この場合、積層チップパッケージの製造方法は、更に、複数の貫通電極21を形成する工程の後で、複数の本体形成部分を互いに分離して複数の本体を形成する工程を備える。

【0051】

以下、基礎構造物が、複数の階層部分10が積層された方向に直交する方向に配列された複数の本体形成部分を備える場合を例にとって、積層チップパッケージ1の製造方法について詳しく説明する。まず、図6ないし図14を参照して、初期基礎構造物を作製する工程について詳しく説明する。

【0052】

初期基礎構造物を作製する工程では、まず、各々が本体2に含まれる半導体チップ30となる予定の、配列された複数の半導体チップ予定部30Pを含むアレイ前ウェハ101を作製する。図6は、アレイ前ウェハ101を示す平面図である。図7は、図6に示したアレイ前ウェハ101の一部を示す断面図である。

【0053】

アレイ前ウェハ101を作製する工程では、具体的には、互いに反対側を向いた2つの面を有する1つの半導体ウェハ100における一方の面に処理、例えばウェハプロセスを施すことによって、それぞれデバイスを含む複数の半導体チップ予定部30Pが配列されたアレイ前ウェハ101を作製する。アレイ前ウェハ101において、複数の半導体チップ予定部30Pは一列に配列されていてもよいし、縦方向と横方向にそれぞれ複数個並ぶように、複数列に配列されていてもよい。以下の説明では、アレイ前ウェハ101において、複数の半導体チップ予定部30Pは、縦方向と横方向にそれぞれ複数個並ぶように、複数列に配列されているものとする。半導体ウェハ100としては、例えばシリコンウェハが用いられる。ウェハプロセスとは、半導体ウェハを加工して、複数のチップに分割される前の複数のデバイスを作製するプロセスである。なお、図6は、理解を容易にするために、半導体ウェハ100に比べて半導体チップ予定部30Pを大きく描いている。例えば、半導体ウェハ100が12インチウェハで、半導体チップ予定部30Pの上面の一辺の長さが8〜10mmとすると、1枚の半導体ウェハ100を用いて、700〜900個の半導体チップ予定部30Pを形成することが可能である。

【0054】

図7は、アレイ前ウェハ101における1つの半導体チップ予定部30Pの一部を示している。図7に示したように、半導体チップ予定部30Pは、半導体ウェハ100の一方の面の近傍に形成されたデバイス形成領域33を含んでいる。デバイス形成領域33は、半導体ウェハ100における一方の面に処理を施すことによってデバイスが形成された領域である。図示しないが、半導体チップ予定部30Pは、更に、デバイス形成領域33の上に配置された複数の電極パッドを含んでいる。複数の電極パッドは、デバイス形成領域33に形成されたデバイスに電気的に接続されている。

【0055】

半導体チップ予定部30Pは、更に、デバイス形成領域33および電極パッドを覆う絶縁材料よりなるパッシベーション膜35を含んでいる。パッシベーション膜35は、複数の電極パッドの上面を露出させる複数の開口部35aを有している。以下、アレイ前ウェハ101において、パッシベーション膜35により近い面を第1の面101aと呼び、その反対側の面を第2の面101bと呼ぶ。

【0056】

初期基礎構造物を作製する工程では、次に、ウェハソートテストによって、アレイ前ウェハ101に含まれる複数の半導体チップ予定部30Pについて、正常に動作する半導体チップ予定部と正常に動作しない半導体チップ予定部とを判別する工程が行われる。この工程では、各半導体チップ予定部30Pの複数の電極パッドに試験装置のプローブを接触させて、試験装置によって、半導体チップ予定部30Pが正常に動作するか否かをテストする。図6において、記号“NG”を付した半導体チップ予定部30Pは、正常に動作しない半導体チップ予定部30Pであり、他の半導体チップ予定部30Pは、正常に動作する半導体チップ予定部30Pである。この工程によって、アレイ前ウェハ101毎に、正常に動作する半導体チップ予定部30Pと正常に動作しない半導体チップ予定部30Pの位置情報が得られる。この位置情報は、後で説明する配線31を形成する工程において利用される。

【0057】

図8は、図6に示した工程に続く工程を示す断面図である。この工程では、アレイ前ウェハ101に対して、第1の面101aにおいて開口し、後に複数の絶縁材充填孔となる複数の溝104Pを形成する。溝104Pは、その底部がアレイ前ウェハ101の第2の面101bに達しないように形成される。溝104Pの深さは、例えば50〜70μmの範囲内である。後に形成される貫通孔20は溝104Pの中を通る。従って、アレイ前ウェハ101の第1の面101aに平行な断面において、溝104Pの大きさは貫通孔20よりも大きい。溝104Pは、その中を複数の貫通孔20が通るものであってもよい。図8において、左側の溝104Pは、後に1つの貫通孔20が通るものであり、右側の溝104Pは、後に複数、例えば4つの貫通孔20が通るものである。上記断面における溝104Pの径は、例えば1.0〜90.0μmの範囲内である。図8には、上記断面における溝104Pの形状が矩形である例を示している。しかし、上記断面における溝104Pの形状は、矩形に限らず、円形、楕円形等でもよい。溝104Pは、例えば、エッチング液としてKOHを用いたウェットエッチングや、Cl2系のエッチングガスを用いた反応性イオンエッチングによって形成される。このようにして、複数の溝104Pが形成された後のアレイ前ウェハ101よりなる研磨前アレイ本体105が作製される。

【0058】

図9は、図8に示した工程に続く工程を示している。この工程では、研磨前アレイ本体105の複数の溝104P内に絶縁材を充填して、この絶縁材よりなる絶縁層106を形成すると共に、パッシベーション膜35の上面と絶縁層106の上面を平坦化する。このようにして、研磨前アレイ本体105と絶縁層106とを含む研磨前アレイ109が作製される。研磨前アレイ109は、アレイ前ウェハ101の第1の面101aに対応する第1の面109aと、アレイ前ウェハ101の第2の面101bに対応する第2の面109bとを有している。

【0059】

絶縁層106に用いられる絶縁材は、主成分として、ポリイミド樹脂等の樹脂を含んでいることが好ましい。ここで、主成分とは、50重量%以上の成分をいう。絶縁材は、更に、樹脂に加えて、樹脂に混合された絶縁性の粒状物を含んでいてもよい。絶縁性の粒状物は、例えばSiO2やAl2O3によって形成される。絶縁性の粒状物は、絶縁層106に発生する応力を緩和すると共に、絶縁層106の強度を増加させる役割を有する。

【0060】

絶縁層106の形成は、例えば以下の方法によって行われる。この方法では、まず、硬化前の樹脂を含む流動性の絶縁材を、複数の溝104P内に埋め込む。次に、例えば150〜250℃の範囲内の温度で絶縁材を熱処理(キュア)することによって、絶縁材を硬化させて絶縁層106とすると共に絶縁層106の上面を平坦化する。この方法において、流動性の絶縁材は、硬化前の樹脂に加えて、樹脂に混合された絶縁性の粒状物を含んでいてもよい。この場合、絶縁層106は、硬化後の樹脂と、この樹脂に混合された絶縁性の粒状物とを含むことになる。

【0061】

絶縁層106の形成は、上記の方法の代りに、例えば以下の方法によって行ってもよい。この方法では、硬化前の樹脂にスピンオングラス膜の原材料液を混合してなる流動性の絶縁材を、図8に示した研磨前アレイ本体105の上面上に塗布して、複数の溝104P内へ絶縁材を充填すると共に、パッシベーション膜35の上面と絶縁材の表面を平坦化する。次に、熱処理によって絶縁材を硬化させて絶縁層106とする。この場合、スピンオングラス膜の原材料液中のガラス成分が、絶縁層106において、樹脂に混合された絶縁性の粒状物になる。

【0062】

図10は、図9に示した工程に続く工程を示している。この工程では、前述の正常に動作する半導体チップ予定部30Pと正常に動作しない半導体チップ予定部30Pの位置情報に基づいて、正常に動作しない半導体チップ予定部30Pでは配線31(複数の導体32)を形成することなく、正常に動作する半導体チップ予定部30Pでは配線31(複数の導体32)を形成する。この工程は、例えば、フォトリソグラフィによりフォトレジスト層をパターニングすることによって、複数の開口部を有するフレームを形成する工程と、このフレームの複数の開口部に収容されるように、例えばめっき法によって複数の導体32を形成する工程とを含んでいる。複数の導体32は、パッシベーション膜35の複数の開口部35aを通って、デバイス形成領域33の上に配置された複数の電極パッドに電気的に接続される。絶縁層106の形成の際に、パッシベーション膜35の複数の開口部35aにも絶縁材が充填された場合には、複数の導体32を形成する前に、パッシベーション膜35の複数の開口部35aに充填された絶縁材を除去する。

【0063】

複数の導体32は、それぞれ、後に複数の貫通電極21が形成されたときに複数の貫通電極21が通過する電極通過孔32aを有している。電極通過孔32aの壁面は、貫通孔20の壁面に現れて、後に貫通電極21の外面に接触する。従って、電極通過孔32aの壁面は、貫通電極21の外面に接触する導体32の端面を構成する。

【0064】

電極通過孔32aは、絶縁層106の上面上に位置する。電極通過孔32aの径は、溝104Pの径よりも小さい。複数の貫通電極21が形成されたときに、電極通過孔32aの壁面が、その電極通過孔32aを通過する貫通電極21の外面に接触する。図10における左側の絶縁層106の上面上には、1つの導体32の1つの電極通過孔32aのみが位置している。図10における右側の絶縁層106の上面上には、4つの導体32の4つの電極通過孔32aが位置している。

【0065】

図11は、図10に示した工程に続く工程を示している。この工程では、まず、研磨前アレイ109の第1の面109aが、図11に示した板状の治具112の一方の面に対向するように、絶縁性の樹脂よりなる接着剤によって、研磨前アレイ109を治具112に張り付ける。以下、この治具112に貼り付けられた研磨前アレイ109を、第1の研磨前アレイ109と呼ぶ。図11において、符号113は、接着剤によって形成された絶縁層を示している。

【0066】

次に、第1の研磨前アレイ109における第2の面109bを研磨する。この研磨は、複数の溝104Pが露出するまで行う。この研磨により、複数の溝104Pは、複数の絶縁材充填孔104となる。また、第1の研磨前アレイ109における第2の面109bを研磨することにより、第1の研磨前アレイ109が薄くされて、治具112に張り付けられた状態のチップアレイ110が形成される。このチップアレイ110の厚みは、例えば20〜60μmの範囲内である。チップアレイ110は、配列された複数の半導体チップ予定部30Pを含んでいる。以下、治具112に張り付けられたチップアレイ110を、第1のチップアレイ110と呼ぶ。第1のチップアレイ110は、第1の研磨前アレイ109の第1の面109aに対応する第1の面110aと、その反対側の第2の面110bとを有している。第2の面110bは、研磨された面である。

【0067】

図12は、図11に示した工程に続く工程を示している。この工程では、まず、治具112に張り付けられた第1のチップアレイ110に、絶縁性の樹脂よりなる接着剤によって、研磨前アレイ109を張り付ける。この研磨前アレイ109は、第1の面109aが、第1のチップアレイ110の研磨された面すなわち第2の面110bに対向するように、第1のチップアレイ110に張り付けられる。以下、第1のチップアレイ110に張り付けられる研磨前アレイ109を、第2の研磨前アレイ109と呼ぶ。第1のチップアレイ110と第2の研磨前アレイ109とを接着する接着剤は絶縁層113となる。

【0068】

次に、図示しないが、第2の研磨前アレイ109における第2の面109bを研磨する。この研磨は、複数の溝104Pが露出するまで行う。この研磨により、複数の溝104Pは、複数の絶縁材充填孔104となる。第2の研磨前アレイ109における第2の面109bを研磨することにより、第2の研磨前アレイ109が薄くされて、第1のチップアレイ110に張り付けられた状態の第2のチップアレイ110が形成される。第2のチップアレイ110の厚みは、第1のチップアレイ110と同様に、例えば20〜60μmの範囲内である。

【0069】

図13は、図12に示した工程に続く工程を示している。この工程では、まず、図12に示した工程と同様の工程を繰り返し行って、所定の数のチップアレイ110の積層体を形成する。図13には、8つのチップアレイ110の積層体を形成した例を示している。次に、チップアレイ110の積層体を治具112から分離する。次に、チップアレイ110の積層体において最も上に配置されたチップアレイ110において、エッチングまたは研磨によって絶縁層113の一部を除去して、複数の導体32を露出させる。この露出した複数の導体32のそれぞれの一部は、複数の端子4を構成する。このようにして、積層された複数のチップアレイ110を含む初期基礎構造物115が形成される。図14は、初期基礎構造物115を示す斜視図である。

【0070】

各チップアレイ110は、配列された複数の半導体チップ予定部30Pを含んでいる。初期基礎構造物115は、複数の階層部分10が積層された方向に直交する方向に配列された複数の初期本体部分2Pを含んでいる。初期本体部分2Pは、後に複数の貫通孔20が形成されることによって本体形成部分となる部分である。

【0071】

図13は、初期基礎構造物115に含まれる複数の初期本体部分2Pのうちの1つにおける一部を示している。図13に示したように、初期本体部分2Pは、複数の貫通孔20が形成される前の積層された複数の階層部分10である積層された複数の初期階層部分10Pを含んでいる。複数の初期階層部分10Pの各々は、半導体チップ予定部30Pを含んでいる。以下の説明では、初期基礎構造物115の形成後における半導体チップ予定部30Pを半導体チップ30とする。複数の初期階層部分10Pの各々は、半導体チップ30を貫通するように形成された複数の絶縁材充填孔104と、この複数の絶縁材充填孔104内に充填された絶縁材よりなる絶縁層106とを含んでいる。なお、絶縁層113は、その下に位置する初期階層部分10Pの構成要素とする。

【0072】

初期基礎構造物115に含まれる複数の初期本体部分2Pの全てが、正常に動作しない半導体チップ30を含まないものであってもよい。あるいは、複数の初期本体部分2Pのうちの少なくとも1つは、正常に動作する半導体チップ30と正常に動作しない半導体チップ30とを、それぞれ1つ以上含むものであってもよい。

【0073】

次に、図15および図16を参照して、初期基礎構造物115を用いて基礎構造物を形成する工程について説明する。図15は、図13に示した工程に続く工程で作製される基礎構造物の一部を示す断面図である。図16は、図15に示した基礎構造物における配線の一部を示す斜視図である。この工程では、初期基礎構造物115の複数の初期本体部分2Pのそれぞれに対して複数の貫通孔20を形成する。これにより、初期本体部分2Pは本体形成部分2Qとなり、初期基礎構造物115は基礎構造物120となる。基礎構造物120は、複数の階層部分10が積層された方向に直交する方向に配列された複数の本体形成部分2Qを備えている。図15は、基礎構造物120に含まれる複数の本体形成部分2Qのうちの1つにおける一部を示している。

【0074】

基礎構造物120に含まれる複数の本体形成部分2Qの全てが、正常に動作しない半導体チップ30を含まないものであってもよい。あるいは、複数の本体形成部分2Qのうちの少なくとも1つは、正常に動作する半導体チップ30と正常に動作しない半導体チップ30とを、それぞれ1つ以上含むものであってもよい。

【0075】

図15に示したように、複数の貫通孔20は、複数のチップアレイ110(初期階層部分10P)が積層された方向に並ぶ複数の絶縁層106を貫通するように形成される。図15における左側の絶縁層106では1つの貫通孔20が貫通し、図15における右側の絶縁層106では4つの貫通孔20が貫通している。前述のように、複数の導体32の各々は、後に複数の貫通電極21が形成されたときに複数の貫通電極21のいずれかが通過する電極通過孔32aを有している。図15および図16に示したように、1つの貫通孔20は、複数のチップアレイ110(初期階層部分10P)が積層された方向に並ぶ複数の導体32の電極通過孔32aを通り、基礎構造物120(本体形成部分2Q)を貫通するように形成される。貫通孔20の径は、電極通過孔32aの径と等しく、絶縁材充填孔104の径よりも小さい。そのため、図15に示したように、貫通孔20を形成した後には、絶縁材充填孔104内において、貫通孔20の周囲に、当初の絶縁層106のうちの一部が残る。

【0076】

複数の貫通孔20の形成は、例えばレーザ加工を用いて行うことができる。絶縁層106が、主成分として樹脂を含む絶縁材によって形成されている場合には、レーザ加工によって、容易に且つ短時間で複数の貫通孔20を形成することができる。

【0077】

次に、図17ないし図19を参照して、基礎構造物120の本体形成部分2Qにおける複数の貫通孔20内に複数の貫通電極21を形成する工程について説明する。図17は、図15に示した工程に続く工程を示す断面図である。図18は、図17に示した工程で形成される貫通電極21を示す斜視図である。図19は、図17に示した工程の変形例を示す斜視図である。

【0078】

この工程では、例えばめっき法によって、複数の貫通孔20内に複数の貫通電極21を形成する。この工程では、まず、図17に示したように、基礎構造物120における最も下のチップアレイ110の下面に、めっき用のシード層141を接合する。シード層141は、Cu等の金属によって構成されている。シード層141は、樹脂等よりなる板142によって保持された金属膜であってもよい。あるいは、シード層141は、金属板であってもよい。この場合には、シード層141を保持する板142は不要である。

【0079】

次に、電気めっき法によって、基礎構造物120の複数の貫通孔20内に、それぞれ、めっき膜よりなる複数の貫通電極21を形成する。このとき、シード層141は通電され、めっき膜は、シード層141の表面から成長して、貫通孔20を埋める。

【0080】

図18は、複数のチップアレイ110が積層された方向に並ぶ複数の導体32と1つの貫通電極21を示している。前述のように、複数の導体32の各々は、複数の貫通電極21のいずれかが通過する電極通過孔32aを有している。複数の貫通電極21が形成されたときに、電極通過孔32aの壁面は、その電極通過孔32aを通過する貫通電極21の外面に接触する。これにより、導体32は貫通電極21に電気的に接続され、複数の導体32を含む配線31によって、半導体チップ30と複数の貫通電極21とが電気的に接続される。

【0081】

ここで、図19を参照して、図17に示した工程の変形例について説明する。この変形例では、電気めっき法によって複数の貫通電極21を形成する前に、無電解めっき法によって、基礎構造物120の複数の貫通孔20のそれぞれの壁面に金属膜よりなるシード層151を形成する。その後、電気めっき法によって、基礎構造物120の複数の貫通孔20内に、それぞれめっき膜を形成する。このとき、シード層151は通電され、めっき膜は、シード層151の表面から成長して、貫通孔20を埋める。この変形例では、シード層151とめっき膜とによって貫通電極21が構成される。この変形例の代わりに、無電解めっき法のみを用いて、複数の貫通電極21を形成してもよい。

【0082】

本体2の下面2bに配置された複数の端子5を備えた積層チップパッケージ1を製造する場合には、複数の貫通電極21を形成した後に、基礎構造物120の複数の本体形成部分2Qの下面に、例えばめっき法によって、複数の端子5を形成する。

【0083】

次に、図20を参照して、複数の貫通電極21を形成する工程の後で、基礎構造物120の複数の本体形成部分2Qを分離して複数の本体2を形成する工程について説明する。図20において、(a)は、1つの基礎構造物120を示している。この基礎構造物120は、複数の階層部分10が積層された方向に直交する方向に配列された複数の本体形成部分2Qを備えている。この工程では、基礎構造物120の複数の本体形成部分2Qが互いに分離されて複数の本体2が形成されるように、基礎構造物120を切断する。図20における(b)は、このようにして形成された複数の本体2のうちの1つを示している。上記のように基礎構造物120を切断することにより、複数の貫通孔20と複数の貫通電極21が形成された後の初期階層部分10Pは階層部分10となる。本体2は、積層された複数の階層部分10を含み、複数の階層部分10の各々は半導体チップ30を含んでいる。

【0084】

以上、図6ないし図20を参照して説明した一連の工程により、積層チップパッケージ1が複数個作製される。ここまでは、図13に示したように8つのチップアレイ110を含む初期基礎構造物115を用いて、8つの階層部分10を含む積層チップパッケージ1を複数個作製する例について説明してきた。しかし、本実施の形態では、初期基礎構造物115に含まれるチップアレイ110の数を変えることによって、階層部分10の数の異なる複数種類の積層チップパッケージ1を作製することができる。

【0085】

以上説明したように、本実施の形態に係る積層チップパッケージ1およびその製造方法、ならびに基礎構造物120によれば、積層された複数の階層部分10の全てを貫通する複数の貫通孔20内に、複数の階層部分10の全てを貫通する複数の貫通電極21を形成することによって、少ない工程数で、複数の貫通電極を備えた積層チップパッケージを製造することが可能になる。従って、本実施の形態によれば、積層チップパッケージ1を、低コストで短時間に大量生産することが可能になる。

【0086】

ところで、従来の貫通電極方式を用いた積層チップパッケージでは、積層された複数の階層部分の各々に複数の貫通電極が形成され、下側の階層部分における複数の貫通電極と上側の階層部分における複数の貫通電極とが電気的に接続される。この場合、下側の階層部分における複数の貫通電極と上側の階層部分における複数の貫通電極との間における位置ずれや抵抗の増加により、複数の半導体チップ間の電気的接続の信頼性が低下するおそれがある。

【0087】

これに対し、本実施の形態では、積層チップパッケージ1が複数の階層部分10の全てを貫通する複数の貫通電極21を備えるため、上述のような問題は生じない。そのため、本実施の形態によれば、複数の半導体チップ30間の電気的接続の信頼性を向上させることができる。

【0088】

また、本実施の形態において、図18に示したように、配線31の複数の導体32の各々が電極通過孔32aを有し、電極通過孔32aの壁面が、その電極通過孔32aを通過する貫通電極21の外面に接触する場合には、導体32と貫通電極21との接触面積を大きくすることができる。これにより、導体32と貫通電極21との電気的接続の信頼性を向上させることができる。

【0089】

ところで、もし、不良の半導体チップ30を含む第2の種類の階層部分10Bにおいても、配線31を介して半導体チップ30と複数の貫通電極21とが電気的に接続されていると、階層部分10Bにおける配線31は、メモリデバイス等、積層チップパッケージ1によって実現するデバイスにとって不要なキャパシタンスや不要なインダクタンスを発生させたり、良品の半導体チップ30に接続された配線31との間に浮遊容量を発生させたりする。このことは、メモリデバイス等のデバイスの動作の高速化の妨げとなる。

【0090】

これに対し、本実施の形態では、不良の半導体チップ30を含む第2の種類の階層部分10Bでは、半導体チップ30と複数の貫通電極21とを電気的に接続する配線31は設けられない。そのため、積層チップパッケージ1において、不良の半導体チップ30を含む第2の種類の階層部分10Bは、単なる絶縁層とみなすことができる。従って、本実施の形態によれば、不良の半導体チップ30に接続された配線に起因する問題を低減しながら、不良の半導体チップ30を使用不能にすることができる。

【0091】

[第2の実施の形態]

次に、図21および図22を参照して、本発明の第2の実施の形態について説明する。図21は、本実施の形態に係る積層チップパッケージの斜視図である。図22は、本実施の形態における配線および貫通電極の一部を示す斜視図である。

【0092】

図21および図22に示したように、本実施の形態では、配線31の複数の導体32の各々は、第1の実施の形態における電極通過孔32aを有しておらず、代わりに、貫通電極21の外面に接触する端面32bを有している。本実施の形態では、複数の貫通電極21を形成する前の基礎構造物120において、導体32の端面32bは、貫通孔20の壁面に現れている。そして、複数の貫通電極21が形成されたときに、導体32の端面32bは1つの貫通電極21の外面に接触する。これにより、導体32は貫通電極21に電気的に接続される。

【0093】

本実施の形態におけるその他の構成は、第1の実施の形態と同様である。また、本実施の形態における作用および効果は、電極通過孔32aに起因する事項以外は、第1の実施の形態と同様である。

【0094】

[第3の実施の形態]

次に、本発明の第3の実施の形態について説明する。始めに、図23ないし図25を参照して、本実施の形態に係る積層チップパッケージの構成について説明する。図23は、本実施の形態に係る積層チップパッケージの斜視図である。図24は、図23における1つの階層部分を示す斜視図である。図25は、図23に示した積層チップパッケージの断面図である。

【0095】

本実施の形態に係る積層チップパッケージ301は、第1の実施の形態と同様に、ほぼ直方体形状の本体2を備えている。本体2は、上面2a、下面2bおよび4つの側面2c,2d,2e,2fを有している。本実施の形態における本体2は、絶縁性の基体311と、この基体311の上に積層された複数の階層部分10を含んでいる。基体311は、例えば樹脂によって形成されている。図23および図25には、一例として、本体2が、8つの階層部分10を含んでいる例を示している。しかし、本体2に含まれる階層部分10の数は8つに限らず、複数であればよい。上下に隣接する2つの階層部分10は、絶縁性の樹脂よりなる接着剤によって接合されている。

【0096】

積層チップパッケージ301は、更に、本体2の上面2aに配置された複数の端子4と、本体2の下面2bに配置された複数の端子5とを備えている。なお、積層チップパッケージ301は、複数の端子4と複数の端子5の一方のみを備えていてもよい。

【0097】

図24および図25に示したように、本実施の形態における階層部分10は、半導体チップ30と、その周囲に配置された絶縁層312とを含んでいる。絶縁層312は、例えば樹脂によって形成されている。

【0098】

図25に示したように、本体2は、更に、本体2に含まれる複数の階層部分10の全てと基体311とを貫通する複数の貫通孔20を含んでいる。本実施の形態では、複数の貫通孔20は、複数の階層部分10の絶縁層312を貫通している。積層チップパッケージ301は、更に、本体2における複数の貫通孔20内に設けられて複数の階層部分10の全てと基体311とを貫通する複数の貫通電極21を備えている。貫通電極21は、例えばCu、Au、Ni、CrまたはZnによって形成されている。

【0099】

本体2に含まれる複数の階層部分10のうちの少なくとも1つは、半導体チップ30と複数の貫通電極21とを電気的に接続する配線31を含んでいる。配線31は、複数の貫通電極21にそれぞれ電気的に接続された複数の導体32を含んでいる。複数の導体32は、それぞれ、複数の貫通孔20の壁面に現れて貫通電極21の外面に接触する端面を有している。導体32は、例えばCuによって形成されている。本体2に含まれる複数の階層部分10のうちの他の少なくとも1つは、配線31を含まないものであってもよい。

【0100】

図23に示した例では、複数の端子4は、最も上に配置された階層部分10における複数の導体32のそれぞれの一部によって構成されている。しかし、複数の端子4は、複数の導体32に電気的に接続された他の複数の導体によって構成されていてもよい。複数の端子5は、本体2の下面2bに位置する複数の貫通電極21の下端部に電気的に接続されている。

【0101】

図24では、複数の導体32のうち、複数の端子4となる部分を破線で示している。複数の端子4が、最も上に配置された階層部分10における複数の導体32の一部によって構成されている場合、他の階層部分10における複数の導体32は、図24において破線で示した部分を含んでいてもよいし含んでいなくてもよい。

【0102】

次に、図26ないし図32を参照して、本実施の形態に係る積層チップパッケージ301の製造方法について説明する。第1の実施の形態と同様に、積層チップパッケージ301の製造方法は、基礎構造物を作製する工程を備えている。基礎構造物は、本体2となる部分である本体形成部分を少なくとも1つ備えている。本体形成部分は、基体311と、複数の階層部分10と、複数の貫通電極21が設けられていない状態の複数の貫通孔20とを含んでいる。積層チップパッケージ301の製造方法は、更に、基礎構造物の本体形成部分における複数の貫通孔20内に複数の貫通電極21を形成する工程を備えている。

【0103】

基礎構造物を作製する工程は、後に複数の貫通孔20が形成されることによって基礎構造物となる初期基礎構造物を作製する工程と、初期基礎構造物に複数の貫通孔20を形成して、基礎構造物を形成する工程とを含んでいる。

【0104】

以下、基礎構造物が、複数の階層部分10が積層された方向に直交する方向に配列された複数の本体形成部分を備える場合を例にとって、積層チップパッケージ301の製造方法について詳しく説明する。

【0105】

図26は、積層チップパッケージ301の製造方法における一工程を示す断面図である。積層チップパッケージ301の製造方法では、まず、基体311となる基体予定部を複数含む基板を用意し、この基板における複数の基体予定部の上にそれぞれ半導体チップ30を搭載する。図26は、基板のうちの1つの基体予定部311Pと、その上に搭載された半導体チップ30を示している。以下、1つの基体予定部311Pに注目して、積層チップパッケージ301の製造方法について説明する。基体予定部311Pの上に半導体チップ30を搭載する際には、基体予定部311Pの上に金属層を形成した後、その金属層の上に半導体チップ30を接合してもよい。基体予定部311Pの上に搭載された半導体チップ30は、本体2において最も下の階層部分10における半導体チップ30となる。

【0106】

半導体チップ30は、デバイス形成領域33と、デバイス形成領域33の上に配置された複数の電極パッド(図示せず)と、デバイス形成領域33および電極パッドを覆う絶縁材料よりなるパッシベーション膜35とを含んでいる。パッシベーション膜35は、複数の電極パッドの上面を露出させる複数の開口部35aを有している。

【0107】

図27は、図26に示した工程に続く工程を示す断面図である。この工程では、半導体チップ30の周囲における基体予定部311Pの上に絶縁層312を形成し、パッシベーション膜35の上面と絶縁層312の上面を平坦化する。

【0108】

図28は、図27に示した工程に続く工程を示す断面図である。この工程では、パッシベーション膜35および絶縁層312の上に、配線31を構成する複数の導体32を形成する。複数の導体32は、パッシベーション膜35の複数の開口部35aを通って、デバイス形成領域33の上に配置された複数の電極パッドに電気的に接続される。ここでは、第1の実施の形態と同様に、複数の導体32の各々が、後に複数の貫通電極21が形成されたときに複数の貫通電極21のいずれかが通過する電極通過孔32aを有している例を挙げる。ただし、複数の導体32の各々は、第2の実施の形態と同様に、電極通過孔32aを有さず、代りに端面32bを有するものであってもよい。

【0109】

図29は、図28に示した工程に続く工程を示す断面図である。この工程では、配線31(複数の導体32)の覆うように絶縁層313を形成し、この絶縁層313の上面を平坦化する。絶縁層313は、例えば樹脂によって形成される。図26ないし図29に示した一連の工程によって、初期基礎構造物のうち、本体2において最も下の階層部分10に対応する部分が形成される。

【0110】

図30は、図29に示した工程に続く工程を示す断面図である。この工程では、まず、絶縁層313の上に、半導体チップ30を搭載する。この半導体チップ30は、本体2において下から2番目の階層部分10における半導体チップ30となる。絶縁層313の上に半導体チップ30を搭載する際には、絶縁層313の上に金属層を形成した後、その金属層の上に半導体チップ30を接合してもよい。次に、図27ないし図29に示した一連の工程と同様にして、絶縁層312、配線31(複数の導体32)および絶縁層313を形成する。このようにして、初期基礎構造物のうち、本体2において下2番目の階層部分10に対応する部分が形成される。以下、同様の工程を繰り返し行って、初期基礎構造物115を形成する。初期基礎構造物115は、複数の階層部分10が積層された方向に直交する方向に配列された複数の初期本体部分2Pを含んでいる。初期本体部分2Pは、後に複数の貫通孔20が形成されることによって本体形成部分となる部分である。

【0111】

図30は、1つの初期本体部分2Pを示している。初期本体部分2Pは、複数の貫通孔20が形成される前の積層された複数の階層部分10である積層された複数の初期階層部分10Pを含んでいる。複数の初期階層部分10Pの各々は、半導体チップ30と、その周囲に配置された絶縁層312とを含んでいる。なお、絶縁層313は、その下に位置する初期階層部分10Pの構成要素とする。

【0112】

図31は、図30に示した工程に続く工程を示す断面図である。この工程では、初期基礎構造物115の複数の初期本体部分2Pのそれぞれに対して複数の貫通孔20を形成する。これにより、初期本体部分2Pは本体形成部分2Qとなり、初期基礎構造物115は基礎構造物120となる。基礎構造物120は、複数の階層部分10が積層された方向に直交する方向に配列された複数の本体形成部分2Qを備えている。図31は、1つの本体形成部分2Qを示している。

【0113】

本実施の形態では、複数の貫通孔20は、複数の初期階層部分10Pの絶縁層312を貫通するように形成される。また、1つの貫通孔20は、複数の初期階層部分10Pが積層された方向に並ぶ複数の導体32の電極通過孔32aを通り、基礎構造物120(本体形成部分2Q)を貫通するように形成される。複数の貫通孔20の形成方法は、第1の実施の形態と同様である。

【0114】

図32は、図31に示した工程に続く工程を示す断面図である。この工程では、複数の貫通孔20内に複数の貫通電極21を形成する。複数の貫通電極21の形成方法は、第1の実施の形態と同様である。複数の貫通電極21が形成されたときに、電極通過孔32aの壁面は、その電極通過孔32aを通過する貫通電極21の外面に接触する。これにより、導体32は貫通電極21に電気的に接続され、複数の導体32を含む配線31によって、半導体チップ30と複数の貫通電極21とが電気的に接続される。

【0115】

本体2の下面2bに配置された複数の端子5を備えた積層チップパッケージ301を製造する場合には、複数の貫通電極21を形成した後に、基礎構造物120の複数の本体形成部分2Qの下面に、例えばめっき法によって、複数の端子5を形成する。

【0116】

本実施の形態では、次に、第1の実施の形態と同様に、基礎構造物120を切断することによって、基礎構造物120の複数の本体形成部分2Qを分離して複数の本体2を形成する。このとき、基体予定部311Pは基体311となる。

【0117】

本実施の形態におけるその他の構成、作用および効果は、第1または第2の実施の形態と同様である。

【0118】

なお、本発明は、上記実施の形態に限定されず、種々の変更が可能である。例えば、初期基礎構造物の作製方法は、実施の形態に示した方法に限らない。例えば、2つの研磨前アレイ109(図10参照)を、それらの第1の面109a同士が対向するように、絶縁性の樹脂よりなる接着剤によって張り合わせた後、2つの研磨前アレイ109の第2の面109bをそれぞれ研磨して、2つのチップアレイ110の積層体を作製し、この2つのチップアレイ110の積層体を複数個張り合わせて初期基礎構造物を作製してもよい。

【0119】

また、本発明において、貫通電極を形成する方法は、めっき法に限らず、他の方法であってもよい。例えば、貫通孔に、銀や銅等の金属粉とバインダーとを含む導電ペーストを充填した後、導電ペーストを加熱して、バインターを分解させると共に金属を焼結させて貫通電極を形成してもよい。あるいは、貫通孔に、銀や銅等の金属粉を圧入した後、金属粉を加熱して金属を焼結させて貫通電極を形成してもよい。

【符号の説明】

【0120】

1…積層チップパッケージ、2…本体、10…階層部分、20…貫通孔、21…貫通電極、30…半導体チップ、31…配線、32…導体。

【技術分野】

【0001】

本発明は、積層された複数の半導体チップを含む積層チップパッケージおよびその製造方法、ならびに積層チップパッケージの製造に用いられる基礎構造物に関する。

【背景技術】

【0002】

近年、携帯電話やノート型パーソナルコンピュータに代表される携帯機器では、軽量化と高性能化が求められている。それに伴い、携帯機器に用いられる電子部品の高集積化が求められている。また、デジタルカメラや映像記録装置等の画像・映像関連機器の発達に伴い、半導体メモリの大容量化、高集積化が求められている。

【0003】

近年、高集積化された電子部品として、システム・イン・パッケージ(System in Package;以下、SiPと記す。)、特に複数の半導体チップを積層する3次元実装技術を用いたSiPが注目されている。本出願において、積層された複数の半導体チップ(以下、単にチップとも記す。)を含むパッケージを、積層チップパッケージと呼ぶ。この積層チップパッケージには、高集積化が可能になるという利点に加え、配線の長さの短縮が可能になることから、回路の動作の高速化や配線の浮遊容量の低減が可能になるという利点がある。

【0004】

積層チップパッケージを製造するための3次元実装技術の主なものには、基板上に複数のチップを積層し、各チップに形成された複数の電極と、基板に形成された外部接続端子とを、ワイヤボンディングによって接続するワイヤボンディング方式と、積層される各チップにそれぞれ複数の貫通電極を形成し、この貫通電極によってチップ間の配線を行う貫通電極方式とがある。

【0005】

特許文献1には、貫通電極方式を用いて構成された積層メモリが記載されている。

【0006】

特許文献2には、積層された複数のチップ間の配線を、貫通電極に類似した配線プラグを用いて行うようにした3次元積層型半導体装置が記載されている。この3次元積層型半導体装置は、積層された複数のユニット半導体装置を含んでいる。1つのユニット半導体装置は、チップ電極を有する半導体チップと、配線パターンと、モールドレジンと、配線プラグとを備えている。配線パターンの一方の面には、チップ電極がマウントされている。モールドレジンは、半導体チップおよび配線パターンを覆っている。配線プラグは、モールドレジンを半導体チップの外側で貫通している。配線プラグの一端は配線パターンの一方の面に接触し、配線プラグの他端はモールドレジンから露出している。配線パターンの他方の面は、モールドレジンの表面に露出している。この3次元積層型半導体装置では、下段のユニット半導体装置の配線プラグを上段のユニット半導体装置の配線パターンの露出面に接触させることによって、複数の半導体チップ間の配線を行っている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2008−187061号公報

【特許文献2】特開2003−163324号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

ワイヤボンディング方式では、ワイヤ同士の接触を避けるために電極の間隔を小さくすることが難しいという問題点や、ワイヤの高い抵抗値が回路の高速動作の妨げになるという問題点がある。

【0009】

貫通電極方式では、上記のワイヤボンディング方式における問題点は解消される。しかし、従来の貫通電極方式では、チップに貫通電極を形成するために多くの工程が必要であることから、積層チップパッケージのコストが高くなるという問題点がある。すなわち、従来の貫通電極方式では、チップに貫通電極を形成するために、後に切断されることによって複数のチップとなるウェハに、複数の貫通電極用の複数の穴を形成し、次に、この複数の穴内およびウェハの上面上に絶縁層とシード層を形成し、次に、めっき法によって複数の穴内にCu等の金属を充填して複数の貫通電極を形成し、次に、余分なシード層を除去するという一連の工程が必要である。

【0010】

特許文献2に記載されている3次元積層型半導体装置では、従来の貫通電極方式における上記の問題点と同様に、配線プラグを形成するために多くの工程が必要であり、その結果、コストが高くなるという問題点がある。

【0011】

本発明はかかる問題点に鑑みてなされたもので、その目的は、積層された複数の半導体チップを含む積層チップパッケージを、低コストで短時間に大量生産できるようにした積層チップパッケージおよびその製造方法、ならびに積層チップパッケージの製造に用いられる基礎構造物を提供することにある。

【課題を解決するための手段】

【0012】

本発明の積層チップパッケージは、本体と複数の貫通電極とを備えている。本体は、積層された複数の階層部分と、それぞれ複数の階層部分の全てを貫通する複数の貫通孔とを含んでいる。複数の貫通電極は、本体における複数の貫通孔内に設けられて複数の階層部分の全てを貫通している。複数の階層部分の各々は半導体チップを含んでいる。複数の階層部分のうちの少なくとも1つは、半導体チップと複数の貫通電極とを電気的に接続する配線を含んでいる。

【0013】

本発明の積層チップパッケージにおいて、配線は、複数の貫通電極にそれぞれ電気的に接続された複数の導体を含み、複数の導体は、それぞれ、複数の貫通孔の壁面に現れて貫通電極の外面に接触する端面を有していてもよい。この場合、複数の導体は、それぞれ、複数の貫通電極が通過する電極通過孔を有し、電極通過孔の壁面が上記端面を構成していてもよい。

【0014】

また、本発明の積層チップパッケージにおいて、複数の階層部分の各々は、半導体チップを貫通するように形成された複数の絶縁材充填孔と、複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含み、複数の貫通孔は、複数の階層部分の絶縁層を貫通していてもよい。この場合、絶縁材は、主成分として樹脂を含んでいてもよい。絶縁材は、更に、樹脂に混合された絶縁性の粒状物を含んでいてもよい。

【0015】

また、本発明の積層チップパッケージにおいて、複数の階層部分は、1つ以上の第1の種類の階層部分と、1つ以上の第2の種類の階層部分とを含んでいてもよい。第1の種類の階層部分における半導体チップは正常に動作するものであり、第2の種類の階層部分における半導体チップは正常に動作しないものである。また、第1の種類の階層部分は配線を含むが、第2の種類の階層部分は配線を含まない。

【0016】

また、本発明の積層チップパッケージにおいて、複数の階層部分の各々は、半導体チップの周囲に形成された絶縁層を含み、複数の貫通孔は、複数の階層部分の絶縁層を貫通していてもよい。

【0017】

本発明の積層チップパッケージの製造方法は、

本体となる部分である本体形成部分を少なくとも1つ備え、本体形成部分は、複数の階層部分と、複数の貫通電極が設けられていない状態の複数の貫通孔とを含む基礎構造物を作製する工程と、

基礎構造物の本体形成部分における複数の貫通孔内に複数の貫通電極を形成する工程とを備えている。

【0018】

本発明の積層チップパッケージの製造方法において、基礎構造物は、少なくとも1つの本体形成部分として、複数の階層部分が積層された方向に直交する方向に配列された複数の本体形成部分を備えていてもよい。この場合、積層チップパッケージの製造方法は、更に、複数の貫通電極を形成する工程の後で、複数の本体形成部分を互いに分離して複数の本体を形成する工程を備えていてもよい。

【0019】

また、本発明の積層チップパッケージの製造方法において、複数の貫通電極は、めっき法によって形成されてもよい。

【0020】

また、本発明の積層チップパッケージの製造方法において、配線は、複数の貫通電極にそれぞれ電気的に接続された複数の導体を含み、複数の導体は、それぞれ、複数の貫通孔の壁面に現れて貫通電極の外面に接触する端面を有していてもよい。この場合、複数の導体は、それぞれ、複数の貫通電極が通過する電極通過孔を有し、電極通過孔の壁面が上記端面を構成していてもよい。

【0021】

また、本発明の積層チップパッケージの製造方法において、基礎構造物を作製する工程は、後に複数の貫通孔が形成されることによって基礎構造物となる初期基礎構造物を作製する工程と、初期基礎構造物に複数の貫通孔を形成して、基礎構造物を形成する工程とを含んでいてもよい。

【0022】

初期基礎構造物は、複数の貫通孔が形成される前の複数の階層部分である複数の初期階層部分を含んでいる。複数の初期階層部分の各々は、半導体チップを貫通するように形成された複数の絶縁材充填孔と、複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含んでいてもよい。この場合、基礎構造物を形成する工程において、複数の貫通孔は、複数の初期階層部分の絶縁層を貫通するように形成されてもよい。絶縁材は、主成分として樹脂を含んでいてもよい。絶縁材は、更に、樹脂に混合された絶縁性の粒状物を含んでいてもよい。

【0023】

複数の初期階層部分の各々が、上記の複数の絶縁材充填孔と絶縁層とを含んでいる場合において、基礎構造物は、少なくとも1つの本体形成部分として、複数の階層部分が積層された方向に直交する方向に配列された複数の本体形成部分を備えていてもよい。この場合、初期基礎構造物を作製する工程は、それぞれ、各々が本体に含まれる半導体チップのいずれかとなる予定の、配列された複数の半導体チップ予定部を含む複数のチップアレイを作製する工程と、複数のチップアレイを積層して初期基礎構造物を形成する工程とを含んでいてもよい。この場合、積層チップパッケージの製造方法は、更に、複数の貫通電極を形成する工程の後で、複数の本体形成部分を互いに分離して複数の本体を形成する工程を備えていてもよい。

【0024】

複数のチップアレイを作製する工程は、1つのチップアレイを作製するための一連の工程として、

互いに反対側を向いた第1および第2の面を有すると共に、配列された複数の半導体チップ予定部を含むアレイ前ウェハを作製する工程と、

アレイ前ウェハに対して、第1の面において開口し、後に複数の絶縁材充填孔となる複数の溝を形成する工程と、

複数の溝内に絶縁材を充填して、アレイ前ウェハの第1および第2の面に対応する第1および第2の面を有する研磨前アレイを形成する工程と、

複数の溝が複数の絶縁材充填孔となるように、研磨前アレイに対して、複数の溝が露出するまで、研磨前アレイの第2の面から研磨を行う工程とを含んでいてもよい。

【0025】

また、基礎構造物が複数の本体形成部分を備えている場合、複数の本体形成部分のうちの少なくとも1つにおける複数の階層部分は、1つ以上の第1の種類の階層部分と、1つ以上の第2の種類の階層部分とを含んでいてもよい。第1の種類の階層部分における半導体チップは正常に動作するものであり、第2の種類の階層部分における半導体チップは正常に動作しないものである。また、第1の種類の階層部分は配線を含むが、第2の種類の階層部分は配線を含まない。この場合、複数のチップアレイを作製する工程は、複数の半導体チップ予定部について、正常に動作する半導体チップ予定部と正常に動作しない半導体チップ予定部とを判別する工程と、正常に動作しない半導体チップ予定部では配線を形成することなく、正常に動作する半導体チップ予定部では配線を形成する工程とを含んでいてもよい。

【0026】

また、本発明の積層チップパッケージの製造方法において、初期基礎構造物は、複数の貫通孔が形成される前の複数の階層部分である複数の初期階層部分を含み、複数の初期階層部分の各々は、半導体チップの周囲に形成された絶縁層を含んでいてもよい。この場合、基礎構造物を形成する工程において、複数の貫通孔は、複数の初期階層部分の絶縁層を貫通するように形成されてもよい。

【0027】

本発明の基礎構造物は、積層チップパッケージを製造するために用いられるものである。この基礎構造物は、本体となる部分である本体形成部分を少なくとも1つ備えている。本体形成部分は、複数の階層部分と、複数の貫通電極が設けられていない状態の複数の貫通孔とを含んでいる。本発明の基礎構造物は、後に本体形成部分における複数の貫通孔内に複数の貫通電極が形成されるものである。

【0028】

本発明の基礎構造物は、少なくとも1つの本体形成部分として、複数の階層部分が積層された方向に直交する方向に配列された複数の本体形成部分を備えていてもよい。この場合、複数の本体形成部分は、複数の貫通電極が形成された後に、互いに分離されて複数の本体となる。複数の本体形成部分のうちの少なくとも1つにおける複数の階層部分は、1つ以上の第1の種類の階層部分と、1つ以上の第2の種類の階層部分とを含んでいてもよい。第1の種類の階層部分における半導体チップは正常に動作するものであり、第2の種類の階層部分における半導体チップは正常に動作しないものである。また、第1の種類の階層部分は配線を含むが、第2の種類の階層部分は配線を含まない。

【0029】

また、本発明の基礎構造物において、配線は、複数の貫通電極が形成されたときに複数の貫通電極にそれぞれ電気的に接続される複数の導体を含み、複数の導体は、それぞれ、複数の貫通孔の壁面に現れて貫通電極の外面に接触する端面を有していてもよい。この場合、複数の導体は、それぞれ、複数の貫通電極が形成されたときに複数の貫通電極が通過する電極通過孔を有し、電極通過孔の壁面が上記端面を構成していてもよい。

【0030】

また、本発明の基礎構造物において、基礎構造物に含まれる複数の階層部分の各々は、半導体チップを貫通するように形成された複数の絶縁材充填孔と、複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含み、複数の貫通孔は、複数の階層部分の絶縁層を貫通していてもよい。この場合、絶縁材は、主成分として樹脂を含んでいてもよい。絶縁材は、更に、樹脂に混合された絶縁性の粒状物を含んでいてもよい。

【0031】

また、本発明の基礎構造物において、基礎構造物に含まれる複数の階層部分の各々は、半導体チップの周囲に形成された絶縁層を含み、複数の貫通孔は、複数の階層部分の絶縁層を貫通していてもよい。

【発明の効果】

【0032】

本発明の積層チップパッケージまたはその製造方法、あるいは基礎構造物によれば、複数の階層部分の全てを貫通する複数の貫通孔内に、複数の階層部分の全てを貫通する複数の貫通電極を形成することによって、少ない工程数で、複数の貫通電極を備えた積層チップパッケージを製造することが可能になる。従って、本発明によれば、積層チップパッケージを、低コストで短時間に大量生産することが可能になるという効果を奏する。

【図面の簡単な説明】

【0033】

【図1】本発明の第1の実施の形態に係る積層チップパッケージの斜視図である。

【図2】下面側から見た図1の積層チップパッケージを示す斜視図である。

【図3】図1における1つの階層部分を示す斜視図である。

【図4】図1に示した積層チップパッケージの断面図である。

【図5】半導体チップに含まれるデバイスの一部を示す断面図である。

【図6】本発明の第1の実施の形態に係る積層チップパッケージの製造方法における一工程で作製されるアレイ前ウェハを示す平面図である。

【図7】図6に示したアレイ前ウェハの一部を示す断面図である。

【図8】図6に示した工程に続く工程を示す断面図である。

【図9】図8に示した工程に続く工程を示す断面図である。

【図10】図9に示した工程に続く工程を示す断面図である。

【図11】図10に示した工程に続く工程を示す断面図である。

【図12】図11に示した工程に続く工程を示す断面図である。

【図13】図12に示した工程に続く工程を示す断面図である。

【図14】図13に示した工程で作製される初期基礎構造物を示す斜視図である。

【図15】図13に示した工程に続く工程で作製される基礎構造物の一部を示す断面図である。

【図16】図15に示した基礎構造物における配線の一部を示す斜視図である。

【図17】図15に示した工程に続く工程を示す断面図である。

【図18】図17に示した工程で形成される貫通電極を示す斜視図である。

【図19】図17に示した工程の変形例を示す斜視図である。

【図20】本発明の第1の実施の形態における、複数の本体形成部分を分離して複数の本体を形成する工程を示す説明図である。

【図21】本発明の第2の実施の形態に係る積層チップパッケージの斜視図である。

【図22】本発明の第2の実施の形態における配線および貫通電極の一部を示す斜視図である。

【図23】本発明の第3の実施の形態に係る積層チップパッケージの斜視図である。

【図24】図23における1つの階層部分を示す斜視図である。

【図25】図23に示した積層チップパッケージの断面図である。

【図26】本発明の第3の実施の形態に係る積層チップパッケージの製造方法における一工程を示す断面図である。

【図27】図26に示した工程に続く工程を示す断面図である。

【図28】図27に示した工程に続く工程を示す断面図である。

【図29】図28に示した工程に続く工程を示す断面図である。

【図30】図29に示した工程に続く工程を示す断面図である。

【図31】図30に示した工程に続く工程を示す断面図である。

【図32】図31に示した工程に続く工程を示す断面図である。

【発明を実施するための形態】

【0034】

[第1の実施の形態]

以下、本発明の実施の形態について図面を参照して詳細に説明する。始めに、図1ないし図4を参照して、本発明の第1の実施の形態に係る積層チップパッケージの構成について説明する。図1は、本実施の形態に係る積層チップパッケージの斜視図である。図2は、下面側から見た図1の積層チップパッケージを示す斜視図である。図3は、図1における1つの階層部分を示す斜視図である。図4は、図1に示した積層チップパッケージの断面図である。

【0035】

図1、図2および図4に示したように、本実施の形態に係る積層チップパッケージ1は、ほぼ直方体形状の本体2を備えている。本体2は、上面2a、下面2bおよび4つの側面2c,2d,2e,2fを有している。本体2は、積層された複数の階層部分10を含んでいる。図1および図2には、一例として、本体2が、8つの階層部分10を含んでいる例を示している。しかし、本体2に含まれる階層部分10の数は8つに限らず、複数であればよい。上下に隣接する2つの階層部分10は、絶縁性の樹脂よりなる接着剤によって接合されている。

【0036】

積層チップパッケージ1は、更に、本体2の上面2aに配置された複数の端子4と、本体2の下面2bに配置された複数の端子5とを備えている。なお、積層チップパッケージ1は、複数の端子4と複数の端子5の一方のみを備えていてもよい。

【0037】

図4に示したように、本体2は、更に、本体2に含まれる複数の階層部分10の全てを貫通する複数の貫通孔20を含んでいる。積層チップパッケージ1は、更に、本体2における複数の貫通孔20内に設けられて複数の階層部分10の全てを貫通する複数の貫通電極21を備えている。貫通電極21は、例えばCu、Au、Ni、CrまたはZnによって形成されている。

【0038】

図3および図4に示したように、複数の階層部分10の各々は半導体チップ30を含んでいる。半導体チップ30は、上面、下面および4つの側面を有している。半導体チップ30の4つの側面は、それぞれ、本体2の側面2c,2d,2e,2fにおいて露出している。

【0039】

図3および図4には示していないが、複数の階層部分10の各々は、半導体チップ30を貫通するように形成された複数の絶縁材充填孔と、この複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含んでいる。そして、複数の貫通孔20は、複数の階層部分10の絶縁層を貫通している。複数の絶縁材充填孔と絶縁層については、後で詳しく説明する。

【0040】

本体2に含まれる複数の階層部分10のうちの少なくとも1つは、半導体チップ30と複数の貫通電極21とを電気的に接続する配線31を含んでいる。配線31は、複数の貫通電極21にそれぞれ電気的に接続された複数の導体32を含んでいる。複数の導体32は、それぞれ、複数の貫通孔20の壁面に現れて貫通電極21の外面に接触する端面を有している。導体32は、例えばCuによって形成されている。

【0041】

本体2に含まれる複数の階層部分10のうちの他の少なくとも1つは、配線31を含まないものであってもよい。以下、配線31を含む階層部分10を第1の種類の階層部分と呼び、符号10Aを付して表す。また、配線31を含まない階層部分10を第2の種類の階層部分と呼び、符号10Bを付して表す。第1の種類の階層部分10Aにおける半導体チップ30は正常に動作するものであり、第2の種類の階層部分10Bにおける半導体チップ30は正常に動作しないものである。以下、正常に動作する半導体チップ30を良品の半導体チップ30と言い、正常に動作しない半導体チップ30を不良の半導体チップ30と言う。図4には、本体2に含まれる複数の階層部分10のうち、上から3番目の階層部分10が第2の種類の階層部分10Bであり、他の7つの階層部分10が第1の種類の階層部分10Aである例を示している。

【0042】

1つの本体2において最も上に配置された階層部分10が第1の種類の階層部分10Aである場合には、複数の端子4は、その階層部分10における複数の導体32のそれぞれの一部によって構成されていてもよいし、複数の導体32に電気的に接続された他の複数の導体によって構成されていてもよい。1つの本体2において最も上に配置された階層部分10が第2の種類の階層部分10Bである場合には、複数の端子4は、本体2の上面2aに位置する複数の貫通電極21の上端部に電気的に接続された複数の導体によって構成される。複数の端子5は、本体2の下面2bに位置する複数の貫通電極21の下端部に電気的に接続された複数の導体によって構成されている。

【0043】

図3では、複数の導体32のうち、複数の端子4となる部分を破線で示している。複数の端子4が、最も上に配置された階層部分10における複数の導体32の一部によって構成されている場合、他の階層部分10における複数の導体32は、図3において破線で示した部分を含んでいてもよいし含んでいなくてもよい。

【0044】

半導体チップ30は、フラッシュメモリ、DRAM、SRAM、MRAM、PROM、FeRAM等のメモリを構成するメモリチップであってもよい。この場合には、複数の半導体チップ30を含む積層チップパッケージ1によって、大容量のメモリを実現することができる。また、本実施の形態に係る積層チップパッケージ1によれば、積層チップパッケージ1に含まれる半導体チップ30の数を変えることにより、64GB(ギガバイト)、128GB、256GB等の種々の容量のメモリを容易に実現することができる。

【0045】

半導体チップ30が複数のメモリセルを有する場合、半導体チップ30が1つ以上の欠陥のあるメモリセルを含んでいても、冗長技術によって正常に動作させることができる場合には、その半導体チップ30は、良品の半導体チップである。

【0046】

半導体チップ30は、メモリチップに限らず、CPU、センサ、センサの駆動回路等の他のデバイスを実現するものであってもよい。本実施の形態に係る積層チップパッケージ1は、特にSiPを実現するのに適している。

【0047】

次に、図5を参照して、半導体チップ30に含まれるデバイスの一例について説明する。ここでは、一例として、半導体チップ30に含まれるデバイスが、メモリを構成する複数のメモリセルを含む回路である場合について説明する。図5は、複数のメモリセルのうちの1つを示している。このメモリセル40は、P型シリコン基板41の表面の近傍に形成されたソース42およびドレイン43を備えている。ソース42およびドレイン43は、共にN型の領域である。ソース42とドレイン43は、これらの間にP型シリコン基板41の一部よりなるチャネルが形成されるように、所定の間隔を開けて配置されている。メモリセル40は、更に、ソース42とドレイン43の間において基板41の表面上に順に積層された絶縁膜44、浮遊ゲート45、絶縁膜46および制御ゲート47を備えている。メモリセル40は、更に、ソース42、ドレイン43、絶縁膜44、浮遊ゲート45、絶縁膜46および制御ゲート47を覆う絶縁層48を備えている。この絶縁層48には、ソース42、ドレイン43、制御ゲート47のそれぞれの上で開口するコンタクトホールが形成されている。メモリセル40は、それぞれ、ソース42、ドレイン43、制御ゲート47の上方の位置で絶縁層48上に形成されたソース電極52、ドレイン電極53、制御ゲート電極57を備えている。ソース電極52、ドレイン電極53、制御ゲート電極57は、それぞれ、対応するコンタクトホールを通して、ソース42、ドレイン43、制御ゲート47に接続されている。

【0048】

次に、本実施の形態に係る積層チップパッケージ1の製造方法について説明する。積層チップパッケージ1の製造方法は、基礎構造物を作製する工程を備えている。後で詳しく説明するが、基礎構造物は、本体2となる部分である本体形成部分を少なくとも1つ備えている。本体形成部分は、複数の階層部分10と、複数の貫通電極21が設けられていない状態の複数の貫通孔20とを含んでいる。積層チップパッケージ1の製造方法は、更に、基礎構造物の本体形成部分における複数の貫通孔20内に複数の貫通電極21を形成する工程を備えている。

【0049】

基礎構造物を作製する工程は、後に複数の貫通孔20が形成されることによって基礎構造物となる初期基礎構造物を作製する工程と、初期基礎構造物に複数の貫通孔20を形成して、基礎構造物を形成する工程とを含んでいる。

【0050】

基礎構造物は、上記の少なくとも1つの本体形成部分として、複数の階層部分10が積層された方向に直交する方向に配列された複数の本体形成部分を備えていてもよい。この場合、積層チップパッケージの製造方法は、更に、複数の貫通電極21を形成する工程の後で、複数の本体形成部分を互いに分離して複数の本体を形成する工程を備える。

【0051】

以下、基礎構造物が、複数の階層部分10が積層された方向に直交する方向に配列された複数の本体形成部分を備える場合を例にとって、積層チップパッケージ1の製造方法について詳しく説明する。まず、図6ないし図14を参照して、初期基礎構造物を作製する工程について詳しく説明する。

【0052】

初期基礎構造物を作製する工程では、まず、各々が本体2に含まれる半導体チップ30となる予定の、配列された複数の半導体チップ予定部30Pを含むアレイ前ウェハ101を作製する。図6は、アレイ前ウェハ101を示す平面図である。図7は、図6に示したアレイ前ウェハ101の一部を示す断面図である。

【0053】

アレイ前ウェハ101を作製する工程では、具体的には、互いに反対側を向いた2つの面を有する1つの半導体ウェハ100における一方の面に処理、例えばウェハプロセスを施すことによって、それぞれデバイスを含む複数の半導体チップ予定部30Pが配列されたアレイ前ウェハ101を作製する。アレイ前ウェハ101において、複数の半導体チップ予定部30Pは一列に配列されていてもよいし、縦方向と横方向にそれぞれ複数個並ぶように、複数列に配列されていてもよい。以下の説明では、アレイ前ウェハ101において、複数の半導体チップ予定部30Pは、縦方向と横方向にそれぞれ複数個並ぶように、複数列に配列されているものとする。半導体ウェハ100としては、例えばシリコンウェハが用いられる。ウェハプロセスとは、半導体ウェハを加工して、複数のチップに分割される前の複数のデバイスを作製するプロセスである。なお、図6は、理解を容易にするために、半導体ウェハ100に比べて半導体チップ予定部30Pを大きく描いている。例えば、半導体ウェハ100が12インチウェハで、半導体チップ予定部30Pの上面の一辺の長さが8〜10mmとすると、1枚の半導体ウェハ100を用いて、700〜900個の半導体チップ予定部30Pを形成することが可能である。

【0054】

図7は、アレイ前ウェハ101における1つの半導体チップ予定部30Pの一部を示している。図7に示したように、半導体チップ予定部30Pは、半導体ウェハ100の一方の面の近傍に形成されたデバイス形成領域33を含んでいる。デバイス形成領域33は、半導体ウェハ100における一方の面に処理を施すことによってデバイスが形成された領域である。図示しないが、半導体チップ予定部30Pは、更に、デバイス形成領域33の上に配置された複数の電極パッドを含んでいる。複数の電極パッドは、デバイス形成領域33に形成されたデバイスに電気的に接続されている。

【0055】

半導体チップ予定部30Pは、更に、デバイス形成領域33および電極パッドを覆う絶縁材料よりなるパッシベーション膜35を含んでいる。パッシベーション膜35は、複数の電極パッドの上面を露出させる複数の開口部35aを有している。以下、アレイ前ウェハ101において、パッシベーション膜35により近い面を第1の面101aと呼び、その反対側の面を第2の面101bと呼ぶ。

【0056】

初期基礎構造物を作製する工程では、次に、ウェハソートテストによって、アレイ前ウェハ101に含まれる複数の半導体チップ予定部30Pについて、正常に動作する半導体チップ予定部と正常に動作しない半導体チップ予定部とを判別する工程が行われる。この工程では、各半導体チップ予定部30Pの複数の電極パッドに試験装置のプローブを接触させて、試験装置によって、半導体チップ予定部30Pが正常に動作するか否かをテストする。図6において、記号“NG”を付した半導体チップ予定部30Pは、正常に動作しない半導体チップ予定部30Pであり、他の半導体チップ予定部30Pは、正常に動作する半導体チップ予定部30Pである。この工程によって、アレイ前ウェハ101毎に、正常に動作する半導体チップ予定部30Pと正常に動作しない半導体チップ予定部30Pの位置情報が得られる。この位置情報は、後で説明する配線31を形成する工程において利用される。

【0057】

図8は、図6に示した工程に続く工程を示す断面図である。この工程では、アレイ前ウェハ101に対して、第1の面101aにおいて開口し、後に複数の絶縁材充填孔となる複数の溝104Pを形成する。溝104Pは、その底部がアレイ前ウェハ101の第2の面101bに達しないように形成される。溝104Pの深さは、例えば50〜70μmの範囲内である。後に形成される貫通孔20は溝104Pの中を通る。従って、アレイ前ウェハ101の第1の面101aに平行な断面において、溝104Pの大きさは貫通孔20よりも大きい。溝104Pは、その中を複数の貫通孔20が通るものであってもよい。図8において、左側の溝104Pは、後に1つの貫通孔20が通るものであり、右側の溝104Pは、後に複数、例えば4つの貫通孔20が通るものである。上記断面における溝104Pの径は、例えば1.0〜90.0μmの範囲内である。図8には、上記断面における溝104Pの形状が矩形である例を示している。しかし、上記断面における溝104Pの形状は、矩形に限らず、円形、楕円形等でもよい。溝104Pは、例えば、エッチング液としてKOHを用いたウェットエッチングや、Cl2系のエッチングガスを用いた反応性イオンエッチングによって形成される。このようにして、複数の溝104Pが形成された後のアレイ前ウェハ101よりなる研磨前アレイ本体105が作製される。

【0058】

図9は、図8に示した工程に続く工程を示している。この工程では、研磨前アレイ本体105の複数の溝104P内に絶縁材を充填して、この絶縁材よりなる絶縁層106を形成すると共に、パッシベーション膜35の上面と絶縁層106の上面を平坦化する。このようにして、研磨前アレイ本体105と絶縁層106とを含む研磨前アレイ109が作製される。研磨前アレイ109は、アレイ前ウェハ101の第1の面101aに対応する第1の面109aと、アレイ前ウェハ101の第2の面101bに対応する第2の面109bとを有している。

【0059】

絶縁層106に用いられる絶縁材は、主成分として、ポリイミド樹脂等の樹脂を含んでいることが好ましい。ここで、主成分とは、50重量%以上の成分をいう。絶縁材は、更に、樹脂に加えて、樹脂に混合された絶縁性の粒状物を含んでいてもよい。絶縁性の粒状物は、例えばSiO2やAl2O3によって形成される。絶縁性の粒状物は、絶縁層106に発生する応力を緩和すると共に、絶縁層106の強度を増加させる役割を有する。

【0060】

絶縁層106の形成は、例えば以下の方法によって行われる。この方法では、まず、硬化前の樹脂を含む流動性の絶縁材を、複数の溝104P内に埋め込む。次に、例えば150〜250℃の範囲内の温度で絶縁材を熱処理(キュア)することによって、絶縁材を硬化させて絶縁層106とすると共に絶縁層106の上面を平坦化する。この方法において、流動性の絶縁材は、硬化前の樹脂に加えて、樹脂に混合された絶縁性の粒状物を含んでいてもよい。この場合、絶縁層106は、硬化後の樹脂と、この樹脂に混合された絶縁性の粒状物とを含むことになる。

【0061】

絶縁層106の形成は、上記の方法の代りに、例えば以下の方法によって行ってもよい。この方法では、硬化前の樹脂にスピンオングラス膜の原材料液を混合してなる流動性の絶縁材を、図8に示した研磨前アレイ本体105の上面上に塗布して、複数の溝104P内へ絶縁材を充填すると共に、パッシベーション膜35の上面と絶縁材の表面を平坦化する。次に、熱処理によって絶縁材を硬化させて絶縁層106とする。この場合、スピンオングラス膜の原材料液中のガラス成分が、絶縁層106において、樹脂に混合された絶縁性の粒状物になる。

【0062】

図10は、図9に示した工程に続く工程を示している。この工程では、前述の正常に動作する半導体チップ予定部30Pと正常に動作しない半導体チップ予定部30Pの位置情報に基づいて、正常に動作しない半導体チップ予定部30Pでは配線31(複数の導体32)を形成することなく、正常に動作する半導体チップ予定部30Pでは配線31(複数の導体32)を形成する。この工程は、例えば、フォトリソグラフィによりフォトレジスト層をパターニングすることによって、複数の開口部を有するフレームを形成する工程と、このフレームの複数の開口部に収容されるように、例えばめっき法によって複数の導体32を形成する工程とを含んでいる。複数の導体32は、パッシベーション膜35の複数の開口部35aを通って、デバイス形成領域33の上に配置された複数の電極パッドに電気的に接続される。絶縁層106の形成の際に、パッシベーション膜35の複数の開口部35aにも絶縁材が充填された場合には、複数の導体32を形成する前に、パッシベーション膜35の複数の開口部35aに充填された絶縁材を除去する。

【0063】

複数の導体32は、それぞれ、後に複数の貫通電極21が形成されたときに複数の貫通電極21が通過する電極通過孔32aを有している。電極通過孔32aの壁面は、貫通孔20の壁面に現れて、後に貫通電極21の外面に接触する。従って、電極通過孔32aの壁面は、貫通電極21の外面に接触する導体32の端面を構成する。

【0064】

電極通過孔32aは、絶縁層106の上面上に位置する。電極通過孔32aの径は、溝104Pの径よりも小さい。複数の貫通電極21が形成されたときに、電極通過孔32aの壁面が、その電極通過孔32aを通過する貫通電極21の外面に接触する。図10における左側の絶縁層106の上面上には、1つの導体32の1つの電極通過孔32aのみが位置している。図10における右側の絶縁層106の上面上には、4つの導体32の4つの電極通過孔32aが位置している。

【0065】

図11は、図10に示した工程に続く工程を示している。この工程では、まず、研磨前アレイ109の第1の面109aが、図11に示した板状の治具112の一方の面に対向するように、絶縁性の樹脂よりなる接着剤によって、研磨前アレイ109を治具112に張り付ける。以下、この治具112に貼り付けられた研磨前アレイ109を、第1の研磨前アレイ109と呼ぶ。図11において、符号113は、接着剤によって形成された絶縁層を示している。

【0066】

次に、第1の研磨前アレイ109における第2の面109bを研磨する。この研磨は、複数の溝104Pが露出するまで行う。この研磨により、複数の溝104Pは、複数の絶縁材充填孔104となる。また、第1の研磨前アレイ109における第2の面109bを研磨することにより、第1の研磨前アレイ109が薄くされて、治具112に張り付けられた状態のチップアレイ110が形成される。このチップアレイ110の厚みは、例えば20〜60μmの範囲内である。チップアレイ110は、配列された複数の半導体チップ予定部30Pを含んでいる。以下、治具112に張り付けられたチップアレイ110を、第1のチップアレイ110と呼ぶ。第1のチップアレイ110は、第1の研磨前アレイ109の第1の面109aに対応する第1の面110aと、その反対側の第2の面110bとを有している。第2の面110bは、研磨された面である。

【0067】

図12は、図11に示した工程に続く工程を示している。この工程では、まず、治具112に張り付けられた第1のチップアレイ110に、絶縁性の樹脂よりなる接着剤によって、研磨前アレイ109を張り付ける。この研磨前アレイ109は、第1の面109aが、第1のチップアレイ110の研磨された面すなわち第2の面110bに対向するように、第1のチップアレイ110に張り付けられる。以下、第1のチップアレイ110に張り付けられる研磨前アレイ109を、第2の研磨前アレイ109と呼ぶ。第1のチップアレイ110と第2の研磨前アレイ109とを接着する接着剤は絶縁層113となる。

【0068】

次に、図示しないが、第2の研磨前アレイ109における第2の面109bを研磨する。この研磨は、複数の溝104Pが露出するまで行う。この研磨により、複数の溝104Pは、複数の絶縁材充填孔104となる。第2の研磨前アレイ109における第2の面109bを研磨することにより、第2の研磨前アレイ109が薄くされて、第1のチップアレイ110に張り付けられた状態の第2のチップアレイ110が形成される。第2のチップアレイ110の厚みは、第1のチップアレイ110と同様に、例えば20〜60μmの範囲内である。

【0069】

図13は、図12に示した工程に続く工程を示している。この工程では、まず、図12に示した工程と同様の工程を繰り返し行って、所定の数のチップアレイ110の積層体を形成する。図13には、8つのチップアレイ110の積層体を形成した例を示している。次に、チップアレイ110の積層体を治具112から分離する。次に、チップアレイ110の積層体において最も上に配置されたチップアレイ110において、エッチングまたは研磨によって絶縁層113の一部を除去して、複数の導体32を露出させる。この露出した複数の導体32のそれぞれの一部は、複数の端子4を構成する。このようにして、積層された複数のチップアレイ110を含む初期基礎構造物115が形成される。図14は、初期基礎構造物115を示す斜視図である。

【0070】

各チップアレイ110は、配列された複数の半導体チップ予定部30Pを含んでいる。初期基礎構造物115は、複数の階層部分10が積層された方向に直交する方向に配列された複数の初期本体部分2Pを含んでいる。初期本体部分2Pは、後に複数の貫通孔20が形成されることによって本体形成部分となる部分である。

【0071】

図13は、初期基礎構造物115に含まれる複数の初期本体部分2Pのうちの1つにおける一部を示している。図13に示したように、初期本体部分2Pは、複数の貫通孔20が形成される前の積層された複数の階層部分10である積層された複数の初期階層部分10Pを含んでいる。複数の初期階層部分10Pの各々は、半導体チップ予定部30Pを含んでいる。以下の説明では、初期基礎構造物115の形成後における半導体チップ予定部30Pを半導体チップ30とする。複数の初期階層部分10Pの各々は、半導体チップ30を貫通するように形成された複数の絶縁材充填孔104と、この複数の絶縁材充填孔104内に充填された絶縁材よりなる絶縁層106とを含んでいる。なお、絶縁層113は、その下に位置する初期階層部分10Pの構成要素とする。

【0072】

初期基礎構造物115に含まれる複数の初期本体部分2Pの全てが、正常に動作しない半導体チップ30を含まないものであってもよい。あるいは、複数の初期本体部分2Pのうちの少なくとも1つは、正常に動作する半導体チップ30と正常に動作しない半導体チップ30とを、それぞれ1つ以上含むものであってもよい。

【0073】

次に、図15および図16を参照して、初期基礎構造物115を用いて基礎構造物を形成する工程について説明する。図15は、図13に示した工程に続く工程で作製される基礎構造物の一部を示す断面図である。図16は、図15に示した基礎構造物における配線の一部を示す斜視図である。この工程では、初期基礎構造物115の複数の初期本体部分2Pのそれぞれに対して複数の貫通孔20を形成する。これにより、初期本体部分2Pは本体形成部分2Qとなり、初期基礎構造物115は基礎構造物120となる。基礎構造物120は、複数の階層部分10が積層された方向に直交する方向に配列された複数の本体形成部分2Qを備えている。図15は、基礎構造物120に含まれる複数の本体形成部分2Qのうちの1つにおける一部を示している。

【0074】

基礎構造物120に含まれる複数の本体形成部分2Qの全てが、正常に動作しない半導体チップ30を含まないものであってもよい。あるいは、複数の本体形成部分2Qのうちの少なくとも1つは、正常に動作する半導体チップ30と正常に動作しない半導体チップ30とを、それぞれ1つ以上含むものであってもよい。

【0075】

図15に示したように、複数の貫通孔20は、複数のチップアレイ110(初期階層部分10P)が積層された方向に並ぶ複数の絶縁層106を貫通するように形成される。図15における左側の絶縁層106では1つの貫通孔20が貫通し、図15における右側の絶縁層106では4つの貫通孔20が貫通している。前述のように、複数の導体32の各々は、後に複数の貫通電極21が形成されたときに複数の貫通電極21のいずれかが通過する電極通過孔32aを有している。図15および図16に示したように、1つの貫通孔20は、複数のチップアレイ110(初期階層部分10P)が積層された方向に並ぶ複数の導体32の電極通過孔32aを通り、基礎構造物120(本体形成部分2Q)を貫通するように形成される。貫通孔20の径は、電極通過孔32aの径と等しく、絶縁材充填孔104の径よりも小さい。そのため、図15に示したように、貫通孔20を形成した後には、絶縁材充填孔104内において、貫通孔20の周囲に、当初の絶縁層106のうちの一部が残る。

【0076】

複数の貫通孔20の形成は、例えばレーザ加工を用いて行うことができる。絶縁層106が、主成分として樹脂を含む絶縁材によって形成されている場合には、レーザ加工によって、容易に且つ短時間で複数の貫通孔20を形成することができる。

【0077】

次に、図17ないし図19を参照して、基礎構造物120の本体形成部分2Qにおける複数の貫通孔20内に複数の貫通電極21を形成する工程について説明する。図17は、図15に示した工程に続く工程を示す断面図である。図18は、図17に示した工程で形成される貫通電極21を示す斜視図である。図19は、図17に示した工程の変形例を示す斜視図である。

【0078】

この工程では、例えばめっき法によって、複数の貫通孔20内に複数の貫通電極21を形成する。この工程では、まず、図17に示したように、基礎構造物120における最も下のチップアレイ110の下面に、めっき用のシード層141を接合する。シード層141は、Cu等の金属によって構成されている。シード層141は、樹脂等よりなる板142によって保持された金属膜であってもよい。あるいは、シード層141は、金属板であってもよい。この場合には、シード層141を保持する板142は不要である。

【0079】

次に、電気めっき法によって、基礎構造物120の複数の貫通孔20内に、それぞれ、めっき膜よりなる複数の貫通電極21を形成する。このとき、シード層141は通電され、めっき膜は、シード層141の表面から成長して、貫通孔20を埋める。

【0080】

図18は、複数のチップアレイ110が積層された方向に並ぶ複数の導体32と1つの貫通電極21を示している。前述のように、複数の導体32の各々は、複数の貫通電極21のいずれかが通過する電極通過孔32aを有している。複数の貫通電極21が形成されたときに、電極通過孔32aの壁面は、その電極通過孔32aを通過する貫通電極21の外面に接触する。これにより、導体32は貫通電極21に電気的に接続され、複数の導体32を含む配線31によって、半導体チップ30と複数の貫通電極21とが電気的に接続される。

【0081】

ここで、図19を参照して、図17に示した工程の変形例について説明する。この変形例では、電気めっき法によって複数の貫通電極21を形成する前に、無電解めっき法によって、基礎構造物120の複数の貫通孔20のそれぞれの壁面に金属膜よりなるシード層151を形成する。その後、電気めっき法によって、基礎構造物120の複数の貫通孔20内に、それぞれめっき膜を形成する。このとき、シード層151は通電され、めっき膜は、シード層151の表面から成長して、貫通孔20を埋める。この変形例では、シード層151とめっき膜とによって貫通電極21が構成される。この変形例の代わりに、無電解めっき法のみを用いて、複数の貫通電極21を形成してもよい。

【0082】

本体2の下面2bに配置された複数の端子5を備えた積層チップパッケージ1を製造する場合には、複数の貫通電極21を形成した後に、基礎構造物120の複数の本体形成部分2Qの下面に、例えばめっき法によって、複数の端子5を形成する。

【0083】

次に、図20を参照して、複数の貫通電極21を形成する工程の後で、基礎構造物120の複数の本体形成部分2Qを分離して複数の本体2を形成する工程について説明する。図20において、(a)は、1つの基礎構造物120を示している。この基礎構造物120は、複数の階層部分10が積層された方向に直交する方向に配列された複数の本体形成部分2Qを備えている。この工程では、基礎構造物120の複数の本体形成部分2Qが互いに分離されて複数の本体2が形成されるように、基礎構造物120を切断する。図20における(b)は、このようにして形成された複数の本体2のうちの1つを示している。上記のように基礎構造物120を切断することにより、複数の貫通孔20と複数の貫通電極21が形成された後の初期階層部分10Pは階層部分10となる。本体2は、積層された複数の階層部分10を含み、複数の階層部分10の各々は半導体チップ30を含んでいる。

【0084】

以上、図6ないし図20を参照して説明した一連の工程により、積層チップパッケージ1が複数個作製される。ここまでは、図13に示したように8つのチップアレイ110を含む初期基礎構造物115を用いて、8つの階層部分10を含む積層チップパッケージ1を複数個作製する例について説明してきた。しかし、本実施の形態では、初期基礎構造物115に含まれるチップアレイ110の数を変えることによって、階層部分10の数の異なる複数種類の積層チップパッケージ1を作製することができる。

【0085】

以上説明したように、本実施の形態に係る積層チップパッケージ1およびその製造方法、ならびに基礎構造物120によれば、積層された複数の階層部分10の全てを貫通する複数の貫通孔20内に、複数の階層部分10の全てを貫通する複数の貫通電極21を形成することによって、少ない工程数で、複数の貫通電極を備えた積層チップパッケージを製造することが可能になる。従って、本実施の形態によれば、積層チップパッケージ1を、低コストで短時間に大量生産することが可能になる。

【0086】

ところで、従来の貫通電極方式を用いた積層チップパッケージでは、積層された複数の階層部分の各々に複数の貫通電極が形成され、下側の階層部分における複数の貫通電極と上側の階層部分における複数の貫通電極とが電気的に接続される。この場合、下側の階層部分における複数の貫通電極と上側の階層部分における複数の貫通電極との間における位置ずれや抵抗の増加により、複数の半導体チップ間の電気的接続の信頼性が低下するおそれがある。

【0087】

これに対し、本実施の形態では、積層チップパッケージ1が複数の階層部分10の全てを貫通する複数の貫通電極21を備えるため、上述のような問題は生じない。そのため、本実施の形態によれば、複数の半導体チップ30間の電気的接続の信頼性を向上させることができる。

【0088】

また、本実施の形態において、図18に示したように、配線31の複数の導体32の各々が電極通過孔32aを有し、電極通過孔32aの壁面が、その電極通過孔32aを通過する貫通電極21の外面に接触する場合には、導体32と貫通電極21との接触面積を大きくすることができる。これにより、導体32と貫通電極21との電気的接続の信頼性を向上させることができる。

【0089】

ところで、もし、不良の半導体チップ30を含む第2の種類の階層部分10Bにおいても、配線31を介して半導体チップ30と複数の貫通電極21とが電気的に接続されていると、階層部分10Bにおける配線31は、メモリデバイス等、積層チップパッケージ1によって実現するデバイスにとって不要なキャパシタンスや不要なインダクタンスを発生させたり、良品の半導体チップ30に接続された配線31との間に浮遊容量を発生させたりする。このことは、メモリデバイス等のデバイスの動作の高速化の妨げとなる。

【0090】

これに対し、本実施の形態では、不良の半導体チップ30を含む第2の種類の階層部分10Bでは、半導体チップ30と複数の貫通電極21とを電気的に接続する配線31は設けられない。そのため、積層チップパッケージ1において、不良の半導体チップ30を含む第2の種類の階層部分10Bは、単なる絶縁層とみなすことができる。従って、本実施の形態によれば、不良の半導体チップ30に接続された配線に起因する問題を低減しながら、不良の半導体チップ30を使用不能にすることができる。

【0091】

[第2の実施の形態]

次に、図21および図22を参照して、本発明の第2の実施の形態について説明する。図21は、本実施の形態に係る積層チップパッケージの斜視図である。図22は、本実施の形態における配線および貫通電極の一部を示す斜視図である。

【0092】

図21および図22に示したように、本実施の形態では、配線31の複数の導体32の各々は、第1の実施の形態における電極通過孔32aを有しておらず、代わりに、貫通電極21の外面に接触する端面32bを有している。本実施の形態では、複数の貫通電極21を形成する前の基礎構造物120において、導体32の端面32bは、貫通孔20の壁面に現れている。そして、複数の貫通電極21が形成されたときに、導体32の端面32bは1つの貫通電極21の外面に接触する。これにより、導体32は貫通電極21に電気的に接続される。

【0093】

本実施の形態におけるその他の構成は、第1の実施の形態と同様である。また、本実施の形態における作用および効果は、電極通過孔32aに起因する事項以外は、第1の実施の形態と同様である。

【0094】

[第3の実施の形態]

次に、本発明の第3の実施の形態について説明する。始めに、図23ないし図25を参照して、本実施の形態に係る積層チップパッケージの構成について説明する。図23は、本実施の形態に係る積層チップパッケージの斜視図である。図24は、図23における1つの階層部分を示す斜視図である。図25は、図23に示した積層チップパッケージの断面図である。

【0095】

本実施の形態に係る積層チップパッケージ301は、第1の実施の形態と同様に、ほぼ直方体形状の本体2を備えている。本体2は、上面2a、下面2bおよび4つの側面2c,2d,2e,2fを有している。本実施の形態における本体2は、絶縁性の基体311と、この基体311の上に積層された複数の階層部分10を含んでいる。基体311は、例えば樹脂によって形成されている。図23および図25には、一例として、本体2が、8つの階層部分10を含んでいる例を示している。しかし、本体2に含まれる階層部分10の数は8つに限らず、複数であればよい。上下に隣接する2つの階層部分10は、絶縁性の樹脂よりなる接着剤によって接合されている。

【0096】

積層チップパッケージ301は、更に、本体2の上面2aに配置された複数の端子4と、本体2の下面2bに配置された複数の端子5とを備えている。なお、積層チップパッケージ301は、複数の端子4と複数の端子5の一方のみを備えていてもよい。

【0097】

図24および図25に示したように、本実施の形態における階層部分10は、半導体チップ30と、その周囲に配置された絶縁層312とを含んでいる。絶縁層312は、例えば樹脂によって形成されている。

【0098】

図25に示したように、本体2は、更に、本体2に含まれる複数の階層部分10の全てと基体311とを貫通する複数の貫通孔20を含んでいる。本実施の形態では、複数の貫通孔20は、複数の階層部分10の絶縁層312を貫通している。積層チップパッケージ301は、更に、本体2における複数の貫通孔20内に設けられて複数の階層部分10の全てと基体311とを貫通する複数の貫通電極21を備えている。貫通電極21は、例えばCu、Au、Ni、CrまたはZnによって形成されている。

【0099】

本体2に含まれる複数の階層部分10のうちの少なくとも1つは、半導体チップ30と複数の貫通電極21とを電気的に接続する配線31を含んでいる。配線31は、複数の貫通電極21にそれぞれ電気的に接続された複数の導体32を含んでいる。複数の導体32は、それぞれ、複数の貫通孔20の壁面に現れて貫通電極21の外面に接触する端面を有している。導体32は、例えばCuによって形成されている。本体2に含まれる複数の階層部分10のうちの他の少なくとも1つは、配線31を含まないものであってもよい。

【0100】

図23に示した例では、複数の端子4は、最も上に配置された階層部分10における複数の導体32のそれぞれの一部によって構成されている。しかし、複数の端子4は、複数の導体32に電気的に接続された他の複数の導体によって構成されていてもよい。複数の端子5は、本体2の下面2bに位置する複数の貫通電極21の下端部に電気的に接続されている。

【0101】

図24では、複数の導体32のうち、複数の端子4となる部分を破線で示している。複数の端子4が、最も上に配置された階層部分10における複数の導体32の一部によって構成されている場合、他の階層部分10における複数の導体32は、図24において破線で示した部分を含んでいてもよいし含んでいなくてもよい。

【0102】

次に、図26ないし図32を参照して、本実施の形態に係る積層チップパッケージ301の製造方法について説明する。第1の実施の形態と同様に、積層チップパッケージ301の製造方法は、基礎構造物を作製する工程を備えている。基礎構造物は、本体2となる部分である本体形成部分を少なくとも1つ備えている。本体形成部分は、基体311と、複数の階層部分10と、複数の貫通電極21が設けられていない状態の複数の貫通孔20とを含んでいる。積層チップパッケージ301の製造方法は、更に、基礎構造物の本体形成部分における複数の貫通孔20内に複数の貫通電極21を形成する工程を備えている。

【0103】

基礎構造物を作製する工程は、後に複数の貫通孔20が形成されることによって基礎構造物となる初期基礎構造物を作製する工程と、初期基礎構造物に複数の貫通孔20を形成して、基礎構造物を形成する工程とを含んでいる。

【0104】

以下、基礎構造物が、複数の階層部分10が積層された方向に直交する方向に配列された複数の本体形成部分を備える場合を例にとって、積層チップパッケージ301の製造方法について詳しく説明する。

【0105】

図26は、積層チップパッケージ301の製造方法における一工程を示す断面図である。積層チップパッケージ301の製造方法では、まず、基体311となる基体予定部を複数含む基板を用意し、この基板における複数の基体予定部の上にそれぞれ半導体チップ30を搭載する。図26は、基板のうちの1つの基体予定部311Pと、その上に搭載された半導体チップ30を示している。以下、1つの基体予定部311Pに注目して、積層チップパッケージ301の製造方法について説明する。基体予定部311Pの上に半導体チップ30を搭載する際には、基体予定部311Pの上に金属層を形成した後、その金属層の上に半導体チップ30を接合してもよい。基体予定部311Pの上に搭載された半導体チップ30は、本体2において最も下の階層部分10における半導体チップ30となる。

【0106】

半導体チップ30は、デバイス形成領域33と、デバイス形成領域33の上に配置された複数の電極パッド(図示せず)と、デバイス形成領域33および電極パッドを覆う絶縁材料よりなるパッシベーション膜35とを含んでいる。パッシベーション膜35は、複数の電極パッドの上面を露出させる複数の開口部35aを有している。

【0107】

図27は、図26に示した工程に続く工程を示す断面図である。この工程では、半導体チップ30の周囲における基体予定部311Pの上に絶縁層312を形成し、パッシベーション膜35の上面と絶縁層312の上面を平坦化する。

【0108】

図28は、図27に示した工程に続く工程を示す断面図である。この工程では、パッシベーション膜35および絶縁層312の上に、配線31を構成する複数の導体32を形成する。複数の導体32は、パッシベーション膜35の複数の開口部35aを通って、デバイス形成領域33の上に配置された複数の電極パッドに電気的に接続される。ここでは、第1の実施の形態と同様に、複数の導体32の各々が、後に複数の貫通電極21が形成されたときに複数の貫通電極21のいずれかが通過する電極通過孔32aを有している例を挙げる。ただし、複数の導体32の各々は、第2の実施の形態と同様に、電極通過孔32aを有さず、代りに端面32bを有するものであってもよい。

【0109】

図29は、図28に示した工程に続く工程を示す断面図である。この工程では、配線31(複数の導体32)の覆うように絶縁層313を形成し、この絶縁層313の上面を平坦化する。絶縁層313は、例えば樹脂によって形成される。図26ないし図29に示した一連の工程によって、初期基礎構造物のうち、本体2において最も下の階層部分10に対応する部分が形成される。

【0110】

図30は、図29に示した工程に続く工程を示す断面図である。この工程では、まず、絶縁層313の上に、半導体チップ30を搭載する。この半導体チップ30は、本体2において下から2番目の階層部分10における半導体チップ30となる。絶縁層313の上に半導体チップ30を搭載する際には、絶縁層313の上に金属層を形成した後、その金属層の上に半導体チップ30を接合してもよい。次に、図27ないし図29に示した一連の工程と同様にして、絶縁層312、配線31(複数の導体32)および絶縁層313を形成する。このようにして、初期基礎構造物のうち、本体2において下2番目の階層部分10に対応する部分が形成される。以下、同様の工程を繰り返し行って、初期基礎構造物115を形成する。初期基礎構造物115は、複数の階層部分10が積層された方向に直交する方向に配列された複数の初期本体部分2Pを含んでいる。初期本体部分2Pは、後に複数の貫通孔20が形成されることによって本体形成部分となる部分である。

【0111】

図30は、1つの初期本体部分2Pを示している。初期本体部分2Pは、複数の貫通孔20が形成される前の積層された複数の階層部分10である積層された複数の初期階層部分10Pを含んでいる。複数の初期階層部分10Pの各々は、半導体チップ30と、その周囲に配置された絶縁層312とを含んでいる。なお、絶縁層313は、その下に位置する初期階層部分10Pの構成要素とする。

【0112】

図31は、図30に示した工程に続く工程を示す断面図である。この工程では、初期基礎構造物115の複数の初期本体部分2Pのそれぞれに対して複数の貫通孔20を形成する。これにより、初期本体部分2Pは本体形成部分2Qとなり、初期基礎構造物115は基礎構造物120となる。基礎構造物120は、複数の階層部分10が積層された方向に直交する方向に配列された複数の本体形成部分2Qを備えている。図31は、1つの本体形成部分2Qを示している。

【0113】

本実施の形態では、複数の貫通孔20は、複数の初期階層部分10Pの絶縁層312を貫通するように形成される。また、1つの貫通孔20は、複数の初期階層部分10Pが積層された方向に並ぶ複数の導体32の電極通過孔32aを通り、基礎構造物120(本体形成部分2Q)を貫通するように形成される。複数の貫通孔20の形成方法は、第1の実施の形態と同様である。

【0114】

図32は、図31に示した工程に続く工程を示す断面図である。この工程では、複数の貫通孔20内に複数の貫通電極21を形成する。複数の貫通電極21の形成方法は、第1の実施の形態と同様である。複数の貫通電極21が形成されたときに、電極通過孔32aの壁面は、その電極通過孔32aを通過する貫通電極21の外面に接触する。これにより、導体32は貫通電極21に電気的に接続され、複数の導体32を含む配線31によって、半導体チップ30と複数の貫通電極21とが電気的に接続される。

【0115】

本体2の下面2bに配置された複数の端子5を備えた積層チップパッケージ301を製造する場合には、複数の貫通電極21を形成した後に、基礎構造物120の複数の本体形成部分2Qの下面に、例えばめっき法によって、複数の端子5を形成する。

【0116】

本実施の形態では、次に、第1の実施の形態と同様に、基礎構造物120を切断することによって、基礎構造物120の複数の本体形成部分2Qを分離して複数の本体2を形成する。このとき、基体予定部311Pは基体311となる。

【0117】

本実施の形態におけるその他の構成、作用および効果は、第1または第2の実施の形態と同様である。

【0118】

なお、本発明は、上記実施の形態に限定されず、種々の変更が可能である。例えば、初期基礎構造物の作製方法は、実施の形態に示した方法に限らない。例えば、2つの研磨前アレイ109(図10参照)を、それらの第1の面109a同士が対向するように、絶縁性の樹脂よりなる接着剤によって張り合わせた後、2つの研磨前アレイ109の第2の面109bをそれぞれ研磨して、2つのチップアレイ110の積層体を作製し、この2つのチップアレイ110の積層体を複数個張り合わせて初期基礎構造物を作製してもよい。

【0119】

また、本発明において、貫通電極を形成する方法は、めっき法に限らず、他の方法であってもよい。例えば、貫通孔に、銀や銅等の金属粉とバインダーとを含む導電ペーストを充填した後、導電ペーストを加熱して、バインターを分解させると共に金属を焼結させて貫通電極を形成してもよい。あるいは、貫通孔に、銀や銅等の金属粉を圧入した後、金属粉を加熱して金属を焼結させて貫通電極を形成してもよい。

【符号の説明】

【0120】

1…積層チップパッケージ、2…本体、10…階層部分、20…貫通孔、21…貫通電極、30…半導体チップ、31…配線、32…導体。

【特許請求の範囲】

【請求項1】

積層された複数の階層部分と、それぞれ前記複数の階層部分の全てを貫通する複数の貫通孔とを含む本体と、

前記本体における前記複数の貫通孔内に設けられて前記複数の階層部分の全てを貫通する複数の貫通電極とを備え、

前記複数の階層部分の各々は半導体チップを含み、

前記複数の階層部分のうちの少なくとも1つは、前記半導体チップと前記複数の貫通電極とを電気的に接続する配線を含む積層チップパッケージを製造する方法であって、

前記本体となる部分である本体形成部分を少なくとも1つ備え、前記本体形成部分は、前記複数の階層部分と、前記複数の貫通電極が設けられていない状態の前記複数の貫通孔とを含む基礎構造物を作製する工程と、

前記基礎構造物の前記本体形成部分における前記複数の貫通孔内に前記複数の貫通電極を形成する工程とを備えたことを特徴とする積層チップパッケージの製造方法。

【請求項2】

前記基礎構造物は、前記少なくとも1つの本体形成部分として、前記複数の階層部分が積層された方向に直交する方向に配列された複数の本体形成部分を備え、

前記積層チップパッケージの製造方法は、更に、前記複数の貫通電極を形成する工程の後で、前記複数の本体形成部分を互いに分離して複数の本体を形成する工程を備えたことを特徴とする請求項1記載の積層チップパッケージの製造方法。

【請求項3】

前記複数の貫通電極は、めっき法によって形成されることを特徴とする請求項1記載の積層チップパッケージの製造方法。

【請求項4】

前記配線は、前記複数の貫通電極にそれぞれ電気的に接続された複数の導体を含み、

前記複数の導体は、それぞれ、前記複数の貫通孔の壁面に現れて前記貫通電極の外面に接触する端面を有することを特徴とする請求項1記載の積層チップパッケージの製造方法。

【請求項5】

前記複数の導体は、それぞれ、前記複数の貫通電極が通過する電極通過孔を有し、前記電極通過孔の壁面が前記端面を構成することを特徴とする請求項4記載の積層チップパッケージの製造方法。

【請求項6】

前記基礎構造物を作製する工程は、

後に前記複数の貫通孔が形成されることによって前記基礎構造物となる初期基礎構造物を作製する工程と、

前記初期基礎構造物に前記複数の貫通孔を形成して、前記基礎構造物を形成する工程とを含むことを特徴とする請求項1記載の積層チップパッケージの製造方法。

【請求項7】

前記初期基礎構造物は、前記複数の貫通孔が形成される前の前記複数の階層部分である複数の初期階層部分を含み、

前記複数の初期階層部分の各々は、前記半導体チップを貫通するように形成された複数の絶縁材充填孔と、前記複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含み、

前記基礎構造物を形成する工程において、前記複数の貫通孔は、前記複数の初期階層部分の前記絶縁層を貫通するように形成されることを特徴とする請求項6記載の積層チップパッケージの製造方法。

【請求項8】

前記絶縁材は、主成分として樹脂を含むことを特徴とする請求項7記載の積層チップパッケージの製造方法。

【請求項9】

前記絶縁材は、更に、前記樹脂に混合された絶縁性の粒状物を含むことを特徴とする請求項8記載の積層チップパッケージの製造方法。

【請求項10】

前記基礎構造物は、前記少なくとも1つの本体形成部分として、前記複数の階層部分が積層された方向に直交する方向に配列された複数の本体形成部分を備え、

前記初期基礎構造物を作製する工程は、

それぞれ、各々が前記本体に含まれる半導体チップのいずれかとなる予定の、配列された複数の半導体チップ予定部を含む複数のチップアレイを作製する工程と、

前記複数のチップアレイを積層して前記初期基礎構造物を形成する工程とを含み、

前記積層チップパッケージの製造方法は、更に、前記複数の貫通電極を形成する工程の後で、前記複数の本体形成部分を互いに分離して複数の本体を形成する工程を備えたことを特徴とする請求項7記載の積層チップパッケージの製造方法。

【請求項11】

前記複数のチップアレイを作製する工程は、1つのチップアレイを作製するための一連の工程として、

互いに反対側を向いた第1および第2の面を有すると共に、前記配列された複数の半導体チップ予定部を含むアレイ前ウェハを作製する工程と、

前記アレイ前ウェハに対して、前記第1の面において開口し、後に前記複数の絶縁材充填孔となる複数の溝を形成する工程と、

前記複数の溝内に前記絶縁材を充填して、前記アレイ前ウェハの第1および第2の面に対応する第1および第2の面を有する研磨前アレイを形成する工程と、

前記複数の溝が前記複数の絶縁材充填孔となるように、前記研磨前アレイに対して、前記複数の溝が露出するまで、前記研磨前アレイの第2の面から研磨を行う工程とを含むことを特徴とする請求項10記載の積層チップパッケージの製造方法。

【請求項12】

前記複数の本体形成部分のうちの少なくとも1つにおける前記複数の階層部分は、1つ以上の第1の種類の階層部分と、1つ以上の第2の種類の階層部分とを含み、

前記第1の種類の階層部分における半導体チップは正常に動作するものであり、

前記第2の種類の階層部分における半導体チップは正常に動作しないものであり、

前記第1の種類の階層部分は前記配線を含むが、前記第2の種類の階層部分は前記配線を含まず、

前記複数のチップアレイを作製する工程は、

前記複数の半導体チップ予定部について、正常に動作する半導体チップ予定部と正常に動作しない半導体チップ予定部とを判別する工程と、

前記正常に動作しない半導体チップ予定部では前記配線を形成することなく、前記正常に動作する半導体チップ予定部では前記配線を形成する工程とを含むことを特徴とする請求項10記載の積層チップパッケージの製造方法。

【請求項13】

前記初期基礎構造物は、前記複数の貫通孔が形成される前の前記複数の階層部分である複数の初期階層部分を含み、

前記複数の初期階層部分の各々は、前記半導体チップの周囲に形成された絶縁層を含み、

前記基礎構造物を形成する工程において、前記複数の貫通孔は、前記複数の初期階層部分の前記絶縁層を貫通するように形成されることを特徴とする請求項6記載の積層チップパッケージの製造方法。

【請求項14】

積層された複数の階層部分と、それぞれ前記複数の階層部分の全てを貫通する複数の貫通孔とを含む本体と、

前記本体における前記複数の貫通孔内に設けられて前記複数の階層部分の全てを貫通する複数の貫通電極とを備え、

前記複数の階層部分の各々は半導体チップを含み、

前記複数の階層部分のうちの少なくとも1つは、前記半導体チップと前記複数の貫通電極とを電気的に接続する配線を含むことを特徴とする積層チップパッケージ。

【請求項15】

前記配線は、前記複数の貫通電極にそれぞれ電気的に接続された複数の導体を含み、

前記複数の導体は、それぞれ、前記複数の貫通孔の壁面に現れて前記貫通電極の外面に接触する端面を有することを特徴とする請求項14記載の積層チップパッケージ。

【請求項16】

前記複数の導体は、それぞれ、前記複数の貫通電極が通過する電極通過孔を有し、前記電極通過孔の壁面が前記端面を構成することを特徴とする請求項15記載の積層チップパッケージ。

【請求項17】

前記複数の階層部分の各々は、前記半導体チップを貫通するように形成された複数の絶縁材充填孔と、前記複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含み、

前記複数の貫通孔は、複数の階層部分の前記絶縁層を貫通していることを特徴とする請求項14記載の積層チップパッケージ。

【請求項18】

前記絶縁材は、主成分として樹脂を含むことを特徴とする請求項17記載の積層チップパッケージ。

【請求項19】

前記絶縁材は、更に、前記樹脂に混合された絶縁性の粒状物を含むことを特徴とする請求項18記載の積層チップパッケージ。

【請求項20】

前記複数の階層部分は、1つ以上の第1の種類の階層部分と、1つ以上の第2の種類の階層部分とを含み、

前記第1の種類の階層部分における半導体チップは正常に動作するものであり、

前記第2の種類の階層部分における半導体チップは正常に動作しないものであり、

前記第1の種類の階層部分は前記配線を含むが、前記第2の種類の階層部分は前記配線を含まないことを特徴とする請求項14記載の積層チップパッケージ。

【請求項21】

前記複数の階層部分の各々は、前記半導体チップの周囲に形成された絶縁層を含み、

前記複数の貫通孔は、前記複数の階層部分の前記絶縁層を貫通していることを特徴とする請求項14記載の積層チップパッケージ。

【請求項22】

積層された複数の階層部分と、それぞれ前記複数の階層部分の全てを貫通する複数の貫通孔とを含む本体と、

前記本体における前記複数の貫通孔内に設けられて前記複数の階層部分の全てを貫通する複数の貫通電極とを備え、

前記複数の階層部分の各々は半導体チップを含み、

前記複数の階層部分のうちの少なくとも1つは、前記半導体チップと前記複数の貫通電極とを電気的に接続する配線を含む積層チップパッケージを製造するために用いられる基礎構造物であって、

前記本体となる部分である本体形成部分を少なくとも1つ備え、

前記本体形成部分は、前記複数の階層部分と、前記複数の貫通電極が設けられていない状態の前記複数の貫通孔とを含み、

後に前記本体形成部分における前記複数の貫通孔内に前記複数の貫通電極が形成されるものであることを特徴とする基礎構造物。

【請求項23】

前記基礎構造物は、前記少なくとも1つの本体形成部分として、前記複数の階層部分が積層された方向に直交する方向に配列された複数の本体形成部分を備え、

前記複数の本体形成部分は、前記複数の貫通電極が形成された後に、互いに分離されて複数の本体となることを特徴とする請求項22記載の基礎構造物。

【請求項24】

前記複数の本体形成部分のうちの少なくとも1つにおける前記複数の階層部分は、1つ以上の第1の種類の階層部分と、1つ以上の第2の種類の階層部分とを含み、

前記第1の種類の階層部分における半導体チップは正常に動作するものであり、

前記第2の種類の階層部分における半導体チップは正常に動作しないものであり、

前記第1の種類の階層部分は前記配線を含むが、前記第2の種類の階層部分は前記配線を含まないことを特徴とする請求項23記載の基礎構造物。

【請求項25】

前記配線は、前記複数の貫通電極が形成されたときに前記複数の貫通電極にそれぞれ電気的に接続される複数の導体を含み、

前記複数の導体は、それぞれ、前記複数の貫通孔の壁面に現れて前記貫通電極の外面に接触する端面を有することを特徴とする請求項23記載の基礎構造物。

【請求項26】

前記複数の導体は、それぞれ、前記複数の貫通電極が形成されたときに前記複数の貫通電極が通過する電極通過孔を有し、前記電極通過孔の壁面が前記端面を構成することを特徴とする請求項25記載の基礎構造物。

【請求項27】

前記基礎構造物に含まれる前記複数の階層部分の各々は、前記半導体チップを貫通するように形成された複数の絶縁材充填孔と、前記複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含み、

前記複数の貫通孔は、前記複数の階層部分の前記絶縁層を貫通していることを特徴とする請求項22記載の基礎構造物。

【請求項28】

前記絶縁材は、主成分として樹脂を含むことを特徴とする請求項27記載の基礎構造物。

【請求項29】

前記絶縁材は、更に、前記樹脂に混合された絶縁性の粒状物を含むことを特徴とする請求項28記載の基礎構造物。

【請求項30】

前記基礎構造物に含まれる前記複数の階層部分の各々は、前記半導体チップの周囲に形成された絶縁層を含み、

前記複数の貫通孔は、前記複数の階層部分の前記絶縁層を貫通していることを特徴とする請求項22記載の基礎構造物。

【請求項1】

積層された複数の階層部分と、それぞれ前記複数の階層部分の全てを貫通する複数の貫通孔とを含む本体と、

前記本体における前記複数の貫通孔内に設けられて前記複数の階層部分の全てを貫通する複数の貫通電極とを備え、

前記複数の階層部分の各々は半導体チップを含み、

前記複数の階層部分のうちの少なくとも1つは、前記半導体チップと前記複数の貫通電極とを電気的に接続する配線を含む積層チップパッケージを製造する方法であって、

前記本体となる部分である本体形成部分を少なくとも1つ備え、前記本体形成部分は、前記複数の階層部分と、前記複数の貫通電極が設けられていない状態の前記複数の貫通孔とを含む基礎構造物を作製する工程と、

前記基礎構造物の前記本体形成部分における前記複数の貫通孔内に前記複数の貫通電極を形成する工程とを備えたことを特徴とする積層チップパッケージの製造方法。

【請求項2】

前記基礎構造物は、前記少なくとも1つの本体形成部分として、前記複数の階層部分が積層された方向に直交する方向に配列された複数の本体形成部分を備え、

前記積層チップパッケージの製造方法は、更に、前記複数の貫通電極を形成する工程の後で、前記複数の本体形成部分を互いに分離して複数の本体を形成する工程を備えたことを特徴とする請求項1記載の積層チップパッケージの製造方法。

【請求項3】

前記複数の貫通電極は、めっき法によって形成されることを特徴とする請求項1記載の積層チップパッケージの製造方法。

【請求項4】

前記配線は、前記複数の貫通電極にそれぞれ電気的に接続された複数の導体を含み、

前記複数の導体は、それぞれ、前記複数の貫通孔の壁面に現れて前記貫通電極の外面に接触する端面を有することを特徴とする請求項1記載の積層チップパッケージの製造方法。

【請求項5】

前記複数の導体は、それぞれ、前記複数の貫通電極が通過する電極通過孔を有し、前記電極通過孔の壁面が前記端面を構成することを特徴とする請求項4記載の積層チップパッケージの製造方法。

【請求項6】

前記基礎構造物を作製する工程は、

後に前記複数の貫通孔が形成されることによって前記基礎構造物となる初期基礎構造物を作製する工程と、

前記初期基礎構造物に前記複数の貫通孔を形成して、前記基礎構造物を形成する工程とを含むことを特徴とする請求項1記載の積層チップパッケージの製造方法。

【請求項7】

前記初期基礎構造物は、前記複数の貫通孔が形成される前の前記複数の階層部分である複数の初期階層部分を含み、

前記複数の初期階層部分の各々は、前記半導体チップを貫通するように形成された複数の絶縁材充填孔と、前記複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含み、

前記基礎構造物を形成する工程において、前記複数の貫通孔は、前記複数の初期階層部分の前記絶縁層を貫通するように形成されることを特徴とする請求項6記載の積層チップパッケージの製造方法。

【請求項8】

前記絶縁材は、主成分として樹脂を含むことを特徴とする請求項7記載の積層チップパッケージの製造方法。

【請求項9】

前記絶縁材は、更に、前記樹脂に混合された絶縁性の粒状物を含むことを特徴とする請求項8記載の積層チップパッケージの製造方法。

【請求項10】

前記基礎構造物は、前記少なくとも1つの本体形成部分として、前記複数の階層部分が積層された方向に直交する方向に配列された複数の本体形成部分を備え、

前記初期基礎構造物を作製する工程は、

それぞれ、各々が前記本体に含まれる半導体チップのいずれかとなる予定の、配列された複数の半導体チップ予定部を含む複数のチップアレイを作製する工程と、

前記複数のチップアレイを積層して前記初期基礎構造物を形成する工程とを含み、

前記積層チップパッケージの製造方法は、更に、前記複数の貫通電極を形成する工程の後で、前記複数の本体形成部分を互いに分離して複数の本体を形成する工程を備えたことを特徴とする請求項7記載の積層チップパッケージの製造方法。

【請求項11】

前記複数のチップアレイを作製する工程は、1つのチップアレイを作製するための一連の工程として、

互いに反対側を向いた第1および第2の面を有すると共に、前記配列された複数の半導体チップ予定部を含むアレイ前ウェハを作製する工程と、

前記アレイ前ウェハに対して、前記第1の面において開口し、後に前記複数の絶縁材充填孔となる複数の溝を形成する工程と、

前記複数の溝内に前記絶縁材を充填して、前記アレイ前ウェハの第1および第2の面に対応する第1および第2の面を有する研磨前アレイを形成する工程と、

前記複数の溝が前記複数の絶縁材充填孔となるように、前記研磨前アレイに対して、前記複数の溝が露出するまで、前記研磨前アレイの第2の面から研磨を行う工程とを含むことを特徴とする請求項10記載の積層チップパッケージの製造方法。

【請求項12】

前記複数の本体形成部分のうちの少なくとも1つにおける前記複数の階層部分は、1つ以上の第1の種類の階層部分と、1つ以上の第2の種類の階層部分とを含み、

前記第1の種類の階層部分における半導体チップは正常に動作するものであり、

前記第2の種類の階層部分における半導体チップは正常に動作しないものであり、

前記第1の種類の階層部分は前記配線を含むが、前記第2の種類の階層部分は前記配線を含まず、

前記複数のチップアレイを作製する工程は、

前記複数の半導体チップ予定部について、正常に動作する半導体チップ予定部と正常に動作しない半導体チップ予定部とを判別する工程と、

前記正常に動作しない半導体チップ予定部では前記配線を形成することなく、前記正常に動作する半導体チップ予定部では前記配線を形成する工程とを含むことを特徴とする請求項10記載の積層チップパッケージの製造方法。

【請求項13】

前記初期基礎構造物は、前記複数の貫通孔が形成される前の前記複数の階層部分である複数の初期階層部分を含み、

前記複数の初期階層部分の各々は、前記半導体チップの周囲に形成された絶縁層を含み、

前記基礎構造物を形成する工程において、前記複数の貫通孔は、前記複数の初期階層部分の前記絶縁層を貫通するように形成されることを特徴とする請求項6記載の積層チップパッケージの製造方法。

【請求項14】

積層された複数の階層部分と、それぞれ前記複数の階層部分の全てを貫通する複数の貫通孔とを含む本体と、

前記本体における前記複数の貫通孔内に設けられて前記複数の階層部分の全てを貫通する複数の貫通電極とを備え、

前記複数の階層部分の各々は半導体チップを含み、

前記複数の階層部分のうちの少なくとも1つは、前記半導体チップと前記複数の貫通電極とを電気的に接続する配線を含むことを特徴とする積層チップパッケージ。

【請求項15】

前記配線は、前記複数の貫通電極にそれぞれ電気的に接続された複数の導体を含み、

前記複数の導体は、それぞれ、前記複数の貫通孔の壁面に現れて前記貫通電極の外面に接触する端面を有することを特徴とする請求項14記載の積層チップパッケージ。

【請求項16】

前記複数の導体は、それぞれ、前記複数の貫通電極が通過する電極通過孔を有し、前記電極通過孔の壁面が前記端面を構成することを特徴とする請求項15記載の積層チップパッケージ。

【請求項17】

前記複数の階層部分の各々は、前記半導体チップを貫通するように形成された複数の絶縁材充填孔と、前記複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含み、

前記複数の貫通孔は、複数の階層部分の前記絶縁層を貫通していることを特徴とする請求項14記載の積層チップパッケージ。

【請求項18】

前記絶縁材は、主成分として樹脂を含むことを特徴とする請求項17記載の積層チップパッケージ。

【請求項19】

前記絶縁材は、更に、前記樹脂に混合された絶縁性の粒状物を含むことを特徴とする請求項18記載の積層チップパッケージ。

【請求項20】

前記複数の階層部分は、1つ以上の第1の種類の階層部分と、1つ以上の第2の種類の階層部分とを含み、

前記第1の種類の階層部分における半導体チップは正常に動作するものであり、

前記第2の種類の階層部分における半導体チップは正常に動作しないものであり、

前記第1の種類の階層部分は前記配線を含むが、前記第2の種類の階層部分は前記配線を含まないことを特徴とする請求項14記載の積層チップパッケージ。

【請求項21】

前記複数の階層部分の各々は、前記半導体チップの周囲に形成された絶縁層を含み、

前記複数の貫通孔は、前記複数の階層部分の前記絶縁層を貫通していることを特徴とする請求項14記載の積層チップパッケージ。

【請求項22】

積層された複数の階層部分と、それぞれ前記複数の階層部分の全てを貫通する複数の貫通孔とを含む本体と、

前記本体における前記複数の貫通孔内に設けられて前記複数の階層部分の全てを貫通する複数の貫通電極とを備え、

前記複数の階層部分の各々は半導体チップを含み、

前記複数の階層部分のうちの少なくとも1つは、前記半導体チップと前記複数の貫通電極とを電気的に接続する配線を含む積層チップパッケージを製造するために用いられる基礎構造物であって、

前記本体となる部分である本体形成部分を少なくとも1つ備え、

前記本体形成部分は、前記複数の階層部分と、前記複数の貫通電極が設けられていない状態の前記複数の貫通孔とを含み、

後に前記本体形成部分における前記複数の貫通孔内に前記複数の貫通電極が形成されるものであることを特徴とする基礎構造物。

【請求項23】

前記基礎構造物は、前記少なくとも1つの本体形成部分として、前記複数の階層部分が積層された方向に直交する方向に配列された複数の本体形成部分を備え、

前記複数の本体形成部分は、前記複数の貫通電極が形成された後に、互いに分離されて複数の本体となることを特徴とする請求項22記載の基礎構造物。

【請求項24】

前記複数の本体形成部分のうちの少なくとも1つにおける前記複数の階層部分は、1つ以上の第1の種類の階層部分と、1つ以上の第2の種類の階層部分とを含み、

前記第1の種類の階層部分における半導体チップは正常に動作するものであり、

前記第2の種類の階層部分における半導体チップは正常に動作しないものであり、

前記第1の種類の階層部分は前記配線を含むが、前記第2の種類の階層部分は前記配線を含まないことを特徴とする請求項23記載の基礎構造物。

【請求項25】

前記配線は、前記複数の貫通電極が形成されたときに前記複数の貫通電極にそれぞれ電気的に接続される複数の導体を含み、

前記複数の導体は、それぞれ、前記複数の貫通孔の壁面に現れて前記貫通電極の外面に接触する端面を有することを特徴とする請求項23記載の基礎構造物。

【請求項26】

前記複数の導体は、それぞれ、前記複数の貫通電極が形成されたときに前記複数の貫通電極が通過する電極通過孔を有し、前記電極通過孔の壁面が前記端面を構成することを特徴とする請求項25記載の基礎構造物。

【請求項27】

前記基礎構造物に含まれる前記複数の階層部分の各々は、前記半導体チップを貫通するように形成された複数の絶縁材充填孔と、前記複数の絶縁材充填孔内に充填された絶縁材よりなる絶縁層とを含み、

前記複数の貫通孔は、前記複数の階層部分の前記絶縁層を貫通していることを特徴とする請求項22記載の基礎構造物。

【請求項28】

前記絶縁材は、主成分として樹脂を含むことを特徴とする請求項27記載の基礎構造物。

【請求項29】

前記絶縁材は、更に、前記樹脂に混合された絶縁性の粒状物を含むことを特徴とする請求項28記載の基礎構造物。

【請求項30】

前記基礎構造物に含まれる前記複数の階層部分の各々は、前記半導体チップの周囲に形成された絶縁層を含み、

前記複数の貫通孔は、前記複数の階層部分の前記絶縁層を貫通していることを特徴とする請求項22記載の基礎構造物。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【公開番号】特開2011−233868(P2011−233868A)

【公開日】平成23年11月17日(2011.11.17)

【国際特許分類】

【出願番号】特願2011−62118(P2011−62118)

【出願日】平成23年3月22日(2011.3.22)

【出願人】(500475649)ヘッドウェイテクノロジーズ インコーポレイテッド (251)

【出願人】(500393893)新科實業有限公司 (361)

【氏名又は名称原語表記】SAE Magnetics(H.K.)Ltd.

【住所又は居所原語表記】SAE Technology Centre, 6 Science Park East Avenue, Hong Kong Science Park, Shatin, N.T., Hong Kong

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

【公開日】平成23年11月17日(2011.11.17)

【国際特許分類】

【出願日】平成23年3月22日(2011.3.22)

【出願人】(500475649)ヘッドウェイテクノロジーズ インコーポレイテッド (251)

【出願人】(500393893)新科實業有限公司 (361)

【氏名又は名称原語表記】SAE Magnetics(H.K.)Ltd.

【住所又は居所原語表記】SAE Technology Centre, 6 Science Park East Avenue, Hong Kong Science Park, Shatin, N.T., Hong Kong

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

[ Back to top ]