Fターム[4M104BB34]の内容

Fターム[4M104BB34]に分類される特許

181 - 200 / 257

半導体装置の製造方法

【課題】p型MOSFETとn型MOSFETとの間で異なる所望のしきい値を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板上にHf、 Zrの少なくとも1つと、Si、O、Nを含むゲート絶縁膜を形成し、第1、第2のゲート電極層を形成し、第1のゲート電極層上および第2のゲート電極層上に、第1の金属含有層を形成し、第2の金属含有層を形成し、保護膜を形成し、保護膜を選択的に除去し、残存する保護膜をマスクとして、第1の金属含有層および第2の金属含有層を選択的に除去し、第1の金属含有層および第2の金属含有層が選択的に除去された第2のゲート電極層上に、第3の金属含有層を成膜し、加熱処理により、第1のゲート電極層を合金化するとともに、第2のゲート電極層を合金化し、異なる組成のゲート電極を形成する。

(もっと読む)

主電極を含むドープされた金属を含む半導体装置

【課題】良好な半導体装置およびそのような半導体装置を作製するための良好な方法を提供する。

【解決手段】半導体装置は、主電極(4)と主電極(4)に接触した誘電体(3)を含み、主電極(4)は、所定の仕事関数を有する材料と、主電極(4)の材料の仕事関数を予め決められた値に向かって変調する仕事関数変調元素(6)とを含み、更に、主電極(4)は、仕事関数変調元素(6)が誘電体(3)に向かっておよび/または誘電体(3)中に拡散するのを防止する拡散防止ドーパント元素(5)を含む。

(もっと読む)

半導体素子への金属含有膜の集積方法

【課題】 本発明は、半導体プロセスに関する。より具体的には、本発明は、化学気相成長法によって形成される金属含有膜を半導体素子に集積する方法に関する。

【解決手段】 たとえばゲートスタックのような、半導体素子中の金属含有膜を集積する方法。一の実施例では、当該方法は、処理チャンバ内に基板を供する手順、その基板をタングステンカルボニル含有ガスに曝露することによって、その基板上に、第1基板温度でタングステン含有膜を成膜する手順、第1基板温度よりも高温である第2基板温度でタングステン含有膜を熱処理することで、そのタングステン含有膜から一酸化炭素を除去する手順、及びその熱処理されたタングステン含有膜上にバリヤ層を形成する手順、を有する。タングステン含有膜の例には、W、WN、WSi、及びWCが含まれる。他の実施例は、Ni、Mo、Co、Rh、Re、Cr又はRuを含む金属含有膜を、各金属元素に対応した金属カルボニル先駆体から堆積する手順を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極を好適な仕事関数を有する導電材料から構成することができ、ゲート電極の構成材料と層間絶縁層のエッチング条件との関係を考慮する必要のない半導体装置を提供する。

【解決手段】NMISFET及びPMISFETを含む半導体装置であって、各ゲート電極32A,32Bは、層間絶縁層の下層部28Aに設けられたゲート電極形成用開口部に埋め込まれており、NMISFETのゲート電極32Aの少なくとも底面部と側面部は第1の導電材料33Aから構成されており、PMISFETのゲート電極32Bの少なくとも底面部と側面部は第1の導電材料とは異なる第2の導電材料33Bから構成されており、各ゲート電極32A,32Bの頂面上には、導電性を有する保護層35A,35Bが形成されており、各ゲート電極用コンタクトプラグ44A,44Bは、保護層35A,35Bを介して、各ゲート電極32A,32Bの頂面に接続されている。

(もっと読む)

金属炭化物膜の気相成長

金属炭化物薄膜を形成する方法が提供される。好ましい実施形態によれば、金属炭化物薄膜は、反応空間中で基板を、金属源化学物質、還元剤および炭素源化学物質の空間的にかつ時間的に分離された気相パルスと交互的かつ逐次的に接触させるステップによって、原子層堆積(ALD)プロセスで形成される。この還元剤は、好ましくは水素の励起された種およびケイ素含有化合物からなる群から選択される。 (もっと読む)

半導体装置

【課題】半導体装置の表面からの放熱性を向上し、高出力動作を実現できるようにする。

【解決手段】半導体装置は、障壁層104の上に該障壁層104と接して形成されたソース電極105、ドレイン電極及びゲート電極107と、障壁層104の上に各電極の上面の少なくとも一部を覆うように形成され、障壁層104を保護する、複数の膜からなるパッシべーション膜108とを有している。パッシベーション膜108は、少なくとも窒化アルミニウムからなる膜を含む。

(もっと読む)

タンタルと炭素結合物の製造方法、タンタルと炭素の傾斜組成構造、タンタルチューブとPIT炭素芯の製造方法、タンタルチューブとPIT炭素芯、タンタル炭化物配線の製造方法、タンタル炭化物配線

【課題】簡易な方法で、所定の形状のタンタルと炭素を固相拡散接合を可能とし更に、タンタルと炭素を固相拡散接合を行う場所以外のタンタ表面に炭化物を形成することを可能とする。

【解決手段】タンタル若しくはタンタル合金と炭素基板とを真空熱処理炉内に設置し、前記タンタル若しくはタンタル合金表面に形成されている自然酸化膜であるTa2O5が昇華する条件下で熱処理を行い、前記Ta2O5を除去した後、前記真空熱処理炉内に炭素源を導入して熱処理を行い、前記タンタル若しくはタンタル合金表面と炭素基板表面を固相拡散接合させると同時に、タンタルと炭素を固相拡散接合を行う場所以外のタンタル表面に炭化物を形成する。

(もっと読む)

有機金属前駆体化合物

本発明は、式(L1)yM(L2)z−y(ここで、Mは第5族金属又は第6族金属であり、L1は置換又は非置換アニオン性6電子供与体リガンドであり、L2は同じか異なり、かつ、(i)置換若しくは非置換アニオン性2電子供与体リガンド、(ii)置換若しくは非置換カチオン性2電子供与体リガンド、又は(iii)置換若しくは非置換中性2電子供与体リガンドであり、yは整数1であり、zはMの原子価であり、Mの酸化数とL1及びL2の電荷との合計は0に等しい)で表される有機金属化合物、有機金属化合物を製造する方法並びに有機金属前駆体化合物の熱的又はプラズマ強化解離により基体上に金属及び/又は金属炭化物/窒化物層を堆積する方法に関する。 (もっと読む)

半導体装置とその製造方法

【課題】 SiC半導体層に、SiC半導体層とのコンタクト抵抗が低いオーミック電極を形成する半導体装置の製造方法を提供する。

【解決手段】 SiC半導体層に接するTi層と、Ti層に接するAl層を形成し、TiとAlが反応してAl3Tiが生成する第1基準温度(686℃)よりも高く、そのAl3TiとSiCが反応してTi3SiC2が生成する第2基準温度(970℃)よりも低い温度で、SiC半導体層とTi層とAl層に熱処理を行ない、Al3Ti層を形成する工程と、Ti層とAl層からAl3Tiが生成する反応が終了した後、第2基準温度よりも高い温度で、SiC半導体層とAl3Ti層に熱処理を行ない、SiC半導体層とオーミック接触をするTi3SiC2層を形成する工程を備えている。

(もっと読む)

半導体装置とその製造方法

【課題】 SiC半導体層に接する、コンタクト抵抗の低いオーミック電極を形成する半導体装置の製造方法を提供する。

【解決手段】 SiC半導体層に接するTi層を形成し、SiC半導体層とTi層の温度を、TiとAlが反応してAl3Tiが生成される第1基準温度(686℃)よりも高く、そのAl3TiとSiCが反応してTi3SiC2が生成される第2基準温度(970℃)よりも低い温度に上げた状態で、Ti層の上にAl層を形成する工程を備えている。

(もっと読む)

半導体装置の製造方法

【課題】金属窒化膜からなるゲート電極を有するMOSFETにおいて、ゲート電極の窒素組成を容易に制御することを可能とする半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板11の上に絶縁膜15を形成する工程(a)と、絶縁膜15の上に窒素を含まない材料かなる膜である第1の導電膜16を形成する工程(b)と、第1の導電膜16の上に窒素を含む材料からなる膜である第2の導電膜18を形成する工程(c)と、第2の導電膜18及び第1の導電膜16をパターニングしてゲート電極を形成すると共に、絶縁膜15をパターニングしてゲート絶縁膜を形成する工程(d)とを備えている。

(もっと読む)

成膜方法、成膜装置及び記憶媒体

【課題】有機不純物層の形成や銅膜の異常成長が少なく、下地膜との密着性のよい銅膜の成膜方法等を提供する。

【解決手段】基板が載置された処理容器内に水蒸気が存在する状態で、銅の有機化合物(例えばCu(hfac)TMVS)からなる原料ガスを供給して基板上に銅の密着層を形成する。次いで、処理容器内の水蒸気と原料ガスとを排出して、その後、処理容器内に再び原料ガスを供給することにより密着層の表面に銅膜を成膜する。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置、半導体装置及び記憶媒体

【課題】銅膜とその下地膜との密着性がよく、配線間の抵抗の小さな半導体装置の製造方法等を提供する。

【解決手段】大気中の水分を吸収した多孔質の絶縁層(SiOC膜11)にトレンチ100の形成された基板(ウエハW)を処理容器内に載置し、バルブメタルからなる第1の下地膜(Ti膜13)を被覆する。絶縁層から放出された水分により、絶縁層と接する第1の下地膜の表面が酸化されてパッシベーション膜13aが形成される。一方、第1の下地膜の表面をバルブメタルの窒化物または炭化物からなる第2の下地膜に被覆し、その表面に銅の有機化合物を原料とするCVDにより銅膜15を成膜する。

(もっと読む)

電界効果トランジスタ、有機薄膜トランジスタおよび有機トランジスタの製造方法

【課題】 有機TFTにおいて、電子注入効率とホール注入効率を改善した電極と有機半導体の組み合わせをそれぞれ判別する手法を提供し、n型チャネルFETとp型チャネルFETの2種類のFETを実現し、さらに、相補型MOS(CMOS)トランジスタを提供する。

【解決手段】 電極金属−有機半導体界面における真空準位シフトΔを電極と有機半導体の構成元素の物理定数から一般的に導く手法を導く。電極金属を電気化学的な手法により変化させ、電子注入とホール注入を制御できる電極を作成する。それらの電極によりn型チャネルFETとp型チャネルFETの2種類のFETを実現し、さらに、相補型MOS(CMOS)トランジスタを提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク電流が少なく、適切なしきい値を有する半導体装置と製造方法を提供する。

【解決手段】第1ソース・ドレイン領域9,10の間のp型半導体領域上に形成されたアモルファス層またはエピタキシャル層を有する第1ゲート絶縁膜5と、第1ゲート絶縁膜上に形成され4.3eV以下の仕事関数を有する第1金属の単体層である第1金属層6a、および第1金属層上に形成され第1金属と異なる第2金属とIV族半導体との化合物を含む第1化合物層6bの積層構造を有する第1ゲート電極6と、を有するnチャネルMISトランジスタ100と、第2ソース・ドレイン領域19,20と、第2ソース・ドレイン領域の間のn型半導体領域上に形成された第2ゲート絶縁膜15と、第2ゲート絶縁膜上に形成され、第1化合物層と同じ組成の化合物を含む第2化合物層16を有する第2ゲート電極16と、を有するpチャネルMISトランジスタ200と、を備えている。

(もっと読む)

中間層を有する半導体素子の形成方法及びその構造

基板(10)上に位置するスタック(30)。スタックは、誘電体層(16)と金属層(26)との間に層(24)を有する。その層は、ハロゲン及び金属を含む。一実施形態において、ハロゲンはフッ素である。一実施形態において、スタックは、トランジスタ用の制御電極スタックである。一例において、制御電極スタックは、MOSFET用のゲートスタックである。一例において、層はフッ化アルミニウムを含む。  (もっと読む)

(もっと読む)

CMOSトランジスタゲートにおいてリセスされた仕事関数金属

トランジスタゲートは、表面上に配置された一対のスペーサを有する基板と、スペーサ間で基板上にコンフォーマルに堆積された高k誘電体と、高k誘電体上とスペーサの側壁の一部に沿ってコンフォーマルに堆積されたリセスされた仕事関数金属と、リセスされた仕事関数金属上にコンフォーマルに堆積された第2の仕事関数金属と、第2の仕事関数金属上に堆積された電極金属とを含む。トランジスタゲートは、高k誘電体を基板上のスペーサ間にあるトレンチ内にコンフォーマルに堆積し、高k誘電体上に仕事関数金属をコンフォーマルに堆積し、仕事関数金属上に犠牲マスクを堆積し、仕事関数金属の一部を露出すべく犠牲マスクの一部をエッチングし、リセスされた仕事関数金属を形成すべく仕事関数金属の露出された一部をエッチングすることにより形成されうる。第2の仕事関数金属及び電極金属が、リセスされた仕事関数金属上に堆積されうる。 (もっと読む)

半導体製造方法およびエッチングシステム

【課題】疎パターン領域と密パターン領域を有する半導体の製造方法において、再現性良く疎パターンと密パターン寸法の独立制御を可能とし、各パターンの露光完の寸法及びゲート電極寸法の長期変動を抑制する。

【解決手段】マスクパターンが疎に形成された領域と密に形成された領域とを有する半導体基板上に積層膜を成膜する成膜工程とマスクパターンを形成するリソグラフィ工程S1と装置内の堆積物を除去するクリーニング工程S11Cとマスクパターンを細線化するトリミング工程S3とマスクパターンを積層膜に転写するドライエッチング工程S4、S5から成る半導体製造方法において、トリミング工程S3の前もしくは後に、シーズニング工程S11Sに続いて堆積ステップ工程S2を導入する。

(もっと読む)

半導体装置及びその製造方法

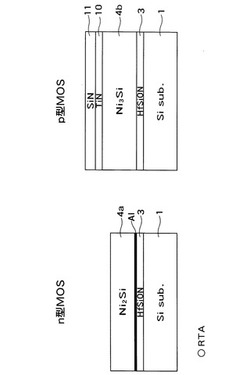

【課題】低リーク電流及び低閾値電圧のnチャネルMOSトランジスタとpチャネルMOSトランジスタとが一の基板に形成された半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成され、第1のゲート絶縁膜32及び第1のゲート電極33を有する第1導電型のトランジスタ31と、第2のゲート絶縁膜42及び第2のゲート電極43を有する第2の導電型のトランジスタ41とを備えている。第1のゲート電極33は、金属膜14aを有するメタルゲート電極であり、第2のゲート電極43は、シリサイド膜26bからなるフルシリサイド化ゲート電極である。

(もっと読む)

半導体装置

【課題】一部のゲート絶縁膜に高誘電率膜を用いている半導体装置において、より簡略して形成することが半導体装置を提供する。

【解決手段】第一の領域と第二の領域とを有する半導体装置において、第一の領域(コア部100)には、第一のゲート電極4、第二のゲート電極5および高誘電率ゲート絶縁膜3が形成されている。第一のゲート電極4と第二のゲート電極5とは、組成比が相違する。高誘電率ゲート絶縁膜3の上には、第一のゲート電極4と第二のゲート電極5が形成されている。また、第二の領域(I/O部200)には、第三のゲート電極7、第四のゲート電極8およびSiON膜6またはSiO2膜が形成されている。第三のゲート電極7と第四のゲート電極8とは、注入されている不純物元素の種類および/または濃度が異なる。また、SiON膜6またはSiO2膜上には、第三のゲート電極7と第四のゲート電極8が形成されている。

(もっと読む)

181 - 200 / 257

[ Back to top ]