Fターム[5F033PP11]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | CVD(化学的気相成長法) (3,065) | MOCVD(有機金属CVD) (177)

Fターム[5F033PP11]に分類される特許

141 - 160 / 177

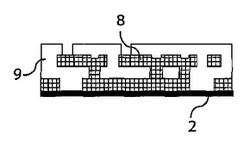

多層構造の形成方法

基板に電気化学エッチングまたは電気めっきを施すことにより多層構造を形成する方法。基板上にシード層を形成し、その上に主電極を形成する。主電極は、基板から複数の電気化学セルを形成するためのパターン層を有する。電圧が印加され、シード層がエッチングされて、またはシード層に材料がめっきされて形成された構造(8)の間に誘電体(9)が堆積される。誘電体層は下層構造を露出するために平坦化され、別の構造層が第1の構造層上に形成される。または、誘電体層は2層の厚さで形成され、下層構造の上端部を選択的に露出するために選択的にエッチングされる。また、複数の構造層を1工程で形成しても良い。 (もっと読む)

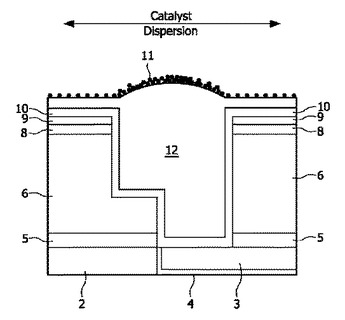

触媒及び化学気相蒸着法を用いて銅配線及び薄膜を形成する方法

【課題】触媒を使用した銅CVD方法として、ピンチ−オフやボイドの発生なしにトレンチ、ビアホール及びコンタクトを充填して銅配線導電体を形成する方法を提供すること。

【解決手段】能動及び受動素子を配線連結するために、銅配線導電体を形成する方法が開示される。ここに開示された発明は、触媒と共に銅を配線導電体物質の原料とするCVD工程を含む。トレンチ、ビアホール、コンタクト、広い受動素子だけでなく電力素子と電力線のための大きいトレンチとホールを充填する配線方法がここに開示されて提供される。ここに提示された他の方法は、狭くて深いトレンチと小径で深いホールのような小さな陥没部を触媒を使用した銅CVDで充填する方法であり、湿式または乾式エッチバックまたは高温プラズマエッチバック工程により後続工程段階に備えて除去されるように扁平な最上部の表面に非常に薄い薄膜を形成する方法である。

(もっと読む)

触媒及び化学気相蒸着法を用いて銅配線及び薄膜を形成する方法

【課題】触媒を使用した銅CVD方法として、ピンチ−オフやボイドの発生なしにトレンチ、ビアホール及びコンタクトを充填して銅配線導電体を形成する方法を提供すること。

【解決手段】能動及び受動素子を配線連結するために、銅配線導電体を形成する方法が開示される。ここに開示された発明は、触媒と共に銅を配線導電体物質の原料とするCVD工程を含む。トレンチ、ビアホール、コンタクト、広い受動素子だけでなく電力素子と電力線のための大きいトレンチとホールを充填する配線方法がここに開示されて提供される。ここに提示された他の方法は、狭くて深いトレンチと小径で深いホールのような小さな陥没部を触媒を使用した銅CVDで充填する方法であり、湿式または乾式エッチバックまたは高温プラズマエッチバック工程により後続工程段階に備えて除去されるように扁平な最上部の表面に非常に薄い薄膜を形成する方法である。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】薄膜トランジスタ表示板の製造工程を簡素化する製造方法を提供する。

【解決手段】基板110上にゲート電極を含むゲート線を形成する段階、ゲート線110上にゲート絶縁膜140を形成する段階、ゲート絶縁膜140上に半導体層150、160を形成する段階、半導体層150、160上にオーミックコンタクト部161を形成する段階、オーミックコンタクト部161上にソース電極173を含むデータ線171及びドレイン電極175を形成する段階、保護膜180を蒸着する段階、保護膜180上に感光膜を成膜して露光現像し、第1エッチングマスクとし、前記ゲート絶縁膜140及び保護膜180をエッチングしてドレイン電極175の一部と基板110の一部を露出させる段階、選択的蒸着法を利用してエッチングマスクが存在しない部分にドレイン電極175と接触する画素電極191を形成する段階、感光膜を除去する段階を含む。これによって、表示板の製造時間、製造費用が短縮されて、製品の生産性が向上する。

(もっと読む)

原子スケール金属ワイヤもしくは金属ナノクラスター、およびこれらの製造方法

【課題】原子的に完全な原子スケール金属ワイヤ及び原子スケール金属クラスタをシリコン基板上に形成する新規な方法を提供する。

【解決手段】(1)鋳型としての自己組織化ナノラインを有する表面を調製し、(2)自己組織化ナノライン以外の表面をマスク材で被覆し、(3)自己組織化ナノラインに対して選択的に濡れ性を有する金属を適切な温度で自己組織化ナノライン上に堆積させて、その金属で構成される原子スケール金属ワイヤを成長させる工程により、1原子または数原子の幅の原子スケール金属ワイヤからなり、電子素子あるいは固体量子情報素子に有用な原子スケール金属ワイヤまたは原子スケール金属ナノクラスターのアレイの製造方法。尚、濡れ性を有する金属としては、インジウム、アルミニウム、ガリウムが好適に使用される。

(もっと読む)

金属配線構造の形成方法

【課題】平坦かつ薄いバリア膜またはRu膜をダマシン構造で形成する。

【解決手段】金属配線構造を形成する方法は、(i)露出した配線層及び露出した絶縁層を含む多層構造を反応空間内に与える工程と、(ii)還元雰囲気中で、絶縁層の少なくとも露出面上に-NH2または>NHターミナルを導入する工程と、(iii)反応空間へ還元剤を導入し、その後反応空間をパージする工程と、(iv)反応空間へハロゲン化金属化合物を導入し、その後反応空間をパージする工程と、(v) N及びHを含むガスを導入し、その後反応空間をパージする工程と、(vi)金属含有バリア層を製造するべく工程(iii)から(v)を連続して繰り返す工程と、(vii)金属含有バリア層上に金属膜を形成する工程と、を含む。

(もっと読む)

トランジスタの製造方法およびメモリデバイスの製造方法

【課題】DRAM用アクセストランジスタの表面領域を小さくするメモリデバイスの製造方法を提供する。

【解決手段】トランジスタの製造方法の一実施形態は、基板内のゲート用溝部を規定することによってゲート電極を形成することを含む。上記ゲート用溝部に隣り合う位置での素子分離用トレンチ毎にてプレート状部がそれぞれ規定される。上記ゲート用溝部を挟む上記2つの各プレート状部が互いに連結される。上記一実施形態では、上記2つの各プレート状部は、上記半導体基板の材料に対して、上記素子分離用トレンチの絶縁材料を選択的にエッチングするエッチングプロセスによって規定される。ゲート絶縁体は、能動領域と上記ゲート用溝部との間の界面部、および、上記能動領域と上記の各プレート状部との間の界面部において設けられる。ゲート電極の材料は、上記ゲート用溝部と上記各プレート状部とを充填するように堆積形成される。

(もっと読む)

半導体デバイス用構造体の製造方法

本発明は、半導体デバイス用デュアルダマシン構造を製造する方法に関する。基板中に形成されたトレンチまたはバイア内の、拡散バリア層の堆積の間中、ハロゲン系前駆物質が使用される。前記堆積からの残留ハロゲンは、前記バリア層上に残ることができ、前記トレンチまたはバイアを充填するために、前記バリア層上に位置する金属層の成長を触媒するのに用いられる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 密着性を高める機能を併せ持つバリア層が形成されるまでの期間に、配線部材の十分な密着性を確保し、配線部材の剥離を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 (a1)半導体基板の上に形成された絶縁膜に凹部を形成する。(a2)凹部の内面、及び絶縁膜の上面を覆うように、CVD法により、Mnからなる第1の膜を形成する。(a3)第1の膜の上に、Cuを主成分とする導電材料を堆積させるとともに、凹部内に該導電材料を充填する。(a4)半導体基板をアニールする。

(もっと読む)

半導体装置の製造方法

【課題】 スタックト構造を有するコンタクトプラグの複数段連結されたコンタクトプラグのうちの下方のものについて、酸化防止を図る。

【解決手段】 半導体装置の製造方法は、半導体基板1上に第1の絶縁膜5を形成する工程(a)と、第1の絶縁膜5中に、バリアメタル膜7及びタングステン膜8からなる第1のプラグ9を形成する工程(b)と、第1のプラグ9Aの上方に、下部電極14、容量絶縁膜15及び上部電極16からなる容量素子17を形成する工程(c)と、第1の絶縁膜5及び第1のプラグ9上に、第2の絶縁膜11を形成する工程(d)と、第2の絶縁膜11中に、第1のプラグ9Bと接続してスタックト構造を構成する第2のプラグ21を形成する工程(e)と、工程(c)の後に、容量素子17に対して酸素雰囲気中で熱処理する工程(f)と、工程(b)と工程(d)との間に、半導体基板に対して熱処理をする工程(g)とを備える。

(もっと読む)

半導体素子の金属配線およびその製造方法

【課題】銅配線のベリア金属層の物質としてCVD TiSiNを用いて65nm以下の半導体素子にも適用できるようにした半導体素子の金属配線およびその製造方法を提供する。

【解決手段】本発明に係る半導体素子の金属配線は、半導体素子が形成された半導体基板と、前記半導体素子に相応する部分にコンタクトホールを有し、前記半導体基板に形成される絶縁膜と、前記コンタクトホール内に形成されるTiSiNベリア金属層と、前記TiSiNベリア金属層上に形成される銅配線とを含んで構成される。

(もっと読む)

ウェハ貫通相互接続部を形成する方法およびそれから得られる構造体

半導体基板内に導電バイアすなわちウェハ貫通相互接続部を形成する方法、および結果として得られるウェハ貫通相互接続構造体を開示する。本発明の一実施形態では、ウェハ貫通相互接続構造体を形成する方法は、基板の第1の表面に開口を形成する処置と、開口の内部表面に第1の絶縁層または誘電体層を堆積させる処置と、第1の誘電体層の上に導電層を堆積させる処置と、導電材料を覆って開口の内部表面に第2の絶縁層または誘電体層を堆積させる処置と、基板の反対側の第2の表面を貫通して導電層の一部分を露出させる処置とを含む。本発明の方法を用いて生成されたウェハ貫通相互接続部を含む半導体デバイスもまた開示する。 (もっと読む)

表面活性化剤を用いるタンタル含有フィルムの原子層蒸着および新規タンタル錯体

表面上にタンタル含有フィルムを形成させる原子層蒸着法が提供される。開示した蒸着法においてタンタル前駆体として用いることができる新規タンタル錯体も提供される。 (もっと読む)

電子部品とその製造方法

【課題】高信頼性の電子部品の製造方法と、互いに接近した配置が可能な電子部品を提供する。

【解決手段】半導体基板(10、10′)に回路を形成するためのCMOS構造(20、20′)を形成し、CMOS構造(20、20′)の形成後、低温処理、特に450℃以下の温度での処理で、半導体基板(10、10′)の第1面(S1)とそれとは反対側の第2面(S2)との間で回路の接続を行うべく、半導体基板(10、10′)の開口内に少なくとも1つの電気導体(30、30′)を形成する。この電子部品は電子回路及びセンサ(80、80′)の狭小な配置を可能とし、特に医療機器用として適する。

(もっと読む)

半導体装置およびその製造方法

【課題】 容量の上部電極用コンタクトを形成する際に、上部電極の損傷を防止してコンタクト部の抵抗増加や歩留まり低下が生じるのを防ぐ。

【解決手段】 半導体装置100は、半導体基板102と、半導体基板102上に、下部電極118、容量膜120、および上部電極122がこの順で積層された構造を有する容量116と、容量116の上部電極122の引出部124と、引出部124の下方に形成され、引出部124を不純物拡散領域103等の下層配線と接続するコンタクト108cとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を大幅に増加させることなく、P型MOSFETとN型MOSFETとで異なる仕事関数を有する金属ゲート電極を形成する。

【解決手段】N型MOSトランジスタとP型MOSトランジスタとが形成された半導体装置であって、N型MOSトランジスタのゲート電極107nは、ゲート絶縁膜104に接するタングステン膜105nを具備し、P型MOSトランジスタのゲート電極107pは、ゲート絶縁膜104に接するタングステン膜105pを具備し、タングステン膜105nに含有される炭素の濃度が、タングステン膜105pに含有される炭素の濃度よりも低いことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有する半導体チップの薄化に好適な技術を提供する。

【解決手段】半導体チップは、多孔質半導体層1と、多孔質半導体層1に積層された非多孔質半導体層2と、多孔質半導体層1及び非多孔質半導体層2を貫通する電極3とを含む。多孔質半導体層1及び非多孔質半導体層2と電極3とが絶縁層5によって絶縁されている。

(もっと読む)

材料を表面および基材に選択的に付着させる方法および装置

液、近臨界および/または超臨界流体から材料を選択的かつ制御可能に基材または表面に付着させて、表面または基材に付着される材料の位置および/または厚さを制御する方法が開示される。一つの例示的なプロセスでは、金属を選択的に付着させて基材の形体パターン(たとえば通路)を充填する。プロセスはさらに、たとえばシリコンウェーハ表面へのバリヤ膜の付着のために複合または構造化シリコンウェーハの表面下への材料の付着を制御するために使用することもできる。材料としては、過装入材料、金属、非金属、成層材料、有機材料、ポリマーおよび半導体材料があるが、これらに限定されない。本発明は、半導体チップ製造のような工業プロセスで用途を見いだす。特に、選択的付着は、液、近臨界または超臨界流体から付着される金属によるパターン形体の選択的充填および/またはコーティングにより、半導体チップ製造におけるケイ素面のケミカルメカニカル平坦化のようなプロセスの代替を提供する、またはその必要性を減らすものと想定される。

(もっと読む)

(もっと読む)

電子デバイス用基板、電子デバイス用基板の製造方法、表示装置および電子機器

【課題】本発明の目的は、例えば、表示装置において、表示ムラを低減することのできる電子デバイス用基板、かかる電子デバイス用基板の製造方法、かかる電子デバイス用基板を備える表示装置および信頼性の高い電子機器を提供すること。

【解決手段】

本発明の電子デバイス用基板は、基板と、この基板上に設けられたスイッチング素子と、このスイッチング素子を覆い、前記スイッチング素子の端子(接続部354)に到達するコンタクトホール361が設けられた層間絶縁膜360と、層間絶縁膜360上に設けられた画素電極223と、画素電極223に連続して、コンタクトホール361の内面および接続部354の表面に、気相プロセスにより形成された導電膜371と、コンタクトホール361の導電膜371内側の空間362を埋めるように充填された充填材料372とで構成される電気接続部370とを有するものである。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 NiSiが用いられたシリサイド上ライナー窒化膜のエッチング特性を改善し、コンタクトホール底での過度のエッチングを防止する。

【解決手段】 半導体基板301の素子活性領域にシリサイド層308を形成する工程と、半導体基板上にライナーになるシリコン窒化膜309を形成する工程と、シリコン窒化膜上に層間絶縁膜を形成する工程と、層間絶縁膜にコンタクトホールを形成する工程とを含み、シリコン窒化膜は、原子層蒸着法によりジクロロシランとアンモニアを用いて曝露するサイクルを繰り返すことにより成膜され、成膜段階におけるアンモニアガスの曝露時間は、表面反応が平衡状態になる緩和時間の2〜10倍である。これにより、窒化膜中の塩素濃度を低減でき、Si−N結合が増やすことができるため、ウェットエッチング耐性を向上できる。

(もっと読む)

141 - 160 / 177

[ Back to top ]