Fターム[5F033WW00]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273)

Fターム[5F033WW00]の下位に属するFターム

長さ、寸法 (1,572)

温度 (833)

濃度 (735)

圧力 (290)

流量 (142)

エネルギー (197)

電圧、電流 (63)

誘電率、容量 (247)

パラメータを工程途中で変化させるもの (113)

Fターム[5F033WW00]に分類される特許

101 - 120 / 1,081

半導体素子及びその半導体素子のパターン形成方法

【課題】 フォトリソグラフィ工程の解像限界内で、具現可能なサイズのパターンを利用して超微細な幅及び間隔を持つ高密度パターンを形成できる配置構造を持つ半導体素子及びその半導体素子パターン形成方法を提供する。

【解決手段】 半導体素子は、コネクション領域に隣接するメモリセル領域を含む基板、メモリセル領域からコネクション領域まで第1方向に延びて配され、第1ライン幅及び第1ライン間隔を持つ複数の第1導電ライン、第1導電ラインそれぞれに連結されるように配され、第2ライン幅及び第2ライン間隔を持つ複数の第2導電ライン、コネクション領域に配され、第1導電ラインに電気的に連結された複数のパッド、を備える。半導体素子上のパターン形成方法は、微細ライン幅及び間隔を提供するために2段階のスペーサ形成工程を含むことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】より低コストで、より信頼性の高いMIMキャパシタを有する、より信頼性の高い半導体装置、およびその製造方法を提供する。

【解決手段】本製造方法は、半導体基板SUBを準備する工程と、半導体基板SUBの一方の主表面上に、アルミニウム層AC1を有する第1の金属電極LEL1と、第1の金属電極LEL1上の誘電体層DECと、誘電体層DEC上の第2の金属電極UELとを形成する工程とを備える。第1の金属電極LEL1を形成する工程においては、表面がRmax<80nm、Rms<10nm、Ra<9nmの関係を満たすように、アルミニウム層AC1が形成される。第1の金属電極LEL1を形成する工程には、少なくとも1層の第1のバリア層T1を形成する工程と、第1のバリア層T1上に、アルミニウム層AC1を形成する工程と、アルミニウム層AC1を構成する結晶を再結晶化する工程とを含んでいる。

(もっと読む)

導電膜用エッチング液およびエッチング方法

【課題】従来の蓚酸系エッチング液のような界面活性剤配合に伴う泡や蓚酸に由来する残渣の発生を生じることなく、界面活性剤を一切使用しなくても、濡れ性、泡切れ性が優れ、高精度で透明導電膜をエッチングすることができるエッチング液およびエッチング方法を提供すること。

【解決手段】少なくとも蓚酸を主成分とする導電膜用エッチング剤(A)と、(B)群および(C)群から選ばれる少なくとも1種とを含有し、界面活性剤を一切含有しないことを特徴とする導電膜用エッチング液。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】機械的強度および密着力に優れた低誘電率の層間絶縁層を有する半導体装置を提供すること。

【解決手段】基板上に形成された、SiO2骨格を含む第1の多孔質層6と、第1の多孔質層6の直上に形成された、SiO2骨格を含む第2の多孔質層7と、第1の多孔質層6に埋め込まれたビア10と、第2の多孔質層7に埋め込まれた配線11と、を有し、第1の多孔質層6の孔密度x1は40%以下であり、第2の多孔質層7の孔密度x2は、(x1+5)%以上である半導体装置を提供する。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】エッチング工程時に銅が露出して不純物が発生することを最小化できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】絶縁基板の上にゲート線124、ゲート絶縁膜140、第1非晶質シリコン膜154、第2非晶質シリコン膜164、第1金属膜174a、及び第2金属膜174bを順次形成する段階と、第2金属膜174bの上に第1部分と第1部分より厚さの厚い第2部分とを有する感光膜パターン52を形成する段階と、感光膜パターン52をマスクとして第2金属膜174b及び第1金属膜174aをエッチングして、第2金属パターン及び第1金属パターンを形成する段階と、第2金属パターンにSF6気体またはSF6とHeの混合気体で前処理する段階とを含む。

(もっと読む)

耐透明導電膜ピンホール腐食性に優れた薄膜トランジスタ基板

【課題】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、その製造工程において、腐食防止用塗料の塗布や剥離といった工程を設けることなく、ピンホール腐食を防止できるような薄膜トランジスタ基板を提供する。

【解決手段】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、前記透明導電膜の結晶最大粒径が200nm以下である薄膜トランジスタ基板。

(もっと読む)

半導体装置及びその製造方法

【課題】配線間の実効的な容量の増加を抑制する。

【解決手段】半導体装置100は、6員環構造の環状シロキサンを原料とする絶縁膜11と、絶縁膜11に形成された配線溝12と、配線溝12に金属膜(配線メタル)15が埋め込まれて構成される配線10と、を有する。半導体装置100では、配線溝12の底面において、絶縁膜11の内部よりも単位体積あたりの炭素原子数、又は/及び、窒素原子数が多い改質層13が形成されている。

(もっと読む)

銅配線半導体用洗浄剤

【課題】 研磨剤由来の砥粒の除去性、絶縁膜上の金属残渣と有機残渣の除去性に優れ、かつ銅配線の耐腐食性に優れる銅配線半導体用洗浄剤を提供することを目的とする。

【解決手段】 銅または銅合金配線を形成する半導体製造工程中の化学的機械的研磨の後に続く工程において使用される洗浄剤であって、アミン(A)、グアニジンの塩またはグアニジン誘導体の塩(B)、および水を必須成分とし、使用時のpHが8.0〜13.0であることを特徴とする銅配線半導体用洗浄剤を用いる。

(もっと読む)

半導体装置の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

半導体装置の製造方法

【課題】溝部を絶縁膜で埋設する際に、溝部のアスペクト比が大きい場合であっても、内部にボイドを残存させることなく、溝部内に絶縁膜を充填する。これにより微細化した半導体装置の製造を容易に行うことを可能とする。

【解決手段】隣り合う凸部の間に形成される溝部の上端部においてオーバーハング形状を有すると共に、溝部の上部にボイドを有するように溝部内に溝部用絶縁膜を形成する。凸部の高さ方向に対して斜め方向から、溝部用絶縁膜に不純物をイオン注入することにより、溝部内に形成された溝部用絶縁膜の一部に不純物をドープする。溝部用絶縁膜の不純物がドープされた部分を除去した後、溝部内に溝部用絶縁膜を充填する。

(もっと読む)

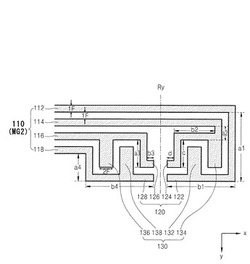

半導体装置

【課題】 動作不良を抑制するのに適する半導体装置を提供すること。

【解決手段】 半導体チップ1と、半導体チップ1に積層された第1電極パッド21と、方向xに延びる第1の縁49aと、方向yに延びる第2の縁とに規定された矩形状を呈する中間層4と、半導体チップ1とともに中間層4を挟むように配置された複数のバンプ5と、を備え、複数のバンプ5のいずれか一つは、複数のバンプ5のうち、方向xの一端且つ方向yの一端に配置され並びに第1電極パッド21に導通する第1バンプ51であり、複数のバンプ5のいずれか一つは、第1電極パッド21に導通する第2バンプ52である。

(もっと読む)

電子デバイス及びその製造方法

【課題】高性能及び高機能で、高周波特性に優れ、コストダウンに有効な絶縁構造を持つ電子デバイス及びその製造方法を提供する。

【解決手段】半導体基板1は、その厚み方向に伸びる縦孔30を有している。絶縁物充填層3は、縦孔30内にその内周面を覆うように充填してなる環状層である。縦導体2は、絶縁物充填層3によって囲まれた領域20内に充填された凝固金属体でなる。絶縁充填層3は、有機絶縁物又はガラスを主成分とする無機絶縁物と、ナノコンポジット構造のセラミックとを有する層である。ナノコンポジット構造のセラミックは、常温比抵抗が1014Ω・cmを超え、比誘電率が4〜9の範囲にある。

(もっと読む)

貫通孔を形成しためっき層付シリコン基板

【解決課題】 複数の微細な貫通孔が存在するシリコン基板において、半導体プロセスに依らない簡素な技術により平坦部のみならず貫通孔内部にも密着性が良好な金属膜を成膜して、高密度実装用途に好適なシリコン基板を提供する。

【解決手段】 めっき前処理によりシリコン基板の平坦部と貫通孔内部の清浄シリコン表面を現出させ、ニッケル置換めっき・無電解銅めっき(S4)を順に行うことにより、シリコン基板の全ての貫通孔の内壁全面ならびに主面の全面もしくは一部の面を直接被覆し、密着性に優れ良好な導電性を示す膜を有するめっき層付シリコン基板を作製することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】3次元集積化技術を適用した場合にも十分な放熱効果が得られる、放熱効率の高い放熱構造を持つ半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1の素子形成面の反対面1bには、貫通電極2の少なくとも端面を露出させる第1の凹部3と、貫通電極2を露出させない第2の凹部8とが形成されている。半導体基板1の反対面1b上には、第1の凹部3における貫通電極3の端面を除く内面及び第2の凹部8の内面を覆うように第1の絶縁膜4が形成されている。第1の絶縁膜4上には、貫通電極2の端面と接続し且つ第1の凹部3の外側まで延びる導電膜5が形成されている。

(もっと読む)

導電性素子およびその製造方法、配線素子、情報入力装置、表示装置、ならびに電子機器

【課題】優れたスループットを実現できる導電性素子を提供する。

【解決手段】導電性素子は、第1の波面および第2の波面を有する基体と、第1の波面上に形成された導電層とを備える。導電層は、導電パターン部を形成し、第1の波面および第2の波面が、0≦(Am1/λm1)<(Am2/λm2)≦1.8(但し、Am1:第1の波面の振動の平均幅、Am2:第2の波面の振動の平均幅、λm1:第1の波面の平均波長、λm2:第2の波面の平均波長)の関係を満たす。

(もっと読む)

半導体装置の製造方法

【課題】ボイドとヒロックの発生の双方を抑制してCu配線を形成する。

【解決手段】半導体基板上の層間絶縁膜に溝パターンを形成する工程(S1)、めっき法によりCu膜を形成する工程(S2,S3)、130〜180℃で第1アニールを行う工程(S4)、CMPにより溝パターン以外の銅膜を除去する工程(S5)、300〜350℃でグレイン成長のための第2アニールを行う工程(S6)とを備える。

(もっと読む)

金属配線

【課題】従来の、真空装置を用いた形成方法に比べて簡便かつ安価に形成され、しかもインクジェット印刷方法によって形成されるもの比べて、断線等を生じることなしに、より細線化された金属配線を提供する。

【解決手段】Ag粒子、またはAgを50原子%以上含む合金粒子を含む分散液を塗布して塗膜を形成し、乾燥後にパターン形成したのち焼成して形成され、その縁部2における、基材の表面方向の、想定される外形線4からの凹入量の最大値と突出量の最大値との和が50nm以下、前記縁部2における、基材3の表面方向の、想定される外形線4と直交し、かつ金属配線1の厚み方向の断面のうち、前記厚み方向の外形線の、前記基材3の表面と接する部分の、前記基材3の表面との交差角度が70°以下で、かつ抵抗率が14μΩ・cm以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】パッド電極に荷重または衝撃力が加わっても、周囲の絶縁膜にクラックが発生しにくい構造の半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、平面形状が、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形、ならびに、これらの少なくとも一部分を含む形状の組合せからなる群から選ばれた平面形状となるような凹部を形成する凹部形成工程と、前記凹部の内面に少なくとも一部を被覆する下敷膜を形成する下敷膜形成工程と、絶縁膜で覆われた前記凹部に導電性の電極材質を埋め込むパッド部形成工程とを含み、前記凹部形成工程は、第1の凹部を形成する工程と、前記第1の凹部の一部分においてさらに深く凹む第2の凹部を形成する工程とを含む。

(もっと読む)

パターン形成方法

【課題】ダブルパターニング法を用いる場合にパターンの疎密に拘わらず、所望のパターンを形成できるようにする。

【解決手段】第1のレジスト膜に第1の露光光を照射し第1の現像を行なうことにより、配線溝パターンを含む第1の領域Aに第1パターン5aを形成すると共に、第1の領域Aと接続され且つ配線溝パターンと比べてパターン密度が疎である第2の領域Bにダミーパターン5bを形成する。その後、第1のレジスト膜を硬化し、硬化した第1のレジスト膜の上に、第2のレジスト膜9を形成する。その後、第2のレジスト膜9に第2の露光光を照射し第2の現像を行なうことにより、第1の領域Aに第2パターン9aを形成する。該第2パターン9aを形成する際に、第1の領域Aには、第1パターン5a及び第2パターン9aにより配線溝パターン2aが形成される一方、第2の領域Bは、ダミーパターン5bの開口部が第2のレジスト膜9によって埋められる。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

101 - 120 / 1,081

[ Back to top ]