Fターム[5F033WW00]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273)

Fターム[5F033WW00]の下位に属するFターム

長さ、寸法 (1,572)

温度 (833)

濃度 (735)

圧力 (290)

流量 (142)

エネルギー (197)

電圧、電流 (63)

誘電率、容量 (247)

パラメータを工程途中で変化させるもの (113)

Fターム[5F033WW00]に分類される特許

41 - 60 / 1,081

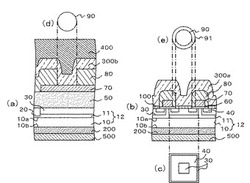

半導体装置および半導体装置の製造方法

【課題】 薄板化の際に層間絶縁膜が破損することを抑制できる半導体装置を得る。

【解決手段】 第1の硬度を有する材料で構成された基板10と、基板10の第1主面10aに設けられたドリフト層11と、ドリフト層11上に絶縁膜60を介して形成されたゲート電極70と、ゲート電極70を覆うように形成され、第1の硬度よりも小さい第2の硬度を有する材料で構成された層間絶縁膜80とを備え、基板10とドリフト層11とを合わせた厚みは200μm以下であり、層間絶縁膜80に、平面視において、全ての内角が90°より大きい多角形、円形または楕円形の開口90が設けられている半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール内に良好にAl膜が埋設されたコンタクトプラグを有する半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板の層間絶縁膜内にコンタクトホールを形成する工程と、基板を加熱した状態でコンタクトプラグを形成する工程を有する。コンタクトプラグを形成する工程では、スパッタ装置のチャンバー内のステージ上に、チャックを介して基板を保持し、チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。チャンバー内のターゲットに対して第一のターゲット電力を印加してコンタクトホール内に第一のAl膜を成膜する。次に、チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して第一のAl膜上に第二のAl膜を成膜する。

(もっと読む)

半導体電極構造

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられたAl合金膜を有する半導体電極構造を提供する。

【解決手段】基板上に少なくとも、基板側から順に、高融点金属の窒化物薄膜と、Al合金膜とを備えた半導体電極構造であって、前記Al合金膜は、500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が300nm〜5μmであることを特徴とする半導体電極構造。(a)Alマトリックスの最大粒径が1μm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】基板を実装する際の温度負荷によって絶縁層と下地金属層の側面との接点領域に加わる応力を緩和させ、応力に起因した絶縁層のクラックの発生を抑えるように構成された半導体装置を提供する。

【解決手段】半導体基板101の一面101aに、絶縁層102、下地金属層103、金属端子が設けられるためのランド部104を順に積層してなる半導体装置109であって、ランド部104は、絶縁層102と対向する面の中央部において、下地金属層103と接合する接合領域と、絶縁層102と対向する面において、接合領域を除いた非接合領域と、を有し、下地金属層103は、ランド部104側から絶縁層102側にかけて外向きに傾斜した側面を有していること、を特徴とする半導体装置109。

(もっと読む)

半導体装置用Al合金膜

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられた半導体装置用Al合金膜を提供する。

【解決手段】500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が500nm〜5μmであることを特徴とする半導体装置用Al合金膜。(a)Alマトリックスの最大粒径が800nm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

半導体装置の製造方法

【課題】 低k膜と金属マスクとの間の界面に歪みを引き起こすことなく、高い精度の望ましいパターンを得ること。

【解決手段】 半導体装置を製造する方法では、金属マスクと絶縁マスクをと備える多層ハードマスクを用いて形成される配線層を含む半導体装置が形成される。第1パターンにアラインされた第2開口パターンを形成するために、第1ステップで多層ハードマスクが使用された後、金属マスクが除去され、絶縁マスクが、第2のステップで絶縁層中に第1のパターン構造を形成するために使用される。

(もっと読む)

誘電フィルム及び材料における疎水性を回復する方法

【課題】誘電率の増加、シラノールの増加、または有機部分の減少、の少なくとも一つによって損傷した、基体上のシリカ誘電フィルムの損傷を回復する。

【解決手段】基体上のそのような損傷シリカ誘電フィルムを表面改質組成物と接触させて、該損傷シリカ誘電フィルムの誘電率の減少、該損傷シリカ誘電フィルムの誘電率のシラノールの減少、該損傷シリカ誘電フィルムの誘電率の有機部分の増加、の1つ以上をもたらす。このとき、該損傷シリカ誘電フィルムに疎水性を与える。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】本発明は、絶縁膜を金属に密着させることができる半導体装置の製造方法と半導体装置を提供することを目的とする。

【解決手段】本願の発明に係る半導体装置の製造方法は、基板上に多結晶の金属を形成する工程と、該金属の表面粗さRaが0.051μmより大きくなり、かつ該金属の表面に1〜10μm径のランダムな方向に伸びる複数の穴が形成されるように、該金属の表面を1.0μm/min未満のエッチングレートでウェットエッチする工程と、該金属の表面に絶縁膜を形成する工程と、を備えたことを特徴とする。

(もっと読む)

基板中間体、基板及び貫通ビア電極形成方法

【課題】貫通ビア電極を形成する際に処理温度が高くなく且つ低コストで、バリア層を均一に、且つ高い密着強度で製造する。

【解決手段】シリコン基板10の厚さ方向に形成された高アスペクト比の、貫通ビア電極形成用の孔12の内周面に、自己組織化単分子膜24を形成し、これに、金属ナノ粒子14を、高密度で吸着させて、この金属ナノ粒子14を触媒として、バリア層を無電解めっきにより形成し、バリア層の上にシード層を無電解めっきにより形成し、次に、貫通ビア電極材を電解めっきにより堆積して、孔12を埋めて、貫通ビア電極を形成する。

(もっと読む)

Cu配線の形成方法および成膜システム

【課題】Cuめっきを用いることなくPVDのみでトレンチまたはホールCuを埋め込んでCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202の全面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上にPVDによりCuがマイグレーションする条件でトレンチ203内に第1のCu膜206を形成する工程と、第1のCu膜206の上に、第1のCu膜206よりも大きな成膜速度でPVDにより第2のCu膜207を形成する工程と、CMPにより全面を研磨する工程とを有する。

(もっと読む)

半導体チップとその製造方法、半導体装置

【課題】立体的な集積に適した、電磁妨害耐性に優れる半導体チップを提供する。また、その半導体チップを用いた、高い電磁妨害耐性と高い処理能力を両立する半導体装置を提供する。

【解決手段】能動素子もしくは受動素子と、それらの素子を電気的に接続する配線部を備えた半導体チップについて、配線部を被覆するように導電性薄膜を設ける。この導電性薄膜は配線部に対して、不要電磁波を遮蔽するシールドとして働くので、半導体チップの電磁妨害耐性が向上する。また、この半導体チップを三次元集積半導体装置に組み込むことで、隣接するチップをフェイス・トゥ・フェイス接続した場合でも、チップ間のクロストークを遮断できる。

(もっと読む)

半導体装置、半導体装置用基板および該基板の製造方法

【課題】電気的接続の信頼性を損なうことなく電気抵抗率を従来よりも低減できる埋め込み配線を有する半導体装置用基板および半導体装置を提供する。

【解決手段】本発明は、上記目的を達成するため、埋め込み配線を有する半導体装置用基板であって、前記埋め込み配線は、金属多結晶体からなり、平均結晶粒径が異なる少なくとも2層の領域を前記基板の厚さ方向に有し、前記埋め込み配線の開口面を含む層の平均結晶粒径が、前記埋め込み配線の他の層の平均結晶粒径よりも小さいことを特徴とする半導体装置用基板を提供する。また、本発明は、上記半導体装置用基板を用いたことを特徴とする半導体装置を提供する。

(もっと読む)

薄膜の成膜方法

【課題】基板上への薄膜の成膜速度を上げ、かつトレンチやビアホールの底面に効率よく薄膜を成膜できる薄膜の形成方法を提供すること。

【解決手段】本発明の成膜方法は、開口幅又は開口径が3μm以下で、かつ、アスペクト比が1以上の段差であるトレンチ又はビアホールを有する基板上に薄膜を成膜する成膜方法であり、真空排気可能な処理室に、基板を支持する第1の電極と、前記基板に対向するように配置されターゲットを支持する第2の電極と、前記第2の電極の外側に配置されて当該第2の電極の内側にカスプ磁界を形成する複数のマグネットと、を備え、

前記処理室にNeを含む処理ガスを導入し、前記第1の電極と前記第2の電極の少なくとも一方にプラズマ形成用の高周波電力を供給すると共に、前記第2の電極上にカスプ磁場を生成してプラズマを発生させ、ターゲット物質をトレンチ又はビアホールを有する基板上に成膜する。

(もっと読む)

電界効果型トランジスタ

【課題】駆動時の発熱温度を低下させる。

【解決手段】基板12の熱伝導率をNsub(W/mK)とし、熱拡散層14の熱伝導率をNkaku(W/mK)とし、熱拡散層14の膜厚をT(mm)とし、熱拡散層14の平面開口率をR(0≦R≦1)とし、S=T×Rとしたとき、例えば、基板12の熱伝導率Nsubが、Nsub<1.8の条件を満たし、熱拡散層14の熱伝導率Nkakuが、Nkaku>3.0×S^(−0.97×e^(−1.2×Nsub))且つNkaku≧Nsubの条件を満たす。

(もっと読む)

表示装置及びマスク

【課題】マスクの枚数を増やすことなく、ストレージキャパシタの電極間から半導体パターンを除去して高画質化を実現させる表示装置及びその製造方法を提供する。

【解決手段】本発明によるTFTパネルの製造では、半導体パターンとTFTのドレイン電極とを、同じマスクを利用したエッチングで同時にパターニングする。一方、画素電極の直下に形成される絶縁膜のパターニングには別のマスクを利用する。ドレイン電極を覆う絶縁膜の領域では、中央部の全体を感光させ、周辺部を半分の厚みまで感光させる。ストレージ電極の上方を覆う絶縁膜の領域は薄い一部を残して感光させる。ドレイン電極を覆う誘電膜をエッチングしてドレイン電極を露出させるとき、絶縁膜のその薄い一部がその下地の誘電膜を保護する。その後、絶縁膜のその薄い一部を画素電極の一部に置換し、保護された誘電膜を隔ててストレージ電極と対向させる。

(もっと読む)

厚膜金属電極の形成方法、及び厚膜レジストの形成方法

【課題】炭化珪素基板に形成された回路素子層上に、厚さが7μm以上で、かつ面内均一性に優れたポジ−ネガ反転型レジストが形成可能な厚膜金属電極の形成方法、及び厚膜レジストの形成方法を提供する。

【解決手段】HMDS処理された回路素子層の上面に、第1の粘性値を有した第1のポジ−ネガ反転型レジストを形成し、次いで、第1のポジ−ネガ反転型レジスト上に、第1及び第2のポジ−ネガ反転型レジスト(厚膜レジスト)の合計の厚さが7μm以上となるように、第1の粘性値よりも大きい第2の粘性値を有した第2のポジ−ネガ反転型レジストを形成する。

(もっと読む)

シリカ系被膜、シリカ系被膜形成用組成物、シリカ系被膜の製造方法及び電子部品

【課題】機械強度が十分であり、低誘電性に優れ、シリコンウエハー及びP−TEOS等のSiO2膜の両方への接着性に優れたシリカ系被膜を提供する。

【解決手段】実質的にOH基の含有量が大幅に減少されてなる高い緻密性を備えた微細孔を有するシリカ系被膜。(a)一般式(1)で表せられる化合物を加水分解縮合して得られるシロキサン樹脂、(化1)R1nSiX4−n(1)(式中、R1は、H若しくはF又はB、N、Al、P、Si、Ge若しくはTiを含む基又は炭素数1〜20の有機基を示し、Xは、加水分解性基を示すし、nは0又は1の整数である)(b)下記一般式(2)で表せられるイオン性化合物並びに(化2)(R24N+)nYn−(2)(式中、R2は、水素原子又は炭素数1〜20の有機基を示し、Yは、陰イオンを示し、nは陰イオンの価数である)(c)前記(a)成分及び(b)成分を溶解可能な溶媒を含むシリカ系被膜形成用組成物。

(もっと読む)

配線の形成方法および形成装置

【課題】有機導電性材料を含む塗布組成物をプラスチック基板上に形成した後、高い電気電導度の配線を形成することができる配線の形成方法および形成装置を提供すること。

【解決手段】プラスチック基板上に有機導電性材料を含む塗布組成物が塗布されて配線パターンが形成された部材を準備し、少なくとも前記配線パターンに電磁波を照射してアニールし、有機導電性材料からなる配線を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】貫通孔の側面のスキャロップ形状及びアンダーカットを修復する。

【解決手段】半導体装置は、第1の基板と、第2の基板と、前記第1の基板と前記第2の基板との間に配置され、前記第1の基板と前記第2の基板とを接着する接着層と、を備え、前記第2の基板及び前記接着層には、前記第2の基板及び前記接着層を貫通する貫通孔が形成されており、前記貫通孔の側面には、凹部が形成されており、前記凹部には、少なくとも有機骨格を有する樹脂が埋め込まれており、前記貫通孔の中には、導電体が形成されている。

(もっと読む)

貫通孔基板、貫通配線基板、電子部品、基板の製造方法、及び貫通孔の検査方法

【課題】貫通孔内の状態を確認できる貫通孔基板、貫通配線基板、電子部品、基板の製造方法、及び貫通孔の検査方法の提供。

【解決手段】(1)基板1の一面1aから他面1bにかけて貫通孔4が形成され、一面1aにおける貫通孔4の開口部5を覆う導電パターン2が配された貫通孔基板であって、導電パターン2には、貫通孔4を一面1a側から観察可能な切抜き3が形成されていることを特徴とする貫通孔基板。(2)切抜き3において、開口部5の縁が観察可能であることを特徴とする(1)に記載の貫通孔基板。

(もっと読む)

41 - 60 / 1,081

[ Back to top ]