Fターム[5F033WW00]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273)

Fターム[5F033WW00]の下位に属するFターム

長さ、寸法 (1,572)

温度 (833)

濃度 (735)

圧力 (290)

流量 (142)

エネルギー (197)

電圧、電流 (63)

誘電率、容量 (247)

パラメータを工程途中で変化させるもの (113)

Fターム[5F033WW00]に分類される特許

141 - 160 / 1,081

半導体装置およびその製造方法

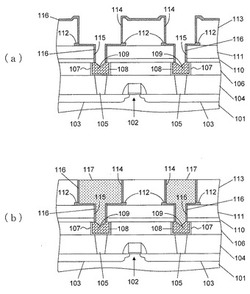

【課題】 デュアルダマシン法による配線構造の製造において、接続プラグ用のホールを通じて下層配線の表面に凹部をエッチング形成するとき、上層配線用の溝の底部が過剰エッチングされないようにする。

【解決手段】 TaNなどからなり、接続プラグに対応する開口を有する導電性膜パターン112をSiOCなどからなる層間絶縁膜111と113との間に設けた後、配線溝114、ホール115を形成する。次にTaN、Taなどからなる積層導電性膜116を堆積し、ホール115の底部の積層導電性膜116を除去し、さらに下層配線を構成するCu膜109を掘り込むエッチングを行う。このとき、導電性膜パターン112があるために配線溝114の底部の下にある層間絶縁膜111のエッチングを防止できる。その後、配線溝114およびホール115内にCuなどの導電性膜117を埋め込む。

(もっと読む)

低誘電率誘電体を含む超小型電子構造およびその構造内の炭素分配を制御する方法

本発明の実施形態は、超小型電子構造の形成に関する。32nmの次のテクノロジーノード向けの低誘電率誘電体材料は、約2.6未満の誘電率を呈する必要がある。本発明により、全体として超小型電子構造の曲げおよび剪断強度の完全性を向上させながら、そのような低誘電率誘電体材料を使用する半導体デバイスを形成することが可能になる。  (もっと読む)

(もっと読む)

マンガン含有低誘電率膜及びその製造方法、半導体装置の製造方法並びに成膜装置

【課題】マンガン含有材料を利用して、低誘電率膜への銅の拡散を防止する。

【解決手段】成膜装置100では、制御部70の制御に基づき、処理容器1内を真空にして、ヒーター6によりウエハWを加熱しつつ、シャワーヘッド11のガス吐出孔13a,13bからウエハWへ向けて低誘電率材料とマンガン含有材料とを含む成膜ガスを供給する。高周波電源23からシャワーヘッド11に高周波電力を供給することにより、成膜ガスを解離させ、処理容器1内に成膜ガスのプラズマを生成させる。このプラズマによって、ウエハWの表面にMnを含有するSiCOH膜を成膜する。

(もっと読む)

半導体装置の製造方法及びフォトマスク

【課題】半導体記憶装置の製造において、パターン間隔を縮小し、レジスト膜厚、エッチング量等のバラツキに対応する。

【解決手段】半導体装置の製造方法は、基板上に被加工膜を形成する工程(a)、被加工膜上にレジスト膜を形成する工程(b)、フォトマスクのマスクパターン200bをレジスト膜に転写パターン200cとして転写する工程(c)、転写パターン200cを加工する工程(d)を含む。転写パターン200cは、所定間隔を開けて端部同士が対向して直列に並ぶ第1及び第2の転写ラインパターン201c及び202cと、これらに各々並列する第3及び第4の転写ラインパターン203c及び204cと、第2及び第3の転写ラインパターン202c及び203cの端部同士を接続する接続部212とを含む。工程(d)にて、接続部212の少なくとも一部を除去し、第2及び第3の転写ラインパターン202c及び203cを分離する。

(もっと読む)

導体層の形成方法及び半導体装置の製造方法

【課題】レジスト残滓を確実に除去する。

【解決手段】基板10上の一部にレジスト20を用いて導体層19をパターニングした後、レジスト20を剥離するレジスト剥離工程と、基板10の導体層19が形成された面に対して、第一ノズル103から第一噴射圧で溶剤を噴射することによりレジスト20の残滓20bをふやかし、第二ノズル104から第一噴射圧よりも高圧の第二噴射圧で溶剤を噴射することによりレジスト20の残滓20bを物理力で除去するレジスト残滓除去工程と、を備える導体層の形成方法である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】素子の信頼性を劣化させることなく、より比誘電率の低い絶縁膜を形成する。

【解決手段】この半導体装置の製造方法は、下地膜101に、環状シロキサンをプラズマ重合させて第一の絶縁膜102を形成する工程と、第一の絶縁膜102を形成する工程の後、連続的に、第一の絶縁膜102上に、環状シロキサンをプラズマ重合させて第二の絶縁膜103を形成する工程と、を含む。第一の絶縁膜102の成膜速度は、第二の絶縁膜103の成膜速度よりも遅い。

(もっと読む)

三次元集積回路用の層間充填材組成物、塗布液、三次元集積回路の製造方法

【課題】 少ない無機フィラーの含有量であっても、より熱伝導性が高い充填層を形成することができる層間充填材組成物を提供すること。

【解決手段】 三次元集積回路用の層間充填材組成物が、微粒子状樹脂フィラー、熱伝導度が1W/m・K以上の無機フィラー、及びマトリックス樹脂を含有し、かつ該層間充填材組成物100体積%あたり、微粒子状樹脂フィラーを1体積%以上50体積%以下、無機フィラーを1体積%以上80体積%以下含有する。

(もっと読む)

薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法

【課題】接着層の厚さを増加させることなく、銅の下部層との接着性が向上し、銅が下部層に拡散することを防止することができる薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法を提供する。

【解決手段】本発明の薄膜形成方法は、基板上にスパッタリング方法により薄膜を形成する方法であって、薄膜は、電力密度が1.5〜3W/cm2、非活性気体の圧力が0.2〜0.3Paで形成する。薄膜は、非晶質構造を有することができ、チタニウム、タンタル、又はモリブデンのうちのいずれか一つで形成することができる。

(もっと読む)

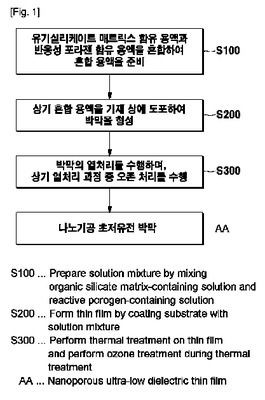

高温オゾン処理を含むナノ細孔の超低誘電薄膜の製造方法及びこれによって製造されたナノ細孔の超低誘電薄膜

高温オゾン処理を含むナノ細孔の超低誘電薄膜の製造方法及びこれによって製造されたナノ細孔の超低誘電薄膜が提供され、前記製造方法は、有機シリケートマトリックス−含有溶液と反応性ポロゲン−含有溶液とを混合して混合溶液を準備し、前記混合溶液を基材上に塗布して薄膜を形成し、前記薄膜を熱処理し、前記熱処理の過程中にオゾン処理を行うことを含み、このような製造方法によって製造されたナノ細孔の超低誘電薄膜は、高温のオゾン処理及び処理温度の最適化による薄膜内の細孔のサイズと分布度の改善を通じて、2.3以下の誘電率と10GPa以上の機械的強度とを有することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】配線間のリーク電流が発生することを抑制し、配線間容量の増大を抑制する。

【解決手段】半導体装置100の製造方法は、絶縁膜2にダマシン配線を形成する工程(A)を含む半導体装置100の製造方法であって、基板1上に形成された絶縁膜2の表面にプラズマ処理を行い、絶縁膜2中の水分を脱離する工程(B)と、シリル化ガスを含む雰囲気中でアニール処理を行い、絶縁膜2をシリル化する工程(C)と、を含む。

(もっと読む)

半導体装置

【課題】半導体装置の微細化を犠牲とすることなく、ビアの冗長性を向上させ、歩留まりが高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板の上に形成された第1の配線211aと、第1の配線211aよりも上層に形成された第3の配線231aと、第1の配線211aと第3の配線231aとを接続する第1のビア221aとを備えている。第1のビア221aの形成位置と第3の配線231aの端部との間隔t1は、第2の配線と第2の配線よりも上層の第4の配線とを接続する第2のビアの形成位置と第4の配線の端部との間隔よりも小さい。第1のビア221aの半導体基板と平行な方向の断面積は、第2のビアの半導体基板と平行な方向の断面積よりも大きい。

(もっと読む)

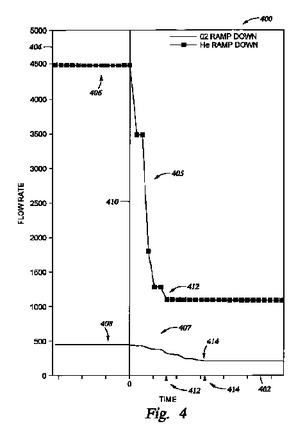

半導体装置及びその製造方法

【課題】配線が形成される多孔質絶縁膜がプラズマダメージ等を受けるのを防ぐことにより、高歩留り且つ高信頼性な半導体装置を得られるようにする。

【解決手段】半導体基板の上に、化学気相成長法により、炭素濃度、空孔形成剤濃度及び酸素濃度がそれぞれ異なる複数の領域を有する空孔形成剤含有膜を形成する工程を備えている。この工程は、前駆体、空孔形成剤及び酸化剤を第1の流量で流す第1の期間と、第1の期間の後に、前駆体の流量に対する空孔形成剤の流量を減少させる第2の期間と、第2の期間の後に、前駆体の流量に対する空孔形成剤の流量の減少を停止し、前駆体、空孔形成剤及び酸化剤を第2の流量で流す第3の期間と、第3の期間の後に、前駆体の流量に対する酸化剤の流量を増大させる第4の期間と、第4の期間の後に、前駆体、空孔形成剤及び酸化剤を第3の流量で流す第5の期間とを含む。

(もっと読む)

ハードマスク材料

【課題】集積回路製造工程のバックエンドプロセス、およびフロントエンドプロセスにおいて利用することができる、高硬度、且つ低応力のハードマスク膜を提供する。

【解決手段】ハードマスク膜は、応力が約−600MPaから600MPaの範囲内であり、硬度は少なくとも約12Gpaである。ハードマスク膜は、PECVD処理チャンバにおいて、高密度化プラズマ後処理を複数回行うことによって、ドープ済または未ドープのシリコンカーバイドの副層を複数成膜することによって得られる。ハードマスク膜は、SixByCz、SixByNz、SixByCzNw、BxCy、およびBxNyから成る群から選択される高硬度のホウ素含有膜を含む。ハードマスク膜は、ゲルマニウム含有率が少なくとも約60原子パーセントと、ゲルマニウム含有率が高いGeNxハードマスク材料を含む。

(もっと読む)

半導体装置

【課題】ワイヤボンディング接続されるパッケージに搭載される場合のワイヤ長を短くできる半導体装置を提供する。

【解決手段】本発明に係る半導体装置100は、シリコン基板103の内部素子領域153に形成された複数の素子と、シリコン基板103上に形成される配線層120と、配線層120を貫通し、内部素子領域153を囲む環状のシールリング101と、内部素子領域153の上方、かつ、配線層120上に形成され、複数の素子に含まれる第1素子と接続されるパッド102と、シールリング101上に形成され、当該シールリング101と接続されたパッド102aとを備える。また、シールリング101は、複数の素子に含まれる第2素子と接続されている。

(もっと読む)

膜形成用組成物、絶縁膜および半導体装置

【課題】低誘電率で、安定した絶縁性を示し、かつ、強度に優れ、膜厚や特性の不本意なばらつきが抑制された絶縁膜の形成に好適に用いることができる膜形成用組成物を提供すること。

【解決手段】本発明の膜形成用組成物は、分子内に、アダマンタン型のかご型構造を含む部分構造a1と、重合性の官能基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含むものであって、アセチレン結合を含むアセチレン系反応基を、分子内に複数個備えたオリゴアセチレン体を前記重合性化合物として含むとともに、前記オリゴアセチレン体が有する前記アセチレン系反応基の少なくとも一部が水素原子で置換された構造を有する水素化体を含み、前記重合性化合物が重合していない状態とした場合における、前記オリゴアセチレン体と前記水素化体の総モル数に対する、前記水素化体のモル分率が0.01〜10モル%であることを特徴とする。

(もっと読む)

堆積後ウエハ洗浄配合物

【課題】

【解決手段】基板の表面から金属キャッピング層の腐食生成物を洗浄するための方法およびシステムが提供されている。一実施形態によると、処理溶液は、界面活性剤、錯化剤、および、pH調整剤を含む。界面活性剤は、ウエハ表面を湿潤を改善し、キャッピング層のさらなる腐食を抑制するよう構成される。錯化剤は、基板表面から脱着した金属イオンと結合するよう構成される。pH調整剤は、基板表面からの腐食生成物の脱着を促進するために、pHを所望のレベルに調整するよう構成される。

(もっと読む)

半導体装置

【課題】 貫通穴の開口寸法が小さく小型化や微細化を容易にでき、貫通穴全体の金属層形成速度を向上する事が容易で、金属層形成工程に要する時間を短縮する事が容易な貫通穴形状を構成した半導体装置を提供することを目的とする。

【解決手段】 基板の表面と裏面とを接続する貫通穴内に金属層を設けた半導体装置において、貫通穴側壁に表面と裏面とを結ぶ向きに複数の突起を設けた事を特徴とする。

(もっと読む)

モリブデン系金属膜上の絶縁膜のドライエッチング方法および薄膜トランジスタパネルの製造方法

【課題】モリブデン系金属膜上の絶縁膜をドライエッチングする際に、選択比を比較的大きくする事ができる方法を提供する。

【解決手段】ドライエッチングにより、レジスト膜45の開口部46に対応する部分つまりソース電極9上におけるオーバーコート膜13にコンタクトホール14を形成し、また同時に、レジスト膜45の開口部47に対応する部分つまり金属膜21a上におけるオーバーコート膜13およびゲート絶縁膜4にコンタクトホール22を形成し、さらに同時に、レジスト膜45の開口部48に対応する部分つまり金属膜31a上におけるオーバーコート膜13にコンタクトホール32も形成する場合、エッチングガスとしてフッ素系ガス(SF6、CF4)、酸素ガスおよび窒素ガスからなる混合ガスを用いる事で窒化シリコン等からなるオーバーコート膜13とモリブデン系金属からなる金属膜31aとの選択比を大きくする。

(もっと読む)

表示装置

【課題】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を備えた表示装置であって、上記腐食防止用塗料の塗布や剥離といった更なる工程を設けることなく、ピンホール腐食を防止することのできる表示装置を提供する。

【解決手段】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を備えた表示装置であって、前記Al合金膜が、Niおよび/またはCoを0.15原子%以下(0原子%を含まない)、Geを0.2原子%以上2.0原子%以下、およびLa、Gd、NdおよびYよりなる群から選択される1種以上の元素を0.05原子%以上1.0原子%以下含有し、かつ、前記Al合金膜の表面において観察される腐食孔のアスペクト比(腐食深さ/腐食直径)が0.12以下であることを特徴とする表示装置。

(もっと読む)

半導体装置の製造方法

【課題】樹脂絶縁層の切削面に亀裂が生じて、絶縁信頼性が低下するのを抑制することのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板の主面上に形成した樹脂絶縁層を、バイトを用いた切削加工により一部除去する切削工程を備えた半導体装置の製造方法であり、切削工程として、表面に金属膜が積層された樹脂絶縁層の部分を切削する工程を含む。そして、金属膜が積層された樹脂絶縁層の部分を切削する際に、バイトの先端部及び該先端部の周辺部分に沿った樹脂絶縁層内の応力分布において、極大値の90%の幅が1.3μm以下となるように切削する。

(もっと読む)

141 - 160 / 1,081

[ Back to top ]