Fターム[5F033WW00]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273)

Fターム[5F033WW00]の下位に属するFターム

長さ、寸法 (1,572)

温度 (833)

濃度 (735)

圧力 (290)

流量 (142)

エネルギー (197)

電圧、電流 (63)

誘電率、容量 (247)

パラメータを工程途中で変化させるもの (113)

Fターム[5F033WW00]に分類される特許

121 - 140 / 1,081

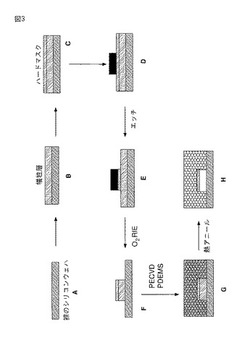

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

表示装置用Al合金膜

【課題】シリコン半導体層および/または透明導電膜との間のバリアメタル層を省略しても、AlとSiの相互拡散を抑制でき、低抵抗のオーミック特性を有する電気的接触が得られると共に、十分な耐熱性を有する表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜および/または薄膜トランジスタの半導体層と直接接続されるAl合金膜であって、Al合金膜は、30原子%以上のMoを含有するAl−Mo合金、またはMoと、Mn、Nd、Ni、Mg、およびFeよりなるX群から選択される少なくとも1種とを含有するAl−Mo−X合金の単層から構成されている。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

半導体装置およびその製造方法

【課題】Cuを主成分とする材料からなる最上層配線からのパッシベーション膜の剥離を防止することができる、半導体装置を提供する。

【解決手段】半導体装置1は、層間絶縁膜26と、絶縁材料からなり、層間絶縁膜26上に形成されたパッシベーション膜33と、銅を主成分とする材料からなり、層間絶縁膜26の表面とパッシベーション膜33との間に形成された最上層配線28と、アルミニウムを主成分とする材料からなり、パッシベーション膜33と最上層配線28の表面との間に介在され、最上層配線28の表面を被覆する配線被覆膜31とを含む。

(もっと読む)

半導体装置

【課題】電源電圧の電圧降下を抑制しつつ、信号配線リソースを大きく確保可能な電源配線構造を実現する。

【解決手段】第1配線層に、電源電位配線101a〜101dおよび基板電位配線102a〜102dが形成されており、配線層全体の真ん中より下層側の配線層に、電源ストラップ配線103a,103b,104a,104bが形成されている。上方ビア部114は、下方ビア部112よりも、電源ストラップ配線103a,103b,104a,104bが延びる方向における配置密度が低くなっている。

(もっと読む)

配線層の形成方法及び半導体装置の製造方法

【課題】信頼性の高い配線層を低コストで形成し得る配線層の形成方法を提供する。

【解決手段】基板10上に樹脂層12を形成する工程と、樹脂層12上にチタンを含む密着層14を形成する工程と、密着層14上にシード層16を形成する工程と、シード層16上に配線層22を形成する工程と、配線層22をマスクとしてシード層16をエッチングする工程と、一般式Ti(OR1)X(OYR2)4−X(但し、R1、R2はアルキル基又は水素であり、Xは1〜3の整数であり、Yは正の整数である)、又は、一般式Ti(OR3)4(但し、R3はアルキル基である)で表されるチタン有機化合物が添加されたエッチング液を用い、前記配線層22をマスクとして、前記密着層14をエッチングする工程とを有している。

(もっと読む)

表示デバイスおよびその製法、ならびにスパッタリングターゲット

【課題】アルミニウム合金膜と透明電極が直接コンタクトすることを可能とし、バリアメタルの省略を可能にするアルミニウム合金膜を用いた表示デバイスとその製造技術を提供すること。

【解決手段】ガラス基板上に配置された薄膜トランジスタと、透明電極によって形成された画素電極と、これら薄膜トランジスタと画素電極を電気的に接続するアルミニウム合金膜によって形成された接続配線部を主たる構成要素として備えた表示デバイスとその製法を開示する。

(もっと読む)

半導体チップ、半導体多層回路、及び、半導体チップの製造方法

【課題】表面から裏面に電気信号を伝播させる接続用配線を有する半導体チップを提供するにあたり、従来周知の半導体技術を利用して、製造時間やコストを増加させることなく、電気信号の減衰を抑制する。

【解決手段】半導体基板20と、表面配線30と、接続用配線40を備えている。半導体基板は、第1主表面20aから第2主表面20bに向けて面積が小さくなる開孔25を有している。表面配線は、半導体基板の第1主表面上に形成されている。また、接続用配線は、開孔の側面上に形成されていて、表面配線と接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】誘電率が低くかつ金属との密着性に優れた絶縁層を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板(シリコン基板)と、基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜12bと、多孔質SiOCH膜12bに設けられた凹部と、凹部を埋め込むように設けられた金属膜(Cu膜22b)と、Cu膜22bと接しており、凹部内の多孔質SiOCH膜12bの表面に設けられた、改質層31bと、を備え、改質層31bは、多孔質SiOCH膜12bの内部と比較して、C/Si比が小さく、かつO/Si比が同等である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】低誘電率の絶縁膜を備える一方で、当該絶縁膜上に選択的に設けられたキャップ層を備えておらず、信頼性に優れた半導体装置を効率よくかつ確実に製造することができる製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて、膜厚の2分の1以上の最大押し込み深さにおいて、弾性率測定変位を膜厚の10分の1とする、ナノインデンターを用いた測定から求められる弾性率が、4.0GPa以上である絶縁膜を形成する工程を有する一方で、絶縁膜上にキャップ層を形成する工程を有していない。

(もっと読む)

絶縁膜および半導体装置

【課題】誘電率の低い絶縁膜であって、半導体装置の製造においてCMP法により当該絶縁膜上の膜を好適に除去することができるとともに、キャップ層を備えておらず、かつ、信頼性に優れた半導体装置の製造に好適に用いることができる絶縁膜を提供すること。

【解決手段】本発明の絶縁膜は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて形成された絶縁膜であって、0.03〜20μmの膜厚を有し、ナノインデンターを用いて、膜厚の2分の1以上の最大押し込み深さにおいて、弾性率測定変位を膜厚の10分の1とする測定から求められる弾性率が、4.0GPa以上であることを特徴とする。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】長期にわたって信頼性に優れた半導体素子及びその製造方法を提供する。

【解決手段】基板の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板1の表面にレジスト組成物を塗布し、プリベークしてレジスト膜10を形成し、該レジスト膜10を貫通して第1表面電極1上にコンタクトホールを形成し、このコンタクトホール内にコンタクト電極4を形成し、第1表面電極2が形成された基板の表面に、熱膨張率が2ppm/℃以上7ppm/℃未満の第1絶縁膜3aを形成し、次いで、該第1絶縁膜3a上に熱膨張率が7ppm/℃以上24ppm/℃以下の第2絶縁膜3bを積層して絶縁膜3を形成し、コンタクト電極4を介して絶縁膜上に第2表面電極5を形成し、第1表面電極2、第2表面電極5及び絶縁膜3が形成された基板の裏面側を支持体に固定し、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

表示装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Ta、Nb、Re、Zr、W、Mo、V、Hf、Ti、CrおよびPtよりなる群(X群)から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置用Al合金膜である。

(1)Alと、X群から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含む第1の析出物について、円相当直径20nm以上の析出物が500,000個/mm2以上の密度で存在する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】絶縁膜の比誘電率を容易かつ十分に低下させる。

【解決手段】半導体装置の製造方法では、それぞれ環状SiO構造を主骨格とし互いに構造が異なる2種類以上の有機シロキサン化合物原料を混合した後で気化する。又は、それら2種類以上の有機シロキサン化合物原料の混合と気化とを一度に行うことによって、気化ガスを生成する。そして、その気化ガスをキャリアガスとともに反応炉に輸送する。そして、反応炉にてその気化ガスを用いたプラズマCVD法又はプラズマ重合法によって多孔質絶縁膜を成膜する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】基板を薄板化しても基板の反りを抑制でき、耐熱性、機械特性に優れた絶縁膜で保護された半導体素子及びその製造方法を提供する。

【解決手段】基板1の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板の表面に、芳香族テトラカルボン酸及び芳香族テトラカルボン酸二無水物から選ばれる1種以上のアシル化合物を、前記芳香族ジアミンよりも1モル%以上多く反応して得られるポリアミド酸を含むポリイミド前駆体組成物を塗布し、イミド化して絶縁膜3を形成し、第1表面電極2及び絶縁膜3が少なくとも形成された基板1を、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

半導体装置

【課題】並列に並ぶゲートパターンを有する半導体装置において、ゲートパターンのレイアウトを工夫することによって、光近接効果を補正しつつ、集積度を向上させる。

【解決手段】並列に並ぶゲートパターン21,22の端部と、並列に並ぶゲートパターン23,24の対向端部とにおいて、ゲートパターン21の端部はゲートパターン22の端部よりもゲートパターン23,24の方に突き出ており、ゲートパターン24の対向端部はゲートパターン23の対向端部よりも、ゲートパターン21,22の方に突き出ている。引っ込んでいる方の、ゲートパターン22の端部およびゲートパターン23の対向端部について、仕上がり形状において後退が生じない程度に、補正量を大きく設定することができる。

(もっと読む)

半導体装置の製造方法

【課題】配線とコンタクトプラグの短絡を効果的に防止する。

【解決手段】半導体装置の製造方法は、隣り合う配線の間に位置する層間絶縁膜内に、配線が露出した第1のコンタクトホールを含む複数のコンタクトホールを形成する。次に、(i)配線の露出した側面が、第1のコンタクトホールの第1の絶縁膜から構成される内壁側面と実質的に同一面となるか、又は(ii)第1のコンタクトホールの内壁側面において配線の露出した側面が窪んだ凹形状が形成されるように、露出した前記配線の一部を除去する。この後、コンタクトホールの内壁側面上にサイドウォール膜を形成後、コンタクトホール内に導電材料を充填することによりコンタクトプラグを形成する。

(もっと読む)

紫外線硬化型インクジェット記録用インク、それから得られた絶縁膜、電子素子及び電子素子の製造方法

【課題】 合成樹脂基板及び電極の両方に対するレベリング性に優れ、平滑性及び絶縁性に優れた硬化膜が得られる紫外線硬化型インクジェット記録用インク、それから得られた絶縁膜、電子素子及び電子素子の製造方法を提供する。

【解決手段】 エネルギー線硬化性化合物、光重合開始剤、及び表面張力調整剤を含有し、硬化性を有さないポリマーを含まず、25℃における粘度が100mPa・sec以下、表面張力が22〜35mN/m、かつインク硬化膜の体積抵抗率1013Ω・cm以上であり、絶縁破壊強度1.2MV/cm2以上である、絶縁膜を形成するためのソルベントフリー紫外線線硬化型インクジェット記録用インク、それを硬化してなる絶縁膜等を提供する。

(もっと読む)

ダマシン処理によるサイドウォールポリマー用の洗浄溶液

【解決手段】ウエハ上の低誘電率材料及び相互接続材料に損傷を与えることなく、ウエハ上のダマシン処理によるサイドウォールポリマーを除去するための水性洗浄溶液及び洗浄溶液を用いる方法を記載する。 (もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置の信頼性を向上させる。

【解決手段】半導体基板1は、素子形成面である第1の面1a及びその反対側の第2の面1bを有する。第1の面1aから第2の面1bまで半導体基板1を貫通するように貫通孔20が形成されている。貫通孔20の内壁上に絶縁膜21及びバリア膜22が順次形成されている。絶縁膜21及びバリア膜22が形成された貫通孔20が埋まるように導電部23が形成されている。貫通孔20の周辺に位置する部分の半導体基板1における少なくとも第1の面1a側にゲッタリングサイト30が形成されている。

(もっと読む)

121 - 140 / 1,081

[ Back to top ]