Fターム[5F033WW00]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273)

Fターム[5F033WW00]の下位に属するFターム

長さ、寸法 (1,572)

温度 (833)

濃度 (735)

圧力 (290)

流量 (142)

エネルギー (197)

電圧、電流 (63)

誘電率、容量 (247)

パラメータを工程途中で変化させるもの (113)

Fターム[5F033WW00]に分類される特許

161 - 180 / 1,081

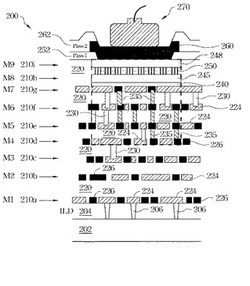

半導体装置のパッド構造

【課題】半導体装置のパッド構造を提供する。

【解決手段】半導体装置200は、半導体基板202、相互接続構造、複数のダミーメタルビア235及びパッド構造を備える。半導体基板202は、内部に複数の微小電子素子が設けられている。相互接続構造は、半導体基板202上に設けられ、複数の金属層210a〜210iと、金属層を隔離する複数のIMD層220とを有する。金属層210a〜210iは、最上金属層210iと、最下金属層210aと、最上金属層210iと最下金属層210aとの間に設けられた少なくとも2層の金属層とを含む。複数のダミーメタルビア235は、少なくとも2層の金属層間に設けられた1層又は2層以上のIMD層220内に形成される。パッド構造は、ダミーメタルビア235の上に直接設けられている。

(もっと読む)

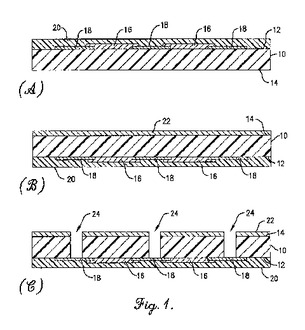

半導体装置の製造方法

【課題】樹脂絶縁層の切削面に亀裂が生じて、絶縁信頼性が低下するのを抑制することのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板の主面上に形成した樹脂絶縁層を、バイトを用いた切削加工により一部除去する切削工程を備えた半導体装置の製造方法であり、切削工程として、表面に金属膜が積層された樹脂絶縁層の部分を切削する工程を含む。そして、金属膜が積層された樹脂絶縁層の部分を切削する際に、バイトの先端部及び該先端部の周辺部分に沿った樹脂絶縁層内の応力分布において、極大値の90%の幅が1.3μm以下となるように切削する。

(もっと読む)

成膜方法及びプラズマ処理装置

【課題】シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させることが可能な成膜方法である。

【解決手段】真空排気が可能になされた処理容器22内で被処理体Wの表面に対して薄膜を形成する成膜方法において、原料ガスを用いて処理容器内でプラズマCVD法により薄膜としてチタンを含む金属膜8を形成する金属膜形成工程と、処理容器内で金属膜に対してアニール処理を行うアニール工程とを有する。これにより、シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させる。

(もっと読む)

集積回路および集積回路の製造方法

【課題】トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成する方法を提供する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

(もっと読む)

半導体素子の製造方法

【課題】 デュアルダマシンプロセスを同一チャンバ内で行っても、再現性よくビアホールを貫通させる技術が望まれる。

【解決手段】 層間絶縁膜上の第1のマスク膜及び層間絶縁膜に、層間絶縁膜の厚さ方向の途中まで達するビアホールを形成する。第1のマスク膜の上に、下層レジスト膜を形成し、その上に、配線溝に対応する開口を有する第2のマスク膜を形成する。チャンバ内において、O2とCOとのプラズマを用い、下層レジスト膜をエッチングするとともに、ビアホール内の一部には、下層レジスト膜を残す。下層レジスト膜の開口の平面形状が転写された開口を、第1のマスク膜に形成するとともに、下層レジスト膜を除去し、ビアホールをさらに掘り下げて、下層配線を露出させる。層間絶縁膜を厚さ方向の途中までエッチングして配線溝を形成する。配線溝及び前記ビアホール内を、導電部材で埋め込む。

(もっと読む)

基板製造方法及び基板

【課題】CMPの処理時間を短縮する。

【解決手段】基板製造方法は、基板上に絶縁層を形成する工程と、絶縁層上に第1のマスクを形成する工程と、第1のマスクを介して絶縁層をエッチングすることにより絶縁層に溝を形成する工程と、第1のマスクを除去する工程と、絶縁層上及び溝の表面に第1の金属層を形成する工程と、溝の内部及び上方に第2のマスクを形成する工程と、第1の金属層上及び第2のマスクの表面に第2の金属層を形成する工程と、第2のマスク及び第2のマスクの表面に形成された第2の金属層を除去する工程と、溝の上方が開口された第3のマスクを第2の金属層上に形成する工程と、溝の内部及び上方に第3の金属層を電界めっきにより形成する工程と、第3のマスクを除去する工程と、第3の金属層を化学機械研磨により平坦化する工程と、を備える。

(もっと読む)

3次元半導体装置および3次元半導体装置の冷却方法

【課題】回路設計に対する制限を低減するか解消し3次元回路内のホットスポットを効率的に冷却する3次元半導体装置。

【解決手段】 チップを貫通する貫通電極を有する複数の半導体チップ1を積層してなる3次元半導体装置であって、前記貫通電極として、異種の第1、第2の材料で構成された第1、第2の貫通電極(4、5)を備え、前記第1、第2の貫通電極とそれぞれ電気的に接続され、前記第1、第2の貫通電極とそれぞれ同種の材料からなり、チップの回路面上に配置され、前記回路面上で接続された第1、第2の表面配線を有し、前記第1の貫通電極、前記第1の表面配線、前記第2の表面配線、前記第2の貫通電極に沿って電流を流すことにより、前記回路面上の前記第1の表面配線と前記第2の表面配線との接合部(2)でペルチェ吸熱が行われる。

(もっと読む)

半導体装置の製造方法

【課題】低誘電率膜に対するUVキュア処理による低誘電率膜の下で且つ配線の上に形成されるライナ膜とその下層の膜との間の界面剥離を、UVブロッキング膜を用いずに防ぐことにより、高歩留まりの配線構造を有する信頼性が高い半導体装置を得られるようにする。

【解決手段】基板の上に、第1の絶縁膜11を形成し、形成した第1の絶縁膜11の上部に第1の金属配線12を形成し、第1の絶縁膜11の上に、第1の金属配線12を覆うように第2の絶縁膜13を形成し、第2の絶縁膜13に対して膜質の改質処理を行う。その後に、第2の絶縁膜13の上に第3の絶縁膜14を形成し、形成した第3の絶縁膜14に対してキュア処理を行う。

(もっと読む)

銅プラグを有する半導体デバイスおよびデバイスを形成するための方法

【課題】絶縁層がデバイスの最終配線層と接触する銅プラグを有する、半導体デバイスを提供する。

【解決手段】銅プラグと絶縁層とを分離する障壁層も存在可能である。他の実施形態では、絶縁層と銅プラグとの間にアルミニウム層も存在可能である。半導体デバイスを生成するためのプロセスも開示される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 デュアルダマシン法を用いて銅の埋め込み配線および接続プラグを形成するとき、接続プラグ中のボイド発生を防止する。

【解決手段】 Low−k膜13、15、ELK膜14、TEOS膜16からなる層間絶縁膜にプラグとなる接続孔19aを形成した後、酸素プラズマ処理を行って変質層20を形成し、この層を薬液処理により選択的に除去すると、ELK膜14が多孔質であることに起因してその側壁21にLow−k膜13、15などより大きい角度のテーパーが形成される。次に配線埋め込み用の溝の底面がELK膜14中にくるように形成して、プラグ開口の入口が広がる形状にした後、銅膜を埋め込む。

(もっと読む)

回路基板の貫通電極の形成方法

【課題】基板上の微細な貫通孔へ貫通電極となる金属を充填する方法であって、基板への熱的影響を軽減することができ、且つ、効率的な製造を可能とする方法を提供する。

【解決手段】本発明は、貫通孔を有する基板の貫通孔に導電性金属を充填する貫通電極の形成方法であって、所定の純度及び粒径の金属粉と有機溶剤とからなる金属ペーストを用いるものである。このとき、金属ペーストに周波数60Hz〜100kHzの機械的振動を印加しながら基板に塗布し、金属ペーストの塗布と同時、又は、金属ペーストの塗布後に貫通孔を他端側から減圧して金属ペーストを貫通孔内に吸引し、その後金属ペーストを焼結して貫通電極とする。この金属ペーストの塗布は、機械的振動が印加されたブレードを基板と非接触な状態で移動させることが好ましい。

(もっと読む)

ドライエッチング方法

【課題】低誘電率を有する多孔性の絶縁膜における比誘電率の増大を抑制可能なドライエッチング方法を提供する。

【解決手段】

比誘電率が2.2以下である多孔性、且つ低誘電率の絶縁膜Iを誘導結合プラズマによってエッチングするに際し、一般式CaFbXcにて表されるフルオロカーボン系のガス、又はC4F8をエッチングガスとして用いるとともに、該エッチングガスの圧力を0.5Pa〜5.0Paに維持する。加えて、高周波アンテナ30に100W〜600Wの範囲で13.56MHzの高周波電力を印可してエッチングガスを用いたプラズマを誘起する。上記絶縁膜Iを有する基板Sをこのプラズマに曝しつつ、該基板Sに対し50W〜300Wの範囲で13.56MHzの高周波電力を印可することにより、プラズマ中のイオン成分によるエッチング反応が支配的となる条件で絶縁膜Iをエッチングする。

(もっと読む)

無電解銅めっき液、無電解銅めっき方法、及び埋め込み配線の形成方法

【課題】孔の内径の大小にかかわらず、該孔の奥まで均一な無電解銅めっき層を形成しうる無電解銅めっき液および無電解銅めっき方法を提供する。また、該無電解銅めっき層を形成することにより孔の内部に信頼性の高い埋め込み配線を形成することのできる埋め込み配線の形成方法を提供する。

【解決手段】チオール基又はジスルフィド結合を有するポリエチレングリコール化合物、及び銅イオンを含有することを特徴とする無電解銅めっき液、さらに、該無電解銅めっき液に、孔2の形成された基板1を浸漬し、該孔の内部に無電解銅めっき層6を形成することを特徴とする無電解銅めっき方法、及び、該無電解銅めっき液に、孔2の形成された基板1を浸漬し、該孔の内部に無電解銅めっき層6からなる埋め込み配線を形成することを特徴とする埋め込み配線の形成方法。

(もっと読む)

配線パターン形成方法および半導体装置の製造方法、半導体装置、データ処理システム

【課題】2回のリソグラフィ工程によるSADP法(Self Align Double Patterning)を用いて、第1配線パターン形成領域には解像限界未満のパターンを含む第1配線パターンを形成し、第2配線パターン形成領域には解像限界以上の通常パターンからなる第2配線パターンを簡便に形成する方法を提供する。

【解決手段】解像限界未満の寸法を有する複数の配線を含む第1配線パターンを、第1リソグラフィ工程と第1リソグラフィ工程の後に実施される第2リソグラフィ工程を用いて形成し、第1のリソグラフィ工程で形成されたパターンに対してのみサイドウォールの形成および除去処理を行い、その後、解像限界以上のパターンを生成する第2リソグラフィ工程を実施する。第2のリソグラフィ工程で形成される解像限界以上の通常パターンに対しては、単純なリソグラフィ工程とすることが可能となる。

(もっと読む)

背面処理中に前面側電気回路を保護するための耐傷性コーティング

マイクロエレクトロニクスメカニカルおよび半導体デバイス特徴の前面側を保護する、耐傷性コーティングを、その使用方法とともに提供する。上記コーティングは、非感光性で、除去可能であり、高い処理温度に耐える。また、これらのコーティングは、デバイス設計において、別個のエッチング停止層を不要とする。上記コーティングは、溶媒系に溶解または分散した成分を含有する組成物から形成される。上記成分は、スチレンアクリロニトリル共重合体および芳香族スルホンポリマーからなる群から選択される。  (もっと読む)

(もっと読む)

回路基板

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】例えば、開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の欠けや割れが抑制される半導体装置の製造方法を提供する。

【解決手段】半導体基板1の表面1aに、外周端部から内側に向かって所定の幅を有して外周端部に沿って延在するパッシベーション膜3を形成する。半導体基板1の外周端部を研削することにより、表面1aおよび裏面1bと直交する外周端面1cを形成する。裏面1bを研削することにより、半導体基板1の厚みを所定の厚みにまで薄くする。研削された裏面を上方に向けた状態で、半導体基板1を回転させながら裏面上に混酸を吐出することにより、裏面にエッチング処理を施して破砕層を除去する。

(もっと読む)

透明電極、有機エレクトロルミネッセンス素子、および有機薄膜太陽電池素子

【課題】重合体を透明電極に含有させた場合、高温高湿環境、硫化水素ガス環境下における環境試験後でも高い導電性を有し、安定性に優れた透明電極を提供する。

【解決手段】透明導電膜上に少なくとも導電性繊維11を含む透明導電層31を有する透明電極であって、該導電層に、重合体の繰り返し単位の中に、下記一般式(1)で表される構造の少なくとも1種を含有する重合体を含有する透明電極。

(式中、R101は重合性基を部分構造として有する基であり、Z1は置換、未置換の単環または縮環の含窒素芳香族ヘテロ環を表す)

(もっと読む)

等方性銅エッチングのためのエッチング調合物

【課題】調合物及び等方性銅エッチング調合物を利用して銅を等方的にエッチングして除去する方法を提供する。

【解決手段】銅をエッチングする調合物は、水溶液を含み、水溶液は、(a)ジアミン、トリアミン、および、テトラミンからなるグループから選択される二座配位子、三座配位子、四座配位子の錯化剤、および、(b)酸化剤を含む。水溶液のpHは、5から12である。一実施形態では、エッチ液は、pH約6から10のエチレンジアミン(EDA)および過酸化水素を含む。銅層の実質的な表面を粗くせずに高速で銅をエッチングすることができる(例えば少なくとも約1,000Å/分)溶液が提供される。調合物は、半製品の半導体デバイスから銅を除去する(例えば銅積載部分をエッチングする)のに特に有益に用いられる。

(もっと読む)

半導体装置の製造方法

【課題】 広範囲にわたって全導電性領域に、断切れ及び上層配線層との間のリーク電流の発生のない、均一な膜厚の銅配線層を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】 ガラス基板上に薄膜トランジスタ及び配線を有する半導体装置を製造する方法において、ガラス基板上に下地絶縁層を形成する工程と、前記下地絶縁層上に下地バリア層を形成する工程と、前記下地バリア層上にシード層を形成する工程と、前記シード層を前記配線に対応する形状にパターニングしてシード層パターンを形成する工程と、前記シード層パターンの表面に銅配線層を無電解めっき法で形成する工程と、前記銅配線層マスクとして前記下地バリア層をパターニングする工程と、前記銅配線層を被覆するように絶縁層を形成する工程とを備えたことを特徴する半導体装置の製造方法。

(もっと読む)

161 - 180 / 1,081

[ Back to top ]