Fターム[5F044LL01]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630) | 直接ハンダ付け状態 (1,160)

Fターム[5F044LL01]の下位に属するFターム

基板の貫通孔を介してハンダ付け (18)

Fターム[5F044LL01]に分類される特許

201 - 220 / 1,142

高い電流許容能力を有するラテラル半導体構成エレメント用のスケーラビリティを有する構造

本発明は、半導体部品、特に、高い電流許容能力を有するラテラル半導体構成エレメント用のスケーラビリティを有する構造に関する。本発明に係るある一つのトランジスター・セルは、一つの制御端子、多数のスプリング・フィールド、並びに、多数のシンク・フィールドを包含している。尚、該制御端子は、少なくとも一つのスプリング・フィールド、或いは、シンク・フィールドを完全に取り囲んでいる。また本発明に係るある一つのトランジスターは、複数のトランジスター・セルを基質上に有しているが、各々のトランジスター・セルは、一つのスプリング・コンタクト・フィールド、及び/或いは、一つのシンク・コンタクト・フィールドを包含している。スプリング・コンタクト・フィールドは、基質の裏側において互いに導通するようにつながれており、シンク・コンタクト・フィールドも、基質の裏側において互いに導通するようにつながれている。本発明に係るトランジスターの製造方法は、以下の工程を包含している:基質を準備する;基質上に、一つの制御端子、多数のスプリング・フィールド、多数のシンク・フィールドを有する多数のトランジスター・セルを形成する;制御端子を互いに導通するようつなぐ;各トランジスター・セルにスプリング・コンタクト・フィールド、及び/或いは、シンク・コンタクト・フィールドを形成する;各トランジスター・セルのスプリング・フィールドとスプリング・コンタクト・フィールドを導通するようにつなぐ;各トランジスター・セルのシンク・フィールドをシンク・コンタクト・フィールドと導通するようにつなぐ;少なくとも一つのバンプを各スプリング・コンタクト・フィールドと各シンク・コンタクト・フィールドに形成する;配線基板を用意する;スプリング・コンタクト・フィールドのバンプを互いに導通するように配線基板上の配線路を介して接続する;そして、シンク・コンタクト・フィールドのバンプを互いに導通するように配線基板上の配線路を介して接続する。このようなバンプと配線基板上の配線路の配置により、ワイヤー・ボンディングが半導体表面に設けられることを低減できる。スプリング・フィールド、シンク・フィールド及び制御端子のバンプに対する本発明に係る配置は、アクティブなトランジスター領域とバンプ間の熱抵抗を低減できるものである。  (もっと読む)

(もっと読む)

接着剤組成物、半導体装置の製造方法、及び、半導体装置

【課題】ボンディング時にバンプ間にボイドを生じにくく、耐リフロー性及び信頼性に優れた半導体装置を製造するために用いることのできる接着剤組成物を提供する。また、該接着剤組成物を用いた半導体装置の製造方法、及び、該半導体装置の製造方法を用いて製造される半導体装置を提供する。

【解決手段】熱硬化性化合物と、前記熱硬化性化合物と反応可能な官能基を有するポリマーと、熱硬化剤とを含有する接着剤組成物であって、ボンディング温度での溶融粘度が10Pa・s以上15000Pa・s以下であり、ボンディング温度でのゲルタイムが10秒以上であり、かつ、240℃でのゲルタイムが1秒以上10秒以下である接着剤組成物。

(もっと読む)

半導体装置および半導体装置の接続体

【課題】突起電極を高くすることなくその径を大きくとることができ、かつ、突起電極間や突起電極と半導体基板上の半導体回路との絶縁を確保することができる半導体装置、および、この半導体装置が接合された接続体を提供すること。

【解決手段】半導体基板1上に形成された複数の外部接続電極2と、前記外部接続電極2の一部を開口部4から露出させて形成されたパッシベーション膜3と、前記パッシベーション膜3の前記開口部4上に形成された下地電極5と、前記下地電極5上に形成されたはんだ突起電極6とを備え、前記はんだ突起電極6の表面が、前記半導体基板1の表面から略同じ高さに位置する平坦面を形成し、前記はんだ突起電極6の周囲を囲むように形成された枠状樹脂膜7が、前記パッシベーション膜3上に形成された面状樹脂膜8と一体化されている。

(もっと読む)

半導体装置の製造方法

【課題】

金バンプを備えたLED素子を粘着シート上に配列させ、この粘着シートを集合基板に重ね、LED素子群を同時にフリップチップ実装する際、加圧加熱ヘッドを使うと接続状態が安定しなかった。

【解決手段】

金バンプ34,35を備えたLED素子13を粘着シート81上に配列させる(a)。この粘着シート81を集合基板84に重ねる(c)。この集合基板84を上板87と下板88を備える加圧治具89に収納する(d)。この加圧治具89をベルト炉95で加熱する。すなわち加圧治具89ごと集合基板84やLED素子13を加熱すると接合部の温度が安定し接続状態が改善する。

(もっと読む)

結合強度を向上させるためのダイの表面処理

電子パッケージシステムにおける改良された接着のための表面処理を提供する。本方法は、結合面上にパッシベーション層を堆積するステップと、パッシベーション層の少なくとも一部を粗面化するステップとを含む。パッシベーション層上に被覆材料を堆積する。結合面は、半導体またはパッケージ基板の一部であり得る。粗面化工程は、化学的または機械的工程によって実施することができる。別の実施形態では、電子パッケージシステムは、半導体またはパッケージ基板の結合面を備える。結合面上にはパッシベーション層が堆積され、接着力の向上のために粗面化されている。パッシベーション層の粗面化された部分の上に被覆材料が堆積されている。  (もっと読む)

(もっと読む)

電子装置、基材、およびパッドのレイアウト方法

【課題】基板上に電子部品を搭載した構成において、基板と電子部品との間の間隙をむらなく洗浄液で洗浄する。

【解決手段】一面110aに形成された複数のパッド120を含み、一面110aに電子部品を搭載するための基材(110)において、複数のパッド120は、x方向に直線状に配置された複数のパッド120をそれぞれ含む第1のパッド列L1および第2のパッド列L2を含む。第1のパッド列L1および第2のパッド列L2は、y方向に沿って隣接して配置され、第2のパッド列L2は、第1のパッド列L1内で隣接するパッドP1およびパッドP2間のy方向に沿った延長線上に配置されたパッドP3を含み、x方向において、パッドP3の中心位置は、パッドP1およびパッドP2間の中心位置と重ならない。

(もっと読む)

実装体の製造方法および実装装置

【課題】接続信頼性の高い実装体を製造する。

【解決手段】基板の電極および電子部品の電極の少なくとも一方の表面に半田が設けられており、基板、絶縁性接着層、および電子部品をこの順で積層させる積層段階と、基板に対して電子部品を押圧することにより、絶縁性接着層を貫通させて電子部品の電極と基板の電極とを接触させる押圧段階と、絶縁性接着層を第1の温度に加熱することにより、絶縁性接着層を熱硬化させる熱硬化段階と、半田を第2の温度に加熱することにより、基板の電極と電子部品の電極との間に、半田を含む金属結合層を形成する金属結合段階とを備える。

(もっと読む)

ボンディング装置

【課題】

ボンディングヘッドに取り付けたストッパと、独立昇降可能なストッパ受け部の距離を検出しながらストッパ受け部の高さを制御し、ボンディングヘッドが熱の影響を受けて膨張し、ストッパとストッパ受け部との距離が広がったとしても、検出し、設定した距離に制御する。

【解決手段】

電子部品を基板に加熱圧着するボンディング装置に次の手段を採用する。

第1に、ボンディングヘッドに設けられたストッパと、ボンディングヘッドの下降高さを規制するストッパ受け部と、両者の距離を検出する距離検出手段と、ストッパ受け部をボンディングヘッドと独立して昇降させる昇降手段と、この昇降手段を制御する制御手段とを設ける。

第2に、電子部品を基板に加熱圧着してバンプが溶解するまで、距離検出手段からの信号によりストッパとストッパ受け部との距離を所定距離に保つようストッパ受け部の高さを制御する。

(もっと読む)

回路基板組み立て品および回路基板へのチップの取り付け方法

【課題】アンテナアレイにおいて、送信/受信モジュールをアンテナ回路基板に容易に接続でき、製造時間とコストを削減できる手段を提供する。

【解決手段】アンテナアレイは、フリップチップ送信/受信(T/R)モジュール1をアンテナ回路基板2に直接取り付けることによって組み立てられる。フィレットボンド6は、フリップチップT/Rモジュール1の周辺の少なくとも一部の周囲において回路基板2およびフリップチップT/Rモジュール1に付けられる。

(もっと読む)

電子部品接合装置及び電子部品接合方法

【課題】接合材の潰れ形状を制御できるようにする。

【解決手段】接合ヘッド1に電子部品6を保持して電子部品6を基板5に搭載する電子部品接合方法において、電子部品6を基板5に搭載するときに、電子部品6が基板5に接触後、接合ヘッド1を基板5方向へ押し付ける荷重制御を開始し、接合ヘッド1の速度変化を抑える方向に接合ヘッド1の速度に応じた値にて加減した荷重指令値を作成し、この荷重指令値に基づいて接合ヘッド1を基板5方向に押し付け、接合ヘッド1は、電子部品6を基板5に押し付け電子部品6の備えた接合材7を介して搭載する、

(もっと読む)

ダイシングシート機能付き導電接続材料、端子間の接続方法及び電気、電子部品

【課題】 本発明の目的は、接続端子間において良好な電気的接続と隣接端子間において高い絶縁信頼性を得ることが可能で、且つ生産性に優れるダイシングシート機能付き導電接続材料を提供すること。また、本発明の別の目的は、上記導電接続材料を用いて電気的に接続されてなる、半導体装置を提供すること。

【解決手段】 本発明のダイシングシート機能付き導電接続材料は、ダイシングシートと、導電接続材料とが積層されてなるダイシングシート機能付き導電接続材料であって、前記導電接続材料が、樹脂組成物と、半田箔又は錫箔から選ばれる金属箔とから構成される積層構造を有することを特徴とする。また、本発明の半導体装置は、上記に記載のダイシングシート機能付き導電接続材料の導電接続材料を有することを特徴とする。

(もっと読む)

半導体装置

【課題】多ピンの半導体装置においてコストの低減化を図る。

【解決手段】フリップチップ接続タイプのBGAにおいて、多層配線基板の上面の外周部に配置された複数の信号用ボンディング電極2kが内側と外側に振り分けて引き出されており、内側に引き出された複数の信号用配線2uと接続する複数の信号用スルーホール2qが、複数の信号用ボンディング電極2kの電極列と複数のコア電源用ボンディング電極が配置された中央部との間の領域に配置されていることで、チップのパッドピッチを詰めることができ、前記多層配線基板の層数を増やすことなく、前記BGAのコストの低減化を図る。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】リッド(LID:蓋材)と配線基板との接着強度を高める。

【解決手段】半導体装置は、配線基板と、この配線基板に貼り付けられたリッドを備える。このリッドには、注入口部が設けられている。このリッドの内側には、この注入口部から樹脂が注入されている。このリッドと配線基板とは、注入された樹脂により固定されている。

(もっと読む)

半導体装置及びその製造方法

【課題】強度を維持し且つバンプ同士の間の狭ピッチ化に耐え得るバンプ及びアンダーバリアメタル構造を得られるようにする。

【解決手段】半導体装置は、半導体チップ1と、半導体チップ1の上に形成された電極パッド2と、電極パッド2の上に形成されたアンダーバリアメタル10と、アンダーバリアメタル10の上に形成されたはんだバンプ6と、アンダーバリアメタル10及びはんだバンプ6の周囲を覆うように形成されたアンダーフィル材18とを有している。はんだバンプ6は、アンダーバリアメタル10との接合界面が該アンダーバリアメタル10の上面であり、アンダーフィル材18は、バンプ6の側面とアンダーバリアメタル10の端面との接合部分における角度が直角又は鈍角である。

(もっと読む)

半田拡散保護を伴う半導体チップデバイス

【解決手段】

半田型熱インタフェース材質(90)を用いて半導体デバイスのために熱的な経路を確立するための種々の方法及び装置が提供される。1つの態様に従うと、基板と基板内へ第1の距離だけ延びる第1のアクティブ回路部分(40)とを有する第1の半導体チップ(20)を提供することを含む製造の方法が提供される。第1のアクティブ回路部分(40)を包囲するが第1のアクティブ回路部分(40)からは横方向に隔てられ且つ基板内へ第1の距離よりも大きい第2の距離だけ延びるバリア(135)が第1の半導体チップ(20)内に形成されて、半田の拡散を抑制する。

(もっと読む)

面実装部品のはんだ付け方法および面実装部品

【課題】ダイボンド用はんだ材料を使用して形成された面実装部品を、実装用はんだ材料を使用してプリント基板にはんだ付けするときでも、ダイボンド用はんだ材料の溶解が起きないようにした。

【解決手段】ダイパット用はんだ材料30として、Cuの含有量が所定値以下のSnを主成分とする(Sn−Sb)系の高融点はんだ材料を使用して形成された面実装部品を、回路基板の基板端子部に塗布された実装用はんだ材料70として、(Sn−Ag−Cu−Bi)系はんだ材料を用いてはんだ付けする。ダイボンド用はんだ材料30の固相線温度は243℃であり、実装用はんだ材料70の液相線温度は215〜220℃程度であるので、リフロー炉の加熱温度(240℃以下)によってもダイボンド用はんだ材料30は溶解しない。

(もっと読む)

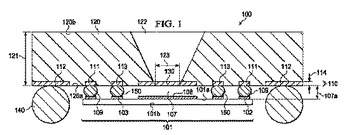

リードフレームベースのパッケージに統合された可動要素を有するマイクロエレクトロメカニカルシステム

MEMSデバイス(100)が集積回路チップ(101)と、リードフレームベースのプラスチック成形本体(120)を含むパッケージとを有し、パッケージは本体の厚み(121)を通る開口(122)を備える。可動フォイル部品(130)が本体(120)に固定され、開口(122)を少なくとも部分的に横切って延びうる。チップ(101)は、フォイルを横切って拡がるようにリード(110)にフリップ実装され、フォイル(130)からギャップにより隔てられうる。リードは、予め製造された個別部品のリードフレーム上にあってもよく、或いは犠牲キャリア上に金属を堆積し、その金属層をパターニングするプロセスフローによって製造されてもよい。その結果のリードフレームは平坦であってもよく、或いは積層型のパッケージ・オン・パッケージデバイスに有用なオフセット構造を有してもよい。  (もっと読む)

(もっと読む)

電極構造

【課題】鉛フリーはんだを用い、下地のNi層によらずに充分な接合強度を得る。

【解決手段】この電極構造10においては、電極下地11上に、Niめっき層12が形成されており、Niめっき層12上にCo薄膜層13が形成される。はんだ層20は、Niめっき層12上ではなく、Co薄膜層13上に形成される。このはんだ層20によって被接合試料30は、この電極構造10に接合される。Co薄膜層13は、10nm〜800nm程度の厚さであり、この厚さのCo薄膜層13は、蒸着法、スパッタリング法によって形成することができる。

(もっと読む)

半導体装置

【課題】半導体チップとその他の電子部品との間隔が小さくなりこれらが近接する場合であっても半導体チップを封止するアンダーフィルのフィレットの外縁部が電子部品に接触することを防止し、高密度なフリップチップ実装が可能な半導体装置を提供する。

【解決手段】半導体チップ2とインターポーザ7との間をアンダーフィル9で封止した半導体装置であって、半導体チップ2の端面部3の少なくとも一部に、水平方向よりもインターポーザ7側に向く面を有する水平方向の幅W1が10〜100μmの切込部4を設けたことを特徴とする。

(もっと読む)

はんだ接合補強剤組成物、及びこれを用いた実装基板の製造方法

【課題】電子部品搭載後の工程数を増やすことなく、高い接合強度が得られる上、はんだ付け性の低下を防止できるはんだ接合補強剤組成物、及びこれを用いた実装基板の製造方法を提供する。

【解決手段】本発明のはんだ接合補強剤組成物(5)は、その雰囲気温度を昇温開始温度である40℃から鉛フリーはんだ粉末のはんだ融点まで0.1〜0.2℃/秒の昇温速度で昇温し、続けて前記はんだ融点で10分間保持した際に、昇温開始直後から5〜7秒毎に粘弾性測定装置によりはんだ接合補強剤組成物(5)の粘度を測定した結果、昇温開始直後における粘度V1(Pa・s)と、昇温開始直後からはんだ融点までの昇温時における最低粘度V2(Pa・s)と、昇温後に前記はんだ融点で10分間保持した直後の粘度V3(Pa・s)とが、V2<V1/10かつV3>10V2の関係を満足することを特徴とする。

(もっと読む)

201 - 220 / 1,142

[ Back to top ]