Fターム[5F140BF14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 半導体 (411)

Fターム[5F140BF14]に分類される特許

81 - 100 / 411

半導体装置の製造方法

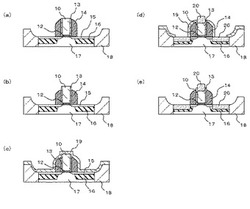

【課題】ポリシリコンゲート電極の意図しないフルシリサイド化を防止する。

【解決手段】基板17上に、ゲート絶縁膜12およびシリコン層10をこの順に積層した積層体(10、12)を形成する工程と、積層体(10、12)の側壁沿いにSiN膜を有するオフセットスペーサ13を形成する工程と、その後、シリコン層10の上面を、薬液を用いて洗浄する工程と、その後、少なくともシリコン層10の上面を覆う金属膜19を形成する工程と、その後、加熱する工程と、を有し、オフセットスペーサ13が有するSiN膜は、ALD法を用いて450℃以上で成膜されたSiN膜、または、1Gpa以上の引張/圧縮応力を有するSiN膜であり、前記薬液は、重量比率で、HF/H2O=1/100以上であるDHF、または、バッファードフッ酸である半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】 フィン型MISトランジスタ、プレーナ型MISトランジスタ及び抵抗素子を集積化した半導体装置において、的確な製造方法を提供する。

【解決手段】 フィン部10aを形成する工程と、フィン部の側面に第1のゲート絶縁膜14及び第1のゲート電極膜15を形成する工程と、フィン部並びにフィン部の側面に形成された第1のゲート絶縁膜及び第1のゲート電極膜を囲み、第1のゲート電極膜に接する半導体導電部16aを形成する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、第2のゲート絶縁膜20及び第2のゲート電極膜21を形成する工程と、半導体導電部上及び抵抗素子形成領域に形成された第2のゲート絶縁膜及び第2のゲート電極膜を除去する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、抵抗素子用の半導体膜を形成する工程とを備える。

(もっと読む)

半導体装置

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜、及び、ゲート電極としてメタル膜を含む半導体装置において、逆短チャネル効果の発生を防止して高性能化を実現する。

【課題手段】半導体装置は、半導体基板101の上に形成されたランタンを含有する高誘電率ゲート絶縁膜102と、高誘電率ゲート絶縁膜102の上に形成されたキャップ膜103と、キャップ膜103の上に形成されたメタル膜104と、メタル膜104の上に形成されたポリシリコン膜105と、高誘電率ゲート絶縁膜102、キャップ膜103、メタル膜104、及びポリシリコン膜105それぞれの両側面に形成されたランタンを含有するゲート側壁絶縁膜106とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加しつつ、基板やソース/ドレイン領域においてリーク電流の発生が効果的に抑制された半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の不純物を含み、素子形成領域170を有する半導体基板101と、素子形成領域170上にゲート絶縁膜132を挟んで形成されたゲート電極125と、ゲート電極125の両側方に形成され、第2導電型の不純物を含むソース/ドレイン領域150とを備える。素子形成領域170のうちゲート電極の両側方に位置する領域には、半導体基板101の主面に対して傾いた半導体単結晶のファセット面を露出させる側壁を有し、コーナー部が丸められたリセス130が形成されており、ソース/ドレイン領域150は、リセス130に埋め込まれたシリコン混晶で構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタに適当なしきい値電圧が与えられる一方、抵抗素子はシリコン膜からなる抵抗体層の異常成長を抑制して、シリコン膜の膜厚を安定化する。

【解決手段】半導体装置は、半導体基板10の上部に形成された素子分離領域12によって囲まれた第1の活性領域10a、第1の活性領域の上に形成された第1の高誘電体膜14aを有する第1のゲート絶縁膜27a、及び第1のゲート絶縁膜の上に形成された第1のゲート電極28aとを有する第1導電型の第1のMISトランジスタ1aと、素子分離領域の上に形成された第2の高誘電体膜14x、及び該第2の高誘電体膜の上に形成されたシリコンからなる抵抗体層20xを有する抵抗素子1xとを備えている。第1の高誘電体膜と第2の高誘電体膜とは、互いに同一の高誘電体材料からなり、第1の高誘電体膜は第1の調整用金属を含み、第2の高誘電体膜は第1の調整用金属を含まない。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

積層膜の形成方法

【課題】 各膜の組成が異なる積層膜を、極めて効率よく、しかも酸化等の不都合が生じることなく形成することができる積層膜の形成方法を提供すること。

【解決手段】 処理室内に基板1を配置し、処理室に、少なくとも、金属カルボニルを含有する原料を含む成膜原料を導入し、CVDにより基板1上に金属カルボニル中の金属を含む複数の膜6a、6bを含む積層膜を形成する積層膜の形成方法であって、上記積層膜に含まれる膜は、同一処理室内で、原料種および/または成膜条件を異ならせて連続成膜され、上記膜の組成が異なる積層膜を形成する。

(もっと読む)

二種類の仕事関数メタルを備える半導体装置

【課題】高誘電率ゲート絶縁膜を備える半導体装置の閾値電圧を適切に制御すること。

【解決手段】半導体装置の形成方法は、仕事関数メタルを含むダミーメタルゲート層をベース絶縁膜の直上に形成することと、アニーリングによって仕事関数メタルをベース絶縁膜中に拡散させることと、ウェットエッチングによってダミーメタルゲート層を除去することと、ベース絶縁膜211、212上に高誘電率ゲート絶縁膜213、213を形成することと、高誘電率ゲート絶縁膜213上にメタルゲート214、215を形成することと、を含む。

(もっと読む)

電界効果型トランジスタ、半導体メモリ、表示素子、画像表示装置及びシステム

【課題】比誘電率が高くリーク電流の少ない絶縁膜を提供する。

【解決手段】基板と、前記基板上に形成されたソース電極、ドレイン電極、及びゲート電極と、前記ゲート電極に所定の電圧を印加することによりソース電極とドレイン電極との間にチャネルが形成される半導体層を有し、前記ゲート電極と前記半導体層の間にゲート絶縁層と、を備え、前記ゲート絶縁層は、アルカリ土類金属の中から選ばれた1または2種類以上の元素と、Ga、Sc、Y、及びCeを除くランタノイドの中から選ばれた1または2種類以上の元素とを含むアモルファス複合金属酸化物絶縁膜により形成されていることを特徴とする電界効果型トランジスタを提供することにより上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法、pチャネルMOSトランジスタ

【課題】nチャネルMOSトランジスタにおいてhigh−Kゲート絶縁膜をhigh−K誘電体膜と酸化ランタン膜の積層により構成した半導体装置において、酸化ランタン膜のパターニングプロセスを不要とする半導体装置の製造方法を提供する。

【解決手段】界面酸化膜22上に形成されたhigh−K誘電体膜23上に酸化膜24を形成する工程と、前記high−K誘電体膜に窒化物層25を形成する工程と、前記窒化物層および前記酸化膜を第1の素子領域21Aから選択的に除去し、第1および第2の素子領域21Bにわたり酸化ランタン膜26を形成し、前記第1の素子領域においては前記界面酸化膜と前記high−K誘電体膜と前記酸化ランタン膜を積層した第1の積層構造を、また前記第2の素子領域においては前記界面酸化膜と前記high−K誘電体膜と前記酸化膜と前記窒化物層と前記酸化ランタン膜を積層した第2の積層構造を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極抵抗の増大や工程数の増加を招くことなく、シリコン混晶層を用いた歪技術により、半導体装置の高性能化を実現する。

【解決手段】半導体基板100における第1のゲート電極106Aから見て第1の絶縁性サイドウォールスペーサ111Aの外側に第1のソースドレイン領域114Aを形成する。その後、半導体基板100における第2のゲート電極106Bから見て第2の絶縁性サイドウォールスペーサ111Bの外側にリセス部119を形成すると共に、第2のゲート電極106Bを部分的に除去する。その後、リセス部109内に、第2のソースドレイン領域114Bとなるシリコン混晶層120を形成する。

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】Geを含む半導体で構成されるチャネル領域を有するP型FETにおいて、逆短チャネル特性の発生を抑制しつつ、短チャネル特性を改善する。

【解決手段】半導体装置は、半導体基板100上に形成されたP型FETを備えている。P型FETは、半導体基板100上に形成され、Geを含有する第1の半導体層103と、第1の半導体層103上に形成され、第1の半導体層103よりも低濃度のGeを含有する第2の半導体層104と、第2の半導体層104上にゲート絶縁膜107aを間に挟んで形成されたゲート電極110aと、第2の半導体層104のうちゲート電極110aの両側方に位置する部分に形成されたp型エクステンション領域111aと、第1の半導体層103内に設けられ、且つp型エクステンション領域111aの下に形成されたn型不純物領域152とを有している。

(もっと読む)

GaN系MOS型電界効果トランジスタ

【課題】ノーマリオフ動作を可能にし、かつしきい値電圧を自由に制御出来るGaN系MOSFETを提供する。

【解決手段】p−GaNからなる電子走行層13とゲート電極18との間にゲート絶縁膜15が形成されたGaN系MOSFET10である。ゲート電極18は、AlGaInP混晶からなる。ゲート電極18は、p型AlGaInP混晶からなる第1のゲート層19と、この上に形成されたp型GaAsからなる第2のゲート層20と、この上に形成された金属層(AuGe/Au電極)21とを有する。AlGaInP混晶の混晶比を変化させることにより、しきい値電圧を制御することが出来る。

(もっと読む)

FINFETSおよびその形成方法

【課題】フィン電界効果トランジスタのソース/ドレイン構造を提供する。

【解決手段】基板上のフィンチャネル本体110a、110b、フィンチャネル本体110a、110b、上に配置されたゲート電極115、およびフィンチャネル本体110a、110b、に隣接して配置され、どのフィン構造も実質的に含まない、少なくとも1つのソース/ドレイン(S/D)領域120a,120b及び125a,125bを含むフィン電界効果トランジスタ(FinFET)。

(もっと読む)

半導体素子加工方法

【課題】本発明は、微細半導体素子の加工方法にかかわり、特に、通常high-k/メタルゲートと呼ばれる構造の素子の微細化に適した加工方法に関する。

【解決手段】Si基板上に形成されたHfあるいはZrを含む絶縁膜とその上層あるいは下層あるいは膜中に存在するMg,YあるいはAlとを含む堆積膜の除去を、ドライエッチングとウエットエッチングを、ウエットエッチングを先にして少なくとも1回繰り返して行う。

(もっと読む)

半導体装置及びその製造方法

【課題】MIPS構造等のゲート電極と同時形成が可能であり且つ抵抗が高い抵抗素子を有する半導体装置及びその製造方法を提供する。

【解決手段】基板上に金属含有膜108及びポリシリコン膜109を順次形成する工程と、前記金属含有膜及び前記ポリシリコン膜を抵抗素子形状にパターニングする工程と、前記金属含有膜の少なくとも一部分を除去することにより、前記ポリシリコン膜の下に中空領域119を形成する工程とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

81 - 100 / 411

[ Back to top ]