Fターム[5J055EZ00]の内容

電子的スイッチ (55,123) | 機能的回路 (8,211)

Fターム[5J055EZ00]の下位に属するFターム

積分回路、CR時定数回路 (122)

微分回路 (16)

定電流素子、定電流回路 (454)

カレントミラー回路 (261)

1、2石の増幅回路 (960)

オペアンプ、演算増幅器 (260)

比較器(デジタル、アナログ) (565)

シュミット回路 (46)

ゲート、トランスファーゲート (670)

マルチプレクサ (275)

フィルター、濾波器、共振回路 (166)

整流回路 (20)

クランプ、リミッタ (97)

スナバ回路 (31)

ブートストラップ回路 (94)

プリチャージ (38)

レベルシフト (258)

整合、インピーダンス変換 (20)

プルアップ、プルダウン (113)

変調、復調器、PWM (119)

A/D、D/A変換器 (155)

論理素子(INVは除く) (1,593)

CPU (177)

特定のIC、LSI (6)

機械要素 (139)

遅延素子、回路、デレイライン (226)

電源回路、特徴がある定電圧回路 (631)

2種以上のクロックを用いるもの (1)

機能的なダイオード (205)

表示装置、LED (102)

Fターム[5J055EZ00]に分類される特許

201 - 220 / 391

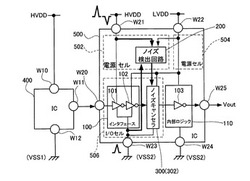

半導体集積回路装置および電子機器

【課題】半導体集積回路装置において、回路の占有面積の増大を最小限に抑えつつ、電源ノイズに起因する誤った信号の伝達を確実に防止し、ESDイミュニティを向上させること。

【解決手段】電源セル(502)内に電源ノイズ検出回路(200)を設ける。一方、I/Oセル506内にノイズキャンセラ(300)を設ける。電源ノイズ検出回路200によって、高レベル側電源電圧(HVDD)に重畳する正極性/負極性の電源ノイズ、および低レベル側電源電圧(VSS1)に重畳される正極性の電源ノイズのいずれかを検出し、ノイズキャンセラ300を動作させる。これによって、電源ノイズに起因する誤った信号の伝達が確実に阻止され、電子機器の重大な誤動作が防止される。

(もっと読む)

バッファ回路

【課題】トレードオフの関係にある低消費電流化とスルーレート特性をともに満足するバッファ回路を提供する。

【解決手段】入力信号の立ち上がり時と立ち下がり時の入力信号と出力信号との差電圧を検出する差電圧検出回路11、12を具備する。その差電圧に基づき電圧電流変換回路21、22は出力回路を構成する出力NMOSm1と出力PMOSm2へのバイアス電流を増加させて供給する。また、差電圧検出回路11、12は所定オフセット電圧を有し、差電圧がオフセット電圧以上、即ち、入力信号が急峻に変化(立ち上がり又は立ち下がり)した場合のみバイアス電流を増加させる。

(もっと読む)

論理回路

【課題】消費電力の変動を抑える論理回路を実現する。

【解決手段】所定の演算処理を行う論理回路1Aは、1又は2以上の2進数の入力データに対して、入力データのハミング重みと関係なく、ハミング重みが一定となる第1の複数のビットデータに変換するデコーダ400Aと、デコーダ400Aにより変換された第1の複数のビットデータを受信し、所定の演算処理のために、受信した第1の複数のビットデータのビット位置を入れ替えることによって、第1の複数のビットデータのビットパターンを変更して、第2の複数のビットデータを生成する配線ネットワーク200Aと、配線ネットワークに200A接続され、配線ネットワーク200Aにおいて生成された第2の複数のビットデータを、1又は2以上の2進数の出力データに変換するエンコーダ300Aとを有する。

(もっと読む)

負荷駆動回路

【課題】負荷駆動用のスイッチング素子のゲート−ソース間にクランプ回路を設けることなく、負荷駆動用のスイッチング素子として、ゲート−ソース間耐圧の低いスイッチング素子を用いる。

【解決手段】ドライブ回路11は、コンデンサ13によって供給される電源電圧以下の振幅で信号を出力し、コンデンサ13の端子間電圧がパワーMOSFET10のゲート−ソース間耐圧以下となるようにコンデンサ13の端子間電圧を固定する電位固定回路20を備える。

(もっと読む)

バッファ回路及びその制御方法

【課題】接地電位と電源ラインとの電位差を規定値に保ち、誤動作を防止することができるバッファ回路及びその制御方法を提供する。

【解決手段】出力スイッチング素子M1、M2と、出力スイッチング素子M1、M2を導通状態に制御する第1スイッチング回路M4、M5及び出力スイッチング素子を非導通状態に制御する第2スイッチング回路M3、M6を有し、第1スイッチング回路M4、M5と第2スイッチング回路M3、M6との接続点が出力スイッチング素子M1、M2に接続され、入力信号及び出力制御信号に応じ、出力スイッチング素子M1、M2を導通状態あるいは非導通状態に制御する出力スイッチング素子制御部20A、20Bと、第2スイッチング回路M3、M6に直列接続され、出力制御信号が入力信号の通過を禁止する出力禁止状態のときに出力スイッチング素子M1、M2の駆動能力を制限する駆動能力変更部30A、30Bと、を備える。

(もっと読む)

低電力センサシステム用の容量性インタフェース回路

本開示は、低電力システム用の容量性インタフェース回路を記載する。容量性インタフェース回路は、高分解能及び低電力で、微小電子機械システム(MEMS)ベースセンサのような静電容量ベース変換器のノイズが非常に低い検知を達成するように構成される。容量性インタフェース回路は、差動増幅器と、相関トリプルサンプリング(CTS)とを使用して、kT/Cノイズ、並びに増幅器オフセット及びフリッカ(1/f)ノイズを増幅器の出力から実質的に消去又は少なくとも低減する。容量性インタフェース回路は、増幅器出力における過渡現象を落ち着かせることを可能にすることによって出力信号におけるグリッチング、すなわち、クロック過渡現象を低減する出力段をさらに備えることができる。このように、低電力システムにおいて回路を使用して、安定した低ノイズ出力を生成することができる。 (もっと読む)

誘導性負荷の駆動装置

【課題】逆起電圧を吸収するに際しても発熱が生じるのを防止するようにした誘導性負荷の駆動装置を提供する。

【解決手段】外部供給電源12と誘導性負荷14の間に介挿される第1のスイッチング素子28、誘導性負荷14とアース24の間に介挿される第2のスイッチング素子30、第1のスイッチング素子28と誘導性負荷14との間で分岐してアース24に接続される電路40を有すると共に、第1のスイッチング素子28がオフ、第2のスイッチング素子30がオンされるとき、誘導性負荷14の逆起電圧によって生じる逆起電流をアース24に還流させる還流回路18、さらに誘導性負荷14と第2のスイッチング素子30との間で分岐して外部供給電源12に接続される電路44を有すると共に、第1、第2のスイッチング素子28,30がオフされるとき、逆起電流を外部供給電源12に還元する逆起電流還元回路20を備えるように構成する。

(もっと読む)

電圧駆動型半導体素子の駆動方法、及び、ゲート駆動回路

【課題】スイッチング損失の減少や、サージ電圧の低下を図ることができる新たな技術を提案する。

【解決手段】電圧駆動型半導体素子(IGBT1)の駆動方法であって、前記電圧駆動型半導体素子のターンオン又はターンオフの指令のタイミングからサージ電圧発生のタイミングまでのサージ期間(ターンオン時間tON/ターンオフ時間tOFF)を記憶し、次回のターンオン時又はターンオフ時において、今回記憶したターンオン時又はターンオフ時における前記サージ期間に基づいて、前記電圧駆動型半導体素子の実効ゲート抵抗値を変更する、こととするものである。

(もっと読む)

半導体集積回路

【課題】半導体集積回路の微小定電流源を共通化し小型化、低消費電力を図る。

【解決手段】発振回路400と、発振回路400で発振CLKが正しく行われているか否かを確認する発振停止検出回路300と、電源電圧VDDから一定電圧VRLを発生して発振回路400に一定電圧VRLを供給する定電圧発生回路200と、を有する半導体集積回路1であって、定電圧発生回路200と発振停止検出回路300に微小定電流Irefを供給する共通の微小定電流源100を有する。

(もっと読む)

パワー半導体の駆動回路およびその信号伝達方法

【課題】フォトカプラ等の高価な絶縁式の信号伝達手段を用いることなく、外部との間で絶縁しつつ信号を伝達することが可能なパワー半導体の駆動回路、およびパワー半導体の駆動回路の信号伝達方法を提供する。

【解決手段】駆動回路100に、外部から入力されたパルス信号を受信するトランス120と、前記パルス信号を増幅して増幅信号を生成するチョッパ型アンプからなる増幅回路130と、前記増幅信号のパルス幅を拡張して拡張信号を生成するピークホールド回路からなる拡張回路140と、前記拡張信号がセット入力端子に入力されるRSフリップフロップ回路150と、RSフリップフロップ回路150の出力信号に対して所定時間遅延した遅延信号を生成し、RSフリップフロップ回路150のリセット入力端子に入力する遅延回路160と、を具備した。

(もっと読む)

スイッチング素子駆動装置及びスイッチング素子駆動方法

【課題】本発明は、完全オン中の過電流に限らずターンオン初期の過電流に対しても適切な保護動作を実行することができる、スイッチング素子駆動装置の提供を目的とする。

【解決手段】パワー素子10がオフしないようにパワー素子10のゲート電圧を正常オフ時のゲート電圧の低下速度より速く低下させるトランジスタ24と、パワー素子10のゲート電圧を正常オフ時のゲート電圧の低下速度より遅く低下させるトランジスタ25とを有し、過電流検出手段26によってパワー素子10に過電流が検出された場合にトランジスタ24によってゲート電圧を低下させた後にトランジスタ25によってゲート電圧を低下させる、スイッチング素子駆動装置であって、ゲート電圧監視手段21によってゲート電圧が所定値以下の場合にはトランジスタ25のみによってゲート電圧を低下させることを特徴とする、スイッチング素子駆動装置。

(もっと読む)

電源装置、電源装置の制御装置および電子装置

【課題】零電流スイッチングを行うことによりスイッチングによる電力損失を抑制することが可能な電源装置、電源装置の制御装置および電子装置を提供すること。

【解決手段】

本発明は、オンすることにより中間ノードの中間電圧を確定させる第1スイッチング回路(12)と、中間電圧を共振させる共振回路(10)と、を有し、入力電圧を前記中間電圧を介し出力電圧に変換する電源装置の制御装置において、中間電圧が第1所定電圧以上となった場合、一定時間後に前記第1スイッチング回路をオンする第1タイミング回路(70)を具備することを特徴とする電源装置の制御装置並びにそれを有する電源装置および電子装置である。

(もっと読む)

負荷駆動制御装置

【課題】電流駆動素子の温度異常時にも負荷への通電を継続させた上で、電流駆動素子を確実に保護可能な負荷駆動制御装置を提供する。

【解決手段】電流駆動素子であるトランジスタの温度が過剰に高い温度異常状態かどうかかが判定され(S101)、温度異常状態でない場合には(S101:No)、トランジスタがPWM制御される。また、温度異常状態であり(S101:Yes)、且つ、トランジスタがPWM制御中の場合には(S102:Yes)、トランジスタがフルON固定状態に制御される(S103)。そして、温度異常状態であり、且つ、トランジスタがPWM制御中でない場合には(S102:No)、トランジスタを制御するための制御信号のデューティ比やスイッチング周波数を低い値に設定することにより、フルON固定状態にした場合よりもスイッチング損失が低くなるようにトランジスタが低損失制御される(S104)。

(もっと読む)

多機能ゲート付き高電圧ゲートドライバ集積回路

【課題】必要とする外部電力スイッチおよび外部コンポーネント数を節約できる、多機能ゲート付き高電圧ゲートドライバ集積回路を提供する。

【解決手段】第1出力電圧信号を供給可能な第1ドライバ回路と、第2出力電圧信号を供給可能な第2ドライバ回路と、第1出力電圧信号とは異なる特性を備える、処理済出力電圧信号を供給するべく、第2出力電圧信号を処理可能な内部回路と、第1出力電圧信号と処理済出力電圧信号のうちのいずれか1つを、ゲートドライブ信号として選択可能な選択回路とを備え、ゲートドライブ信号を外部電力スイッチのゲートに供給して外部電力スイッチをオンオフするべく、選択回路に接続される外部電力スイッチを更に備える高電圧ゲートドライバ集積回路を提供する。

(もっと読む)

電力変換装置及びその異常検出方法

【課題】複数のIGBT素子で構成される電力変換装置において、ゲート駆動回路の異常及びIGBT素子の異常を確実に検出して保護を行う。

【解決手段】電力変換装置の制御回路100と、各IGBTに対する指令パルスを発生するパルス発生回路200と、入力された指令パルスに応じてIGBTのオン・オフ動作制御を行う複数のゲート駆動回路400a〜400nと、各ゲート駆動回路に接続するIGBT500a〜500nと、異常検出回路300から構成し、異常検出回路にて、指令パルスRPa〜RPnとゲート駆動回路から出力されるゲートフィードバック信号FBPa〜FBPnとの不一致を判定し、不一致状態が一定時間継続した場合に異常と判定し、パルス発生回路に全指令パルスをオフさせる信号SUPを出力する。

(もっと読む)

半導体集積回路

【課題】製造工程上のばらつきを高精度で補正することができ、かつ、回路の大規模化を抑えることができる半導体集積回路を提供する。

【解決手段】この半導体集積回路は、第1の電位と第2の電位との間に直列に接続され、第1の電位と第2の電位との間の電圧を分圧することにより複数の電圧を生成する複数の抵抗と、複数の抵抗の内の少なくとも1つに並列に接続された少なくとも1つのスイッチ回路と、複数の抵抗の内の少なくとも他の1つに並列に接続された少なくとも1つのヒューズと、外部から供給される制御信号に従って、少なくとも1つのスイッチ回路をオン/オフさせるように制御する制御回路とを具備する。

(もっと読む)

半導体集積回路装置

【課題】ノイズ感度が小さく、サンプリング/ホールド誤差のサンプリング依存期間を小さく抑え、高精度で安定したサンプリング/ホールドを実現する。

【解決手段】サンプル/ホールド回路9は、トランジスタ12の両補の接続部には、抵抗10,11がそれぞれ接続されており、抵抗11の他方の接続部と基準電位VSSとの間には静電容量素子13が接続された構成となっている。このように、トランジスタ12の両方の接続部に、抵抗10,11がそれぞれ接続されていることにより、該トランジスタ12がONした際の電荷の抜き差しにおいて、入力信号Vin側、静電容量素子13側ともに、(Cg(:トランジスタ12の対バックゲート容量)/2×R)の時定数を有することになり、ホールドオフセット電圧ΔVhoff=qg/2Cshとすることができる。

(もっと読む)

駆動回路

【課題】スイッチング素子として電圧制御型トランジスタを備えた駆動回路において、回路規模の大型化や制御装置の処理負荷の増加を招くことなく、スイッチング素子の発熱を抑制しつつスイッチングノイズを低減できるようにする。

【解決手段】エンジンECUのMPU2から出力されるチャージ駆動信号によりチャージSW26がオン/オフされて、コンデンサ28にインジェクタ4開弁用の高電圧を蓄積するインジェクタ駆動回路において、チャージSW26を構成しているMOSFETのゲート抵抗として、NTC型のサーミスタ30を用いる。この結果、チャージSW26の低温時には、ゲート抵抗が大きくなってスイッチングノイズが抑制され、チャージSW26の温度が上昇すると、ゲート抵抗が低下して、チャージSW26の発熱が抑制される。

(もっと読む)

一次電池駆動型昇圧チョッパ回路及びその駆動方法

【課題】電池容量の使用効率を向上できかつ電池交換手間を減らせる一次電池駆動型昇圧チョッパ回路を提供すること。

【解決手段】昇圧チョッパ回路部31のトランジスタQ2を駆動する発振回路部32は、トランジスタQ1とそのコレクタ抵抗R1とからなる駆動段33を有する。トランジスタQ1のベースは、コンデンサC2により負荷駆動端Toに、CR回路30により接地端(Te)に接続されている。また、接地端(Te)はコンデンサC1により電源入力端(Ti)に接続されている。これにより、一次電池1の電圧が低くても、トランジスタQ1、Q2が安定にオンすることができる。

(もっと読む)

電力用スイッチング素子の駆動装置

【課題】 電力用スイッチング素子のゲート駆動能力を適切なタイミングで適切に調整し、サージ電圧の抑制とスイッチング損失の低減を安定的に両立させる駆動装置を提供する。

【解決手段】 IGBT(電力用スイッチング素子)のゲート電流を検出するゲート電流検出回路50(ゲート電流検出手段)と、検出したゲート電流の変化パターンに基づいて、IGBTのゲートを駆動する能力を調整する制御手段10(調整手段)を備えている。ゲート電流はIGBTのスイッチングノイズの影響を受け難い場所で検出することができる。IGBTのゲート駆動能力を、適切なタイミングで適切に調整することができる。

(もっと読む)

201 - 220 / 391

[ Back to top ]