国際特許分類[H03K3/02]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電気的パルスの発生回路;単安定回路,双安定回路,多安定回路 (1,702) | パルスの発生に用いられる回路形式または手段によって特徴づけられた発生器 (1,478)

国際特許分類[H03K3/02]の下位に属する分類

能動素子として二種類以上の素子または手段の使用によるもの,例.BIMOS,IGBTのような複合装置

内部または外部正帰還をもつ,差動増幅器または比較器を用いるもの (124)

内部または外部正帰還をもつ,論理回路を用いるもの (450)

能動素子として正帰還をもつ真空管だけを用いるもの

能動素子として内部または外部正帰還をもつバイポーラトランジスタを用いるもの (51)

能動素子として2個の電極,1個または2個の電位跳躍障壁をもち,負性抵抗特性を示す半導体装置を用いるもの (2)

能動素子としてホール蓄積またはエンハンスメント効果を示す半導体装置のを用いるもの (1)

能動素子として3以上の電極をもちかつアバランシェ効果を示す半導体装置を用いるもの

能動素子として3以上のPN接合,または4以上の電極,または同一伝導領域に接続された2以上の電極をもつバイポーラ半導体装置を用いるもの (2)

能動素子として内部または外部正帰還をもつ電界効果トランジスタを用いるもの (670)

能動素子としてバルク負性抵抗装置,例.ガン効果装置,を用いるもの

能動素子として他に分類されない半導体を用いるもの (2)

能動素子としてガス入り管を用いるもの,例.非安定トリガ回路

能動素子として超電導装置を用いるもの (3)

能動素子として電気化学的電池を用いるもの

能動素子として光−電子装置,すなわち電気的にまたは光学的に結合された発光および光電変換を用いるもの (3)

能動素子として電子ビーム偏向管を用いるもの

能動素子として非線形磁気装置または非線形誘電体装置を用いるもの (14)

外部信号により制御されるスイッチング素子によって負荷を通して放電させられ,かつ正帰還が組みこまれていないエネルギ蓄積素子の使用によるもの (33)

電流磁気効果装置の使用によるもの,例.ホール効果装置 (3)

国際特許分類[H03K3/02]に分類される特許

31 - 40 / 120

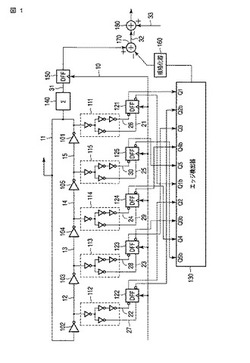

デジタル制御発振器

【課題】TDCに関する冗長構成を削減可能なDCOを提供する。

【解決手段】DCOは、デジタル制御信号によって遅延量が制御される3以上の奇数個の単相インバータ101〜105を環状に接続したリングオシレータと、単相インバータの各々の出力信号をバッファリングし、第1の差動信号として夫々出力する奇数個のバッファ111〜115と、基準信号の立ち上がりエッジまたは立ち下がりエッジにおける第1の差動信号の値を保持して第2の差動信号として夫々出力する奇数個のフリップフロップ121〜125と、奇数個のフリップフロップから出力される奇数組の第2の差動信号を入力し、奇数組の第2の差動信号を位相の進み順に配列したときの、連続する高レベル値または連続する低レベル値の末尾を示す情報を出力するエッジ検出器130とを具備する。

(もっと読む)

基準パルス生成装置

【構成】基準パルスは、HDMIトランスミッタ36のクロック生成動作のために参照される。CPU28は、HDMIトランスミッタ36のクロック作成動作をリセットし、基準パルスのレベルをOS用タイマTM1のオーバフローに応答してLレベルに変更するとともに、フリーランタイマTM2の値を“CAL_START_TIME”として検出するとともに、HDMIトランスミッタ36のクロック作成動作をリセットする。CPU28はさらに、その後のOS用タイマTM1のオーバフローに応答して基準パルスのレベルをHレベルに変更し、これに関連してフリーランタイマTM2の値を“CAL_STOP_TIME”として検出する。“CAL_STOP_TIME”と“CAL_START_TIME”との差分を表す“ΔTM”が既定範囲から外れると、CPU28は、上述の処理を再起動する。

【効果】クロック周波数の精度を確保することができる。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

高周波信号出力装置、該高周波信号出力装置に用いられる信号出力方法及び信号出力制御プログラム

【課題】出力タイミングの1ヒット目から安定した規定値の高周波信号を出力する高周波信号発生装置を提供する。

【解決手段】高周波信号発生部11で高周波信号shが発生し、同高周波信号shでは、制御部13により設定された周波数、パルス幅及び出力レベルを有するバースト状のパルスが発生するバースト期間と同パルスが発生しない非バースト期間とが、パルス発生部12により設定されたパルス繰返し周波数で交互に繰り返される。制御部13により、高周波信号発生部11に動作開始制御信号caが与えられると共に、高周波出力制御部14により、所定時間が経過するまで高周波信号発生部11の出力側が終端される一方、同所定時間が経過した後、高周波信号発生部11から出力されている高周波信号shのパルスが1ヒット目から外部へ送出される。

(もっと読む)

スピン素子を使用した弛緩発振器

【課題】スピン素子を使用した弛緩発振器を提供する。

【解決手段】弛緩発振器は、電源を印加する電源部と、該電源部から印加される電源によって駆動されるスピン素子と、該スピン素子に並列に連結されるキャパシタとを含む。スピン素子は、磁場の強さによって可変な可変電圧値を有する。キャパシタは、前記スピン素子が臨界電圧範囲の最小電圧値を有すると放電し、スピン素子が前記臨界電圧範囲の最大電圧値を有すると充電する。従って弛緩発振器は、製作に必要な部品の個数が少なくて回路が単純化され、製造費用と消費電力が少ない。よって弛緩発振器は、広範囲な周波数帯域の調節が可能で活動範囲が広く、磁化反転を使用することによって高出力が可能であるという効果がある。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

パルス発生回路

【課題】電源オフした直後に電源を再投入しても正常にパルス生成動作を再開できるようにすること。

【解決手段】このパルス発生回路は、第1のDフリップフロップ回路11のセット端子及びリセット端子をそれぞれコンデンサC11,C12を介してグラウンド又は電源に接続し、第1のDフリップフロップ回路11のQ出力端子とセット端子間及びQバー出力端子とリセット端子間にそれぞれ第1の抵抗R11,R12を接続し、前記セット端子、リセット端子、Q出力端子又はQバー出力端子のうちのいずれかの端子とグラウンド間に第2の抵抗RGを接続している。また、第1のDフリップフロップ回路11のQ出力端子を第2のDフリップフロップ回路20のクロック端子に接続し、第2のDフリップフロップ回路20のデータ端子及びセット端子を電源に接続し、第2のDフリップフロップ回路20のQバー出力端子とリセット端子間に第3の抵抗R2を接続した。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

発振回路

【課題】チップ面積を増大させることなく、低消費電流で安定した動作周波数を実現する。

【解決手段】発振回路は、電圧発生回路、ランプ電圧発生回路、及びアンプ回路を有する第1及び第2の遅延回路と、第1及び第2の遅延回路からの遅延信号が入力されるフリップフロップ回路とを備える。電圧発生回路は、電源線に接続された第1の電流源と、この第1の電流源及び接地線間にカスケード接続された第1及び第2のEMOSトランジスタと、ドレインが電源線、ゲートが第1のEMOSトランジスタにそれぞれ接続されたDMOSトランジスタと、このDMOSトランジスタ及び接地線間にカスケード接続され、それぞれ第1及び第2のEMOSトランジスタにゲートが共通接続された第3及び第4のEMOSトランジスタとを含み、DMOSトランジスタのソースから出力電圧を出力することを特徴とする。

(もっと読む)

電圧−周波数変換回路およびそれを備えた血圧測定装置

【課題】簡易な方式により精度の高い電圧−周波数変換回路を提供する。

【解決手段】抵抗素子16は、入力端子とノードN0との間に設けられる。スイッチ素子15は、ノードN0と接地電圧GNDとの間に設けられ、ノードNCの電圧レベルに応じて導通する。抵抗素子13は、ノードN0とノードNAとの間に設けられる。抵抗素子12は、ノードNAとNOR回路11Aの入力ノードの一方側との間に設けられる。コンデンサ14は、ノードNAとノードNCとの間に接続される。NOR回路11Aの入力ノードは、抵抗素子12を介してノードNAと、接地電圧GNDと接続される。NOR回路11Bの入力ノードは、NOR回路11Aの出力ノードと、接地電圧GNDと接続される。NOR回路11Cの入力ノードは、ノードNCと、接地電圧GNDと接続される。

(もっと読む)

31 - 40 / 120

[ Back to top ]