Fターム[4M104DD86]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 気相との反応 (289)

Fターム[4M104DD86]に分類される特許

61 - 80 / 289

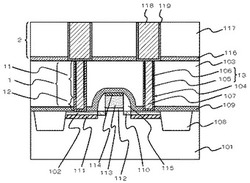

半導体装置及びその製造方法

【課題】ボイドやシームが発生しにくい構造体とする。

【解決手段】本発明の半導体装置は、半導体基板101に形成された層間絶縁膜103と、層間絶縁膜103に形成されたコンタクト孔104と、コンタクト孔104を埋め込むCu膜107と、コンタクト孔104の内部の側壁に形成され、Cu膜107の下地となる金属含有下地膜13と、を備える。コンタクト孔104の開口に接続している側壁の一部を含む第一の領域11において、金属含有下地膜13は、Cu膜107との界面に金属窒化層106を有する。第一の領域11よりも半導体基板101側の側壁を含む第二の領域12において、金属含有下地膜13は、Cu膜107との界面に金属層105を有する。金属層105の表面におけるCu膜107の成膜速度は、金属窒化層106の表面におけるCu膜107の成膜速度よりも大きい。

(もっと読む)

表示装置及びその製造方法

【課題】ソース・ドレイン電極に、剥離やストレスマイグレーションによるボイドが発生するのを抑制する。

【解決手段】複数の薄膜トランジスタが配列された基板を有する表示装置であって、薄膜トランジスタは、半導体層6と、半導体層6上に形成されるコンタクト層7と、コンタクト層7上に形成されるソース電極10及びドレイン電極9とを有し、ソース電極10およびドレイン電極9は、コンタクト層7の上側に形成される第1の導電層9a,10aと、第1の導電層9a,10aの上側に形成される第2の導電層9b,10bとを有し、第2導電層9b,10bは、第1添加元素と、銅とを含有する銅合金層であり、前記第1添加元素は、ジルコニウム、チタン、銀、インジウム、金、錫、クロム、ケイ素から選ばれた少なくとも1種類の元素である、ことを特徴とする表示装置。

(もっと読む)

トランジスタ基板及びその製造方法

【課題】オフ領域におけるゲート電圧−ドレイン電流特性(Vg−Id特性)の劣化を抑制した薄膜トランジスタを備えたトランジスタ基板及びその製造方法を提供する。

【解決手段】薄膜トランジスタTFTに設けられるチャネル保護層15の下層に形成された半導体層14のうち、ソース、ドレイン電極17間に側壁部が露出する領域(及びその近傍領域)が、酸素プラズマ処理により酸化処理されている。これにより、当該領域に酸化膜20が形成され、非導体化又は高抵抗化する。

(もっと読む)

光電変換装置用基板、およびそれを用いた光電変換装置、ならびにそれらの製造方法

【課題】微小凹部を形成することにより、光電変換装置の光電変換効率および安定性を向上させる。

【解決手段】ガラス基板2と、ガラス基板2の主表面の少なくとも一部を覆い、基板側とは反対側の表面に凹凸形状を有する透明導電膜3とを備えている。凹凸形状は、最大高さが50nm以上1200nm以下である凸部を有している。凸部の表面上に、局部山頂の間隔が2nm以上25nm以下である微小凹部が形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体装置のソース電極、ドレイン電極及びゲート電極を形成するいずれの領域においても、残渣のない良好な半導体/金属界面が得られるようにする。

【解決手段】化合物半導体装置の製造方法を、基板1上に化合物半導体積層構造4を形成する工程と、化合物半導体積層構造上に金属膜5A〜5Cを形成する工程と、金属膜上にソース電極7及びドレイン電極8を形成する工程と、金属膜の一部を酸化又は窒化して、金属酸化物膜又は金属窒化物膜5CXを形成する工程と、金属酸化物膜又は金属窒化物膜上にゲート電極9を形成する工程とを含むものとする。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

薄膜トランジスタおよびその製造方法、並びに表示装置

【課題】チャネルへの不純物添加を行うことなく閾値電圧を大きくすることが可能な薄膜トランジスタおよびその製造方法、並びに表示装置を提供する。

【解決手段】基板11にゲート電極20を形成したのち、このゲート電極20の表面から厚み方向における一部を、熱処理またはプラズマ処理を用いて酸化させることにより、ゲート電極20のゲート絶縁膜30との界面20Aから厚み方向における一部を、金属酸化物よりなる界面層21とする。ゲート電極20のゲート絶縁膜30との界面20Aにおける仕事関数が大きくなるので、ゲート電極20と酸化物半導体膜40との仕事関数差φMSが大きくなり、閾値電圧Vthが大きくなる。

(もっと読む)

有機銀錯体化合物、これの製造方法及びこれを用いた薄膜形成方法

【課題】銀化合物とアンモニウムカルバメート系化合物とを反応して誘導される新規な有機銀錯体化合物及び該化合物の製造方法の提供。

【解決手段】下式で表される銀化合物と、アンモニウムカルバメート系化合物(例えば;2−エチルヘキシルアンモニウム2−エチルヘキシルカルバメート、2−メトキシエチルアンモニウム2−メトキシエチルカルバメート、2−シアノエチルアンモニウム2−シアノエチルカルバメートなど)とを反応させて銀錯体化合物を製造する。

(式で、nは1〜4の整数であり、Xは酸素、硫黄、ハロゲン、シアノ、シアネート、カーボネート、ニトレート、ニトライト、サルフェート、ホスフェート、チオシアネート、クロレート、パークロレート、テトラフルオロボレート、アセチルアセトネート、及びカルボキシレートで構成された群から選択される置換基である)

(もっと読む)

半導体装置

【課題】ボンディングメタル層の材料によるショットキ界面の劣化を抑制または防止して、デバイス特性を改善する。

【解決手段】ショットキダイオードは、半導体基板10と、この半導体基板10にショットキ接触するショットキ金属層15と、ショットキ金属層15上に形成されたボンディングメタル層16とを含む。ショットキ金属層15は、金属窒化物層32bを含む金属窒化物含有多結晶金属層32からなるバリア層と、これに積層された金属層31とを有している。

(もっと読む)

密着性を改良するための基板のプラズマアニーリング

【課題】許容可能な拡散バリア特性と基板への密着性を耐熱性金属窒化物が有するように、基板上への窒化チタンなどの耐熱性金属窒化物膜の形成を提供する。

【解決手段】材料の層が、ウェハ上に部分的に形成された集積回路内の基板上に形成される。基板はプラズマアニールを受け、その間に基板はイオンでボンバードされる(工程300)。プラズマアニールは、エネルギーを注入された窒素含有ガスから生成されたプラズマへ基板を曝すことにより実行できる。基板がプラズマアニールされた後、耐熱性金属窒化物の層が基板上に堆積される(工程301)。耐熱性金属窒化物の層は、次に、第1セットのイオンでボンバードされる。第1セットのイオンによる耐熱性金属のこのボンバードは、プラズマアニールを実行することにより達成できる。耐熱性金属窒化物は、更に、第2セットのイオンによりボンバードされる(工程302)。

(もっと読む)

半導体装置およびその製造方法

【課題】オン電圧の低電圧化と高速動作を両立させた半導体装置を提供する。

【解決手段】ゲート絶縁膜3は、ソース領域5の端縁部からウエル領域4の外縁にかけての部分の上部に相当する領域が、厚さ約50nmの薄膜部3aとなっており、エピタキシャル層1の上部に相当する領域が、厚さ80〜100nmの厚膜部3bとなっている。薄膜部3aと厚膜部3bとの間は曲率を有して緩やかに変化し、この薄膜部3aから厚膜部3bへと変化する領域を膜厚変化領域15と呼称する。膜厚変化領域15は、エピタキシャル層1のウエル領域4の側面に接する部分および、当該部分近傍のウエル領域4の上部に相当する領域であり、そこでの、ゲート絶縁膜3の厚さは薄膜部3aよりも厚くなっている。

(もっと読む)

電界効果トランジスタの金属ゲート構造

【課題】電界効果トランジスタの電気抵抗の小さい金属ゲート構造を提供する。

【解決手段】本発明は、集積回路製造に関するものであって、特に、低抵抗の金属ゲート電極を有する電界効果トランジスタに関するものである。電界効果トランジスタのゲート電極の例は、凹部326aを有し、かつ、第一抵抗を有する第一金属材料からなる下側部分326と、突起328aを有し、かつ、第二抵抗を有する第二金属材料からなる上側部分328とからなり、突起が凹部に延伸し、第二抵抗は第一抵抗より小さい材料で形成される。

(もっと読む)

半導体装置およびその作製方法

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】半導体材料を含む基板に設けられたチャネル形成領域と、不純物領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極および第1のドレイン電極と、を有する第1のトランジスタと、半導体材料を含む基板上の酸化物半導体層と、第2のソース電極および第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、を有し、第2のソース電極および第2のドレイン電極は、その側面が酸化された酸化領域を有し、第1のゲート電極、第1のソース電極、または第1のドレイン電極のいずれかは、第2のゲート電極、第2のソース電極、または第2のドレイン電極のいずれかと電気的に接続されている半導体装置である。

(もっと読む)

グラフェン構造体、グラフェン構造体の製造方法、及び電子デバイス

【課題】グラフェンを高精度でパターニングすることができ、これにより、グラフェンを用いた電子デバイス要素及び電子デバイスの精細加工が可能であり、製造コストを格段に低減することが可能なグラフェン構造体及びその製造方法等を提供する。

【解決手段】基板上にレジスト膜を精度よくパターニングし、そのレジスト膜の開口内に親水化膜を形成した後、GOが親水性を有することを利用して、親水化膜の部分にのみ、GOを選択的に化学的に結合させて固定化し、更にそのGOを還元して親水化膜の部分にのみグラフェンが選択的に固定化されたグラフェン構造体を得る。このように、グラフェン構造体は、基板上にグラフェンが設けられてなり、且つ、基板における親水処理の部位とグラフェン、及び/又は、基板における疎水処理の部位以外の部位とグラフェンとの間に、親水処理による結合が形成されたものである。

(もっと読む)

半導体装置およびその作製方法

【課題】良好な特性を備えた、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびドレイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、ソース電極およびドレイン電極は、その側面が酸化された酸化領域を有する半導体装置である。なお、ソース電極およびドレイン電極の酸化領域は、300MHz以上300GHz以下の高周波電力、および、酸素とアルゴンの混合ガスを用いたプラズマ処理により形成されたものであることが望ましい。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

成膜方法及びプラズマ処理装置

【課題】シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させることが可能な成膜方法である。

【解決手段】真空排気が可能になされた処理容器22内で被処理体Wの表面に対して薄膜を形成する成膜方法において、原料ガスを用いて処理容器内でプラズマCVD法により薄膜としてチタンを含む金属膜8を形成する金属膜形成工程と、処理容器内で金属膜に対してアニール処理を行うアニール工程とを有する。これにより、シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させる。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】オフ電流および漏れ電流が抑制された薄膜トランジスタ、および前記薄膜トランジスタを歩留り良く製造することのできる薄膜トランジスタの製造方法を提供する。

【解決手段】ゲート電極12上にゲート絶縁膜12を介して順次形成されるSi(i)膜13およびSi(n)膜14上に金属膜を形成し、フォトレジストパターン22をマスクとしてエッチングし、ソース電極15およびドレイン電極16を形成する。酸素を含むプラズマで処理して、フォトレジストパターン22の側面を後退させるとともに、ソース電極15およびドレイン電極16の側面および露出した上面にAl酸化皮膜17を形成する。残存するフォトレジストパターン22およびAl酸化皮膜17をマスクとして、チャネル部18のSi(n)膜14およびSi(i)膜13の表面の一部をエッチングする。

(もっと読む)

ショットキーバリアダイオード

【課題】耐圧を向上できるショットキーバリアダイオードを提供する。

【解決手段】ショットキーバリアダイオード10は、基板と、基板上に形成されたGaN層3と、GaN層3上に接して形成されたショットキー電極4とを備えている。ショットキー電極4は、卑金属で、かつ4×1019cm-3以上の酸素濃度を有する。ショットキーバリアダイオード10において好ましくは、GaN層3とショットキー電極4との界面の炭素のピーク濃度は、1×1019cm-3以上である。

(もっと読む)

配線の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

61 - 80 / 289

[ Back to top ]