Fターム[5F033RR21]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 有機材料 (4,730)

Fターム[5F033RR21]の下位に属するFターム

Fターム[5F033RR21]に分類される特許

61 - 80 / 1,987

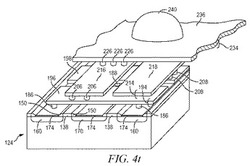

相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

(もっと読む)

半導体装置の製造方法

【課題】 厚い絶縁樹脂層のウェハレベルCSPで、第1電極(チップパッド)と外部電極(バンプ)との接続不良が発生しにくい半導体装置の製造方法を提供する。

【解決手段】 次の各工程を含む半導体装置の製造方法、(1)絶縁樹脂層を半導体ウェハの上に形成し、(2)開口径が(D1)となるよう絶縁樹脂層の一部を除去し半導体ウェハ上の第1電極を露出し、(3)フィルム状レジストを半導体ウェハの全面に、第1電極とレジストとの間が中空構造となるよう貼付け、(4)レジストをパターニングし、再配線層を絶縁樹脂層の上に形成し、レジストパターンを除去し、めっきした部分以外のシード層を除去し、(5)再配線層の上に再配線保護層を形成し、(6)再配線保護層の開口径(D2)が、D2>D1となるように再配線保護層の一部を除去して第1電極と、第2電極を露出し、(7)第1電極及び第2電極の上にめっき層を形成し、(8)めっき層を溶融して外部電極を形成する。

(もっと読む)

電極・配線用導電体

【課題】金属粒子の焼結体から構成された導電体を微細化された電極・配線とした場合でも腐蝕やマイグレーションの発生を長期間防止可能な電極・配線用導電体を提供する。

【解決手段】金属粒子の焼結体から構成された導電体薄膜上に、下記一般式(1)で表されるチオール化合物または下記一般式(2)で表されるスルフィド化合物から選択される少なくともいずれか一種の化合物を含有する金属イオン移動防止膜を設け、且つ、前記金属イオン移動防止膜中に凝集体構造が含まれてなる電極・配線用導電体とする。

Ar−SH…(1)[式(1)中、Arはベンゼン環を示し、置換基を有していてもよい。]

(A−R’−O−R−S)2…(2)[式(2)中、R’、Rはアルキレン基を示し、Aはフルオロアルキル基を示す。]

(もっと読む)

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

機能膜形成方法、配線基板の製造方法および配線基板

【課題】液体に対し金属膜の表面の濡れ性を改質し、金属表面と液体との接触角を増加させて液体の濡れ広がりを抑制し、信頼性の高い機能膜を低コストで実現すること。

【解決手段】基材1の平板面1aに金属膜2を形成する(金属膜形成工程)。次いで、金属膜2の表面2aに機能材料を含有する液体3を付与し、液体3を固化させて機能膜3Aを形成する(機能膜形成工程)。金属膜形成工程では、平板面1aに対する成膜入射角αが5°以上15°以下となる条件で平板面1aに金属を真空蒸着し、金属膜2を平板面1aに対して20°以上45°以下に傾斜する柱状結晶構造に形成する。

(もっと読む)

電子部材の製造方法

【課題】従来の方法では凹版印刷および平板印刷に向かなかったインクであっても、凹版印刷および平板印刷で印刷することの可能な電子部材の製造方法を提供する。

【解決手段】下記の関係式(1)、(2)を満たす電子材料層および粘着材料層を積層してなる積層インクが、凹版を用いて基材の表面に直接転写される。これにより、電子材料層が凹版印刷に向かない性質を有している場合であっても、粘着材料層の性質を活かして、電子材料層を含む積層インクを基材上に滲みなく印刷することができる。

E2<E3<E1またはE1<E3<E2…(1)

|E1−E2|>|E3−E2|…(2)

E1:版面の表面自由エネルギー

E2:電子材料層の表面自由エネルギー

E3:粘着材料層の表面自由エネルギー

(もっと読む)

パターン形成装置およびパターン形成方法

【課題】基板表面に塗布液を塗布して硬化させることにより基板表面に所定のパターンを形成するパターン形成技術において、パターンのさらなる微細化・高アスペクト化を可能とする技術を提供する。

【解決手段】吐出ノズル523から基板Wに吐出される隔壁形成用塗布液の側面部に対して集中的に、ライトガイド533の下端に設けたレンズ534で収束された光を照射する。塗布液の側面部が他の部分に先んじて硬化することで、表面張力によって表面が丸くなったり塗布液が広がるのを抑制することができるため、薄く均一で側面部が急峻に立ち上がる隔壁Bを形成することができる。

(もっと読む)

半導体装置およびその製造方法、表示装置ならびに電子機器

【課題】信頼性を向上させることが可能な半導体装置等を提供する。

【解決手段】半導体装置は、下層側の第1導電体部および上層側の第2導電体部と、第1の導電体部と第2の導電体部との間に設けられた、厚膜状の絶縁体層と、この絶縁体層に対する貫通孔の内面形状に倣うように形成され、第1導電体部と第2導電体部とを電気的に接続するコンタクト部とを備え、貫通孔のテーパ角が鋭角となっている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

パターン転写方法

【課題】エッチングを行わずに残膜除去処理を行うことが可能なパターン転写方法を提供する。

【解決手段】実施形態のパターン転写方法では、被加工基板上に光反応性樹脂を形成する。さらに、前記方法では、凹凸パターンを有する透明基板と、前記凹凸パターンの表面の一部に形成された遮光膜と、を備えるモールドを前記光反応性樹脂に押印する。さらに、前記方法では、前記モールドが前記光反応性樹脂に押印された状態で、前記モールドを介して前記光反応性樹脂に光を照射する。さらに、前記方法では、前記光反応性樹脂に光を照射した後に、前記モールドが前記光反応性樹脂に押印された状態で、前記光反応性樹脂を加熱する。さらに、前記方法では、前記光反応性樹脂の加熱後に、前記モールドを前記光反応性樹脂から離型する。さらに、前記方法では、前記モールドの離型後に、前記光反応性樹脂を洗浄液で洗浄する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】基板を実装する際の温度負荷によって絶縁層と下地金属層の側面との接点領域に加わる応力を緩和させ、応力に起因した絶縁層のクラックの発生を抑えるように構成された半導体装置を提供する。

【解決手段】半導体基板101の一面101aに、絶縁層102、下地金属層103、金属端子が設けられるためのランド部104を順に積層してなる半導体装置109であって、ランド部104は、絶縁層102と対向する面の中央部において、下地金属層103と接合する接合領域と、絶縁層102と対向する面において、接合領域を除いた非接合領域と、を有し、下地金属層103は、ランド部104側から絶縁層102側にかけて外向きに傾斜した側面を有していること、を特徴とする半導体装置109。

(もっと読む)

膜の製造方法および表示装置の製造方法

【課題】微細な貫通孔を有する膜を形成することが可能な膜の製造方法、およびこの方法を用いた表示装置の製造方法を提供する。

【解決手段】ペースト充填用の凹部を有すると共に凹部内に凸部を有し、凸部の上面に撥液性領域を有する凹版を用い、凹部に充填されたペーストを基材に転写することにより、基材上に、貫通孔を有する膜を形成する膜の製造方法。基板に、TFT,絶縁膜および有機EL素子を順に形成する工程を含み、絶縁膜を形成する工程において、ペースト充填用の凹部を有すると共に凹部内に凸部を有し、凸部の上面に撥液性領域を有する凹版を用い、凹部に充填されたペーストを基材に転写することにより、基材上に、貫通孔を有する膜を形成する表示装置の製造方法。

(もっと読む)

半導体装置及びその製造方法並びに積層型半導体装置

【課題】貫通電極と直接に接続される配線の信頼性を向上できるようにする。

【解決手段】半導体装置100は、貫通孔1Aを有する半導体基板1と、半導体基板1の上に形成された第2層間絶縁膜7bと、第2層間絶縁膜7bに貫通孔1Aを覆うように形成された第1の外部接続用配線8a1と、第2層間絶縁膜7bの上に、第1の外部接続用配線8a1を覆うように形成された第3層間絶縁膜7cと、第3層間絶縁膜7cにおける第1の外部接続用配線8a1の上側部分に形成された第2の外部接続用配線8b1と、貫通孔1Aにおける少なくとも内壁面に形成されると共に、各外部接続用配線8a1、8b1とそれぞれ電気的に接続される貫通電極15Aとを備えている。第1の外部接続用配線8a1は、複数の孔部19aを有し、第2の外部接続用配線8b1は、第1の外部接続用配線8a1の孔部19aを覆うように形成されている。

(もっと読む)

導電性ビアの製造と充填のための方法、およびそのように形成された導電性ビア

【課題】ビアホール表面上の絶縁コーティングとビアホール内に挿入される導電材料との付着性を向上する。

【解決手段】導電性ビアを形成する方法は、一つ以上のビアホールを基板内に形成するステップを含む。ビアホールは、単一マスク、保護層、ボンドパッド、もしくは、エッチングプロセスの間にフォトマスクが除去される場合にハードマスクとして機能する、基板のその他のフィーチャで形成され得る。ビアホールは、その表面に低誘電率(低K)誘電材料を含む誘電体コーティングの付着を促進するように構成されてもよい。障壁層が各ビアホールの表面の上に形成されてもよい。種材料(seed material)を含み得るベース層は、その後のビアホールの表面上の導電材料の選択的堆積を促進するように形成されてもよい。

(もっと読む)

半導体装置およびその製造方法

【課題】ダイシング工程で発生する膜剥離やクラックがチップ内部に伝播するのを防ぐ。

【解決手段】半導体装置100は、基板102と、ビア層130および配線層132が形成される素子形成領域であるチップ内部202と、平面視においてチップ内部202を囲むようにチップ内部202の外周に形成されたシールリング部204と、を含む。シールリング部204において、シールリングは、平面視においてチップ内部202を囲むように形成された貫通孔122aを有する第1のメタル層122と、第1のメタル層122上に第1のメタル層122に接して形成された第2のメタル層124と、を含み、第1のメタル層122の貫通孔122aの下部分には絶縁性材料(層間絶縁膜106)が形成され、貫通孔122aの上部分には第2のメタル層124を構成するメタル材料がくい込んで形成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】電極パッドの表面の突出部に起因する不具合が発生し難い半導体装置の製造方法及び半導体装置を提供する。

【解決手段】半導体装置の製造方法は、表面の突出部に突出部、例えば、プロービング痕21が存在する電極パッド2を備える基板1上に、電極パッド2の少なくとも一部を覆う第1の絶縁膜4を形成する第1の絶縁膜形成工程と、第1の絶縁膜4の表面から突起した部分22を除去することができる処理を行う除去処理工程と、除去処理工程後に、第1の絶縁膜4上及び電極パッド2上に第2の絶縁膜5を形成する第2の絶縁膜形成工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 低k膜と金属マスクとの間の界面に歪みを引き起こすことなく、高い精度の望ましいパターンを得ること。

【解決手段】 半導体装置を製造する方法では、金属マスクと絶縁マスクをと備える多層ハードマスクを用いて形成される配線層を含む半導体装置が形成される。第1パターンにアラインされた第2開口パターンを形成するために、第1ステップで多層ハードマスクが使用された後、金属マスクが除去され、絶縁マスクが、第2のステップで絶縁層中に第1のパターン構造を形成するために使用される。

(もっと読む)

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

【課題】公知のプロセスよりも高速であり、充てんされたビアにボイド、凹み又はキーホールを残さず、製造の費用効果が高い、改善された方法を提供する。

【解決手段】第1の表面214及び対向する第2の表面216を有する基板212を設け、基板の第1の表面に部分的にのみ前記基板の中に広がる少なくとも1つのブラインドビア218を形成する。酸化材料によって前記少なくとも1つのブラインドビアの表面をパッシベーションし、少なくとも一つのブラインドビアの酸化材料の表面に銅を含むシード材料228を、シード材料を前記少なくとも一つのブラインドビアの内部に閉じ込め、かつ、基板の前記第1の表面を露出させるように形成する。シード材料の上に導電性材料230を前記少なくとも一つのブラインドビアを充填するように無電解めっきし、少なくとも一つのブラインドビアの導電性材料を露出させるために基板の前記第2の表面に研磨平坦化を実施する。

(もっと読む)

複数の開口部を備える基板上への層の蒸着方法

【課題】多孔性低誘電率絶縁膜のトレンチおよびビア内にカバレージ良くライニング層を形成する半導体装置の製造方法を提供する。

【解決手段】第1パルス期間に供給される第1反応物と、第2パルス期間に供給される第2反応物とを利用する原子層堆積(ALD)プロセスにより成膜する。まずシーリング層を低コンフォマリティーを有する条件で成膜し、ポアをブロックする。この後、接着層を高いコンフォマリティーを有する条件で成膜する。

(もっと読む)

誘電フィルム及び材料における疎水性を回復する方法

【課題】誘電率の増加、シラノールの増加、または有機部分の減少、の少なくとも一つによって損傷した、基体上のシリカ誘電フィルムの損傷を回復する。

【解決手段】基体上のそのような損傷シリカ誘電フィルムを表面改質組成物と接触させて、該損傷シリカ誘電フィルムの誘電率の減少、該損傷シリカ誘電フィルムの誘電率のシラノールの減少、該損傷シリカ誘電フィルムの誘電率の有機部分の増加、の1つ以上をもたらす。このとき、該損傷シリカ誘電フィルムに疎水性を与える。

(もっと読む)

61 - 80 / 1,987

[ Back to top ]