Fターム[5F033RR22]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 有機材料 (4,730) | ポリイミド系樹脂 (1,337)

Fターム[5F033RR22]に分類される特許

141 - 160 / 1,337

半導体装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを特徴としている。

(もっと読む)

半導体装置

【課題】アクティブマトリクス型の液晶表示装置に代表される電気光学装置ならびに半導体装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的としている。

【解決手段】基板上に逆スタガ型のTFT上に無機材料から成る第1の層間絶縁層と、第1の層間絶縁膜上に形成された有機材料から成る第2の層間絶縁層と、前記第2の層間絶縁層に接して形成された画素電極とを設け、前記基板の端部に他の基板の配線と電気的に接続する入力端子部とを有し、該入力端子部は、ゲート電極と同じ材料から成る第1の層と、画素電極と同じ材料から成る第2の層とから形成されていることを特徴としている。このような構成とすることで、フォトリソグラフィー技術で使用するフォトマスクの数を5枚とすることができる。

(もっと読む)

チップの製造方法

【課題】 相互接続ラインを形成するための新規な方法を提供する。

【解決手段】 細線相互接続部(60)は基体(10)の表面内又はその上に形成された半導体回路(42)の上に位置する第1の誘電体層(12)内に設けられる。パシベーション層(18)は誘電体層の上に付着され、第2の厚い誘電体層(20)はパシベーション層の表面上に形成される。厚くて幅広い相互接続ラインは第2の厚い誘電体層内に形成される。第1の誘電体層はまた、基体の表面上に付着されたパシベーション層の表面上に幅広くて厚い相互接続ネットワークを形成するように、省略することができる。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

三次元積層構造を持つ半導体装置の製造方法

【課題】 三次元積層構造を持つ半導体装置において、積層された半導体回路層間の積層方向の電気的接続を、埋込配線を使用して容易に実現する半導体装置の製造方法を提供する。

【解決手段】 第1半導体回路層1aの半導体基板11の表面に、絶縁膜14で内壁面が覆われたトレンチ13を形成し、トレンチ13の内部に導電性材料を充填して導電性プラグ15を形成する。次に、トレンチ13とは重ならないように所望の半導体素子を基板11の表面または内部に形成し、その上に層間絶縁膜19を介して多層配線構造30を形成してから、多層配線構造30の表面にプラグ15に電気的に接続されたバンプ電極37を形成する。そして、電極37を用いて基板11を支持基板40に固定してから基板11をその裏面側から選択的に除去し、絶縁膜14を基板11の裏面側に露出させる。基板11の裏面側に露出せしめられた絶縁膜14を選択的に除去してプラグ15を露出させ、その端に電極42を形成する。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極のための開口部を形成する時に、上部配線層の配線とのミスアラインメント問題が発生しない半導体装置を製造する方法の提供。

【解決手段】第1面及び第1面の反対側に第2面を有する基板を準備する段階と、基板の第1面から基板の厚さ方向に延長して貫通電極が形成される領域に犠牲膜パターンを形成する段階と、基板の第1面上に形成され、犠牲膜パターン上に位置する配線を有する上部配線層を形成する段階と、基板の第2面を部分的に除去して犠牲膜パターンを露出させる段階と、犠牲膜パターンを基板の第2面から除去して配線を露出させる開口部を形成する段階と、開口部内に配線と電気的に接続される貫通電極を形成する段階と、を有する。

(もっと読む)

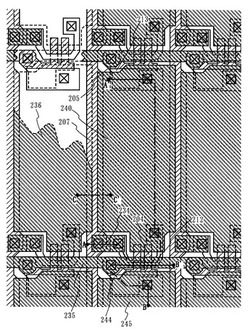

固定用構造および嵌合構造

【課題】チップの縁領域は、膨張係数が異なることによって、温度サイクル中に、TC応力とも称される特定の負荷を受けることが多い。これらの縁領域は特にTC応力を受け易いため、同領域内において様々な不良が生じる可能性がある。これによって、実際のデバイスにおける信頼性のリスクが増大する可能性がある。

【解決手段】半導体デバイスの金属構造210のための固定用構造200は、オーバーハング形状の側壁230を少なくとも1つ含んだ固定用凹部構造220を含んでいる。上記金属構造210は、少なくとも部分的に上記固定用凹部構造220内に配置されている。

(もっと読む)

半導体装置

【課題】工程数の増大を抑制しつつ、チップ上に形成された再配線または突出電極の信頼性を向上させる。

【解決手段】配線2bおよびパッド電極2aが形成された半導体基板と、半導体基板上に形成された応力緩和層4と、応力緩和層4上に合金シード膜5を形成した後、応力緩和層4と合金シード膜5とを熱処理にて反応させることで、応力緩和層4と合金シード膜5との間に反応性バリア絶縁膜6を形成する。再配線8または突出電極は合金シード膜5上に形成する。

(もっと読む)

半導体装置の製造方法

【課題】水素又はカルボン酸を用いたリフロー時の導電部と絶縁層の密着力低下を抑制する。

【解決手段】半導体基板の上に設けられた第1導電部上に絶縁層を形成し(ステップS1)、その絶縁層を被覆するようにバリア層を形成した後(ステップS2)、そのバリア層の上に第2導電部を形成する(ステップS3)。そして、第1導電部上の絶縁層がバリア層で被覆されている状態で、第2導電部を水素又はカルボン酸を含む雰囲気中で溶融し(ステップS4)、その後、その第2導電部をマスクにして、絶縁層の上からバリア層を除去する(ステップS5)。

(もっと読む)

半導体素子基板

【課題】低誘電率特性、低リーク電流特性、および高絶縁破壊電圧特性に優れ、しかも、透明性が高い樹脂膜を備える半導体素子基板を提供すること。

【解決手段】バインダー樹脂(A)、酸性基を有する化合物(B)、及び架橋剤(C)を含有してなる樹脂組成物からなる樹脂膜を有する半導体素子基板であって、

前記バインダー樹脂(A)は、重量平均分子量(Mw)が10,000以上、吸水率が0.03重量%以上であり、前記バインダー樹脂(A)の重量平均分子量(Mw)に対する、前記架橋剤(C)の分子量の比率が、0.05以下であり、前記バインダー樹脂(A)100重量部に対する、前記架橋剤(C)の含有量が21〜150重量部であり、前記樹脂膜は、前記半導体素子基板に実装されている半導体素子表面、または前記半導体素子に含まれる半導体層と接触して形成されていることを特徴とする半導体素子基板を提供する。

(もっと読む)

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体

装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上か

らフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有す

る。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及

び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透

過層表面に撥液処理を行ってもよい。

(もっと読む)

半導体装置、回路基板及び電子機器

【課題】信頼性の高い半導体装置及びその製造方法、回路基板並びに電子機器を提供することにある。

【解決手段】電極114は集積回路112に電気的に接続されている。半導体基板110の電極114が形成された面に、電極114を避けて樹脂層118が形成されている。配線122は、電極114に電気的に接続されており、樹脂層118の側面121と上面120の境目に形成された第1の部分150と、第1の部分150に接続されて樹脂層118の上面120に形成された第2の部分152と、を有する。第1の部分150は第2の部分152よりも広い幅で形成されている。外部端子124が配線122に電気的に接続されている。

(もっと読む)

半導体装置

【課題】並列駆動構成のI/Oバッファから出力される信号を安定化し、信頼性を向上する。

【解決手段】I/Oセル2は、1つの出力信号を正転信号と反転信号からなる相補信号として出力する相補型I/Oセルからなり、2つのI/Oセル2が並列接続された構成からなる。2つのI/Oセル2の出力部となるインバータ6の出力部は、配線17によってそれぞれ接続されており、2つのI/Oセル2の出力部となるインバータ7の出力部は、配線18によってそれぞれ接続されている。配線17は、I/Oセル2の下辺側に2つのI/Oセル2を横断するように形成され。配線18は、該配線17の上方に形成されており、2つのI/Oセル2を横断するように形成されている。また、配線17の配線長と配線18の配線長は、略同等となるようにレイアウトされている。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】保護膜(Al2O3)の膜質変化に起因するTFT特性のばらつきを軽減することが可能な薄膜トランジスタの製造方法を提供する。

【解決手段】TFT1の製造プロセスにおいて、ソース・ドレイン電極15上に、第1保護膜16(Al2O3層)とAl層とをこの順に、スパッタリングにより連続的に成膜する。各層のスパッタリングでは、いずれもターゲットとしてアルミニウムを用いるが、Al2O3層の成膜過程では、反応ガスとして使用する酸素ガスによってターゲット表面が変質し易い。その後、連続してAl層を成膜する(酸素ガスを使用しないスパッタリングを行う)ことで、ターゲット表面が改質される(成膜処理の度に、ターゲット表面が改質される)。従って、成膜処理回数が増しても、保護膜における膜厚や屈折率が変化しにくい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の検査特性を向上させる。

【解決手段】本発明の半導体装置の製造方法は、(a)基板の上方にアルミニウムを含有する導電性膜(アルミニウム膜10b)を形成する工程と、(b)上記導電性膜をパターニングすることにより配線を形成する工程と、(c)上記配線の上部に第1絶縁膜(第1保護膜)を形成する工程と、を有する。さらに、(d)上記第1絶縁膜をエッチングすることにより、上記配線のパッド領域(Pd)を露出する工程と(e)上記パッド領域(Pd)に、窒素系のプラズマガスを用いたプラズマ処理を行う工程と、(f)上記(e)工程の後、上記パッド領域(Pd)にプローブ針を当接し、上記パッド領域(Pd)に通電する工程と、を有する。上記(e)工程により、上記パッド領域(Pd)に窒化アルミニウム層(15)が形成され、パッド領域(Pd)とプローブ針(N)との接触抵抗を低減することができる。

(もっと読む)

半導体デバイス用基板洗浄液及び洗浄方法

【課題】基板表面を腐食することなく微粒子付着による汚染、有機物汚染及び金属汚染を同時に除去することができ、しかも水リンス性も良好で、短時間で基板表面を高清浄化することができる半導体デバイス用基板洗浄液を提供する。

【解決手段】

半導体デバイス製造における化学的機械的研磨工程の後に行われる、半導体デバイス用基板の洗浄工程に用いられる洗浄液であって、以下の成分(A)〜(D)を含有してなる半導体デバイス用基板洗浄液。

(A)有機酸

(B)スルホン酸型アニオン性界面活性剤

(C)ポリビニルピロリドン及びポリエチレンオキシド−ポリプロピレンオキシドブロック共重合体から選ばれる少なくとも1種の高分子凝集剤

(D)水

(もっと読む)

半導体装置及びその製造方法

【課題】回路を形成した半導体ウェハをダイシングするときに発生するクラックの伝搬を抑制する。

【解決手段】ウェハ1上のチップ領域2にMOSトランジスタT1及び配線31,48,54,64,64を形成すると共に、チップ領域2内でMOSトランジスタT1及び配線31,48,54,64,64を囲むガードリング76を形成する。また、ウェハ1上のスクライブライン領域3には、チップ領域2に第1層の配線31を形成するときに、第1の応力吸収パターン33を同時に形成する。さらに、最上層の配線74を形成するときに、第2の応力吸収パターン77を同時に形成する。各応力吸収パターン33,77は、チップ領域2を囲むように連続して形成され、スクライブライン領域3の中心線SCを跨ぐベタパターンである。ダイシング時には、第1及び第2の応力吸収パターン33,77の一部が残るようにウェハ1を切断する。

(もっと読む)

パターン形成体の製造方法、および有機薄膜トランジスタ

【課題】 本発明は、簡易な製造工程で高精細なパターン状に導電性パターン等を効率よく形成可能なパターン形成体の製造方法、およびその方法により形成されたパターン形成体を用いた配線基板の製造方法や有機薄膜トランジスタの製造方法等を提供することを主目的としている。

【解決手段】 上記目的を達成するために、本発明は、光触媒を含有する光触媒含有層および基体を有する光触媒含有層側基板の光触媒含有層と、撥水性を有する樹脂製基材とを対向させて配置し、パターン状にエネルギーを照射することにより、前記樹脂製基材上に水との接触角が低下した濡れ性変化パターンをパターン状に形成するエネルギー照射工程を有することを特徴とするパターン形成体の製造方法を提供する。

(もっと読む)

半導体装置

【課題】 製造が容易でかつ絶縁性に優れ、平坦な上面(表面)を持つパッシベーション構造を備えた配線構造を、低コストかつ短リードタイムで形成する、半導体装置を提供する。また、配線抵抗が小さくボンディング耐性が高い配線構造を提供する。

【解決手段】 所望の素子領域の形成された基板表面に形成された配線層と、前記配線層表面を覆う層間絶縁膜と、前記層間絶縁膜表面全体を覆うように形成された窒化シリコン膜と、前記窒化シリコン膜の上層に形成された最上層メタルとしての金層からなるメタル配線層と、前記窒化シリコン膜と前記メタル配線層との間に形成されたバリア層と、前記メタル配線層上に形成されたポリイミドからなる平坦化絶縁膜とを含み、前記バリア層と前記配線層は、前記窒化シリコン膜と前記層間絶縁膜に形成されたスルーホールを通じて接続されており、前記平坦化絶縁膜が一部領域で除去せしめられ、前記メタル配線層にボンディングがなされていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】薄型化及び小型化を図る半導体装置を提供する。

【解決手段】半導体装置1は、半導体チップ10と、半導体チップ10の上に積層された多層配線構造30と、多層配線構造30内に埋設された電子部品60,80と、を備える。半導体チップは、半導体基板11と、半導体基板上に形成された内部配線20と、内部配線を被覆するようにして半導体基板上に形成された封止層16と、を有し、多層配線構造が封止層上に形成されている。

(もっと読む)

141 - 160 / 1,337

[ Back to top ]