Fターム[5F044AA02]の内容

ボンディング (23,044) | ワイヤによるペレット電極との接続構造 (951) | 配線基板との接続 (306)

Fターム[5F044AA02]の下位に属するFターム

基板配線にメッキしているもの (25)

基板配線にボンディングチップがあるもの (12)

基板配線の配置、形状に関するもの (52)

Fターム[5F044AA02]に分類される特許

41 - 60 / 217

オフセットダイスタッキングを用いたマルチチップパッケージおよびその作成方法

半導体装置の製造方法

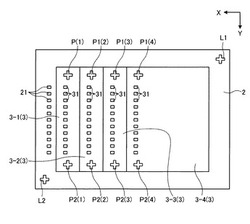

【課題】認識パターンの位置の誤検出を抑制することで、製造効率の低下を抑えることのできる半導体装置の製造方法を提供すること。

【解決手段】位置検出を行うための認識パターンP1,P2が形成された複数の半導体メモリチップ3を、回路パターンが形成された回路基板2上に、認識パターンが露出するように階段状に積層し、認識パターンの位置として予め登録された登録位置情報に基づいて認識パターンの位置を検出し、認識パターンの検出位置に基づいて回路基板と半導体メモリチップとにワイヤボンディングを行い、認識パターンの位置の検出は、1の認識パターンを検出して次の認識パターンを検出する場合に、1の認識パターンの検出位置情報と、次の認識パターンの登録位置情報との差分から検出基準位置を設定し、設定された検出基準位置に基づいて次の認識パターンを検出することにより行われる。

(もっと読む)

電子装置、中継部材、実装基板、及び電子装置の製造方法

【課題】ワイヤの接続構造の信頼性を確保し、かつワイヤ接続用の構造体に汎用性を持たせる。

【解決手段】中継部材100は、少なくとも一部が平面視で半導体チップ20とリード14の間に位置しており、表面に複数の金属が互いに絶縁した状態で設けられている。第1ワイヤ40及び第2ワイヤ30の少なくとも一方は、他端34,44が中継部材100の表面に位置する金属の少なくとも一つに接合している。また第1ワイヤ40の他端44と第2ワイヤ30の他端34は、中継部材100のうち半導体チップ20とリード14の間に位置する部分で、互いに接合している。

(もっと読む)

半導体素子の実装構造

【課題】半導体素子とパッケージとの線膨張係数差に起因して半導体素子の機能部に生じる応力を低減でき、且つ、アウトガスの発生を防止できる半導体素子の実装構造を提供する。

【解決手段】シリコン基板の主表面側に機能部12を形成した半導体素子1が、シリコン基板の裏面側をパッケージ2の実装面22側として配置され、シリコン基板の裏面に直接接合されたAuバンプ3を介してパッケージ2の実装面22に接合され、シリコン基板の主表面側のパッド14がボンディングワイヤ4を介してパッケージ2の導体パターン23と電気的に接続されている。

(もっと読む)

半導体装置

【課題】固体撮像素子13の特性が安定している撮像装置1を提供する。

【解決手段】第1の主面11に形成された固体撮像素子13と第2の主面12に形成された固体撮像素子13の外部端子17とを有するデバイスチップ10と、接続パッド36を有する先端部31と、90度以上の角度に折り曲げられた屈曲部32と、延設部33と、からなり、先端部31から屈曲部32を介して延設部33まで延設された配線層35を有する配線板30と、第2の主面12に先端部31を接着する接着層16と、外部端子17と接続パッド36とを電気的に接続するワイヤボンディング配線40と、を具備し、配線板30がデバイスチップ10の第2の主面の直上空間10S内にある。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】電源端子及びグランド端子をより少なくして、信号端子をより多く備えることができる半導体装置を提供する。

【解決手段】複数の第1電極パッド11を第1面に有する半導体チップ10と、第1面上で、複数の第1電極パッド11の各々と接触し、複数の第1電極パッド11の各々を電気的に接続する第1配線テープ20とを具備する。

(もっと読む)

配線構造

【課題】電源・信号間の干渉および結合の抑制と、電源ノイズの抑制と、信号間の干渉・クロストークの抑制と、インピーダンス不連続による信号反射の抑制とを、全てバランスよく満たす低コストな高速デバイスを提供する。

【解決手段】信号用ボンディングワイヤ31d、31eと、グランド用ボンディングワイヤ31b、31gと、電源用ボンディングワイヤ32a、32c、32f]とを、次のように配置する。すなわち、グランド用ボンディングワイヤまたは電源用ボンディングワイヤの一方が、信号用ボンディングワイヤと同じ第1の包絡面に含まれ、他方は別の第2の包絡面に含まれる。ここで、第2の包絡面に含まれるボンディングワイヤおよび信号用ボンディングワイヤの間の電磁結合が、第1の包絡面に含まれる2本のボンディングワイヤの間の電磁結合よりも小さくなるようにする配線構造。

(もっと読む)

低インダクタンス化された結合素子が接合されたマイクロ電子アセンブリ

マイクロ電子アセンブリ100は、第1の面において露出するチップコンタクト112を有する半導体チップ110、1110と、チップ110、1110の面128、129と並置される基板130、1130とを含む。導電性結合素子144が第1のチップコンタクト112を基板の第1の基板コンタクト132、1132と電気的に接続することができ、第2の導電性結合素子146が第1のチップコンタクト112、132を第2の基板コンタクトと電気的に接続することができる。第1の結合素子144は第1のチップコンタクト112、212Aに冶金学的に接合される第1の端部244A、344Aと、第1の基板コンタクトに冶金学的に接合される第2の端部244B、344Bとを有することができる。第2の結合素子の第1の端部246A、346Aは第1の結合素子212Aに冶金学的に接合することができる。第2の結合素子は、第1のチップコンタクト112、212A、1212又は基板コンタクト132、1132と接触する場合も、接触しない場合もある。第3の結合素子948を、基板コンタクト又はチップコンタクトに接合される第1の結合素子及び第2の結合素子の端部に接合することができる。一実施形態では、結合素子740は、第1のコンタクト732Aにおいて接合される第1の端部742及び第2の端部746と、第2のコンタクト712Aに接合される中央部744とを有する、ループ状接続を有することができる。 (もっと読む)

半導体装置の製造方法

【課題】平置きタイプの半導体装置において、ワイヤボンディング不良の発生を抑制する。

【解決手段】複数の半導体チップ12を、配線基板40が有する複数のチップ搭載領域20a上にそれぞれ液状の接着材ペースト11aを介して搭載する半導体装置の製造方法であって、配線基板40を以下のようにする。すなわち、各デバイス領域40a内で、並べて配置される複数のチップ搭載領域20aの間には、端子(ボンディングリード)22を配置せず、配線基板40を覆う絶縁膜26に形成された溝部(ダム部)26bを配置する。

(もっと読む)

ワイヤボンディング方法および半導体装置

【課題】低エネルギーで適切にワイヤを被接合用パッドに接合できるワイヤボンディング方法を提供する。

【解決手段】ボール形成工程の後、ツール100の先端部から引き出されているボール形状の引き出し部40aを、表面が粗化された粗化部材200に押し付けて、引き出し部40aが粗化部材200に押し付けられた部位から潰れるように塑性変形させることにより、引き出し部40aの表面のうち粗化部材200に押し付けられた部位を粗化する粗化工程を行い、その後、引き出し部40aの表面のうち粗化された部位を、被接合用パッド21に押し当ててボンディング工程を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】ワイヤの経路が所望の経路から外れてしまうことにより、隣り合うワイヤどうしが接触することを抑制する。

【解決手段】半導体装置は、電極上に形成されたバンプ10と、バンプ10に一端が接続されたワイヤ1と、を有している。バンプ10は、本体部11と、本体部11上に形成された複数の突起部12と、を有している。ワイヤ1と、複数の突起部12どうしの間に形成される谷間13とが、平面視において重なっている。複数の突起部12どうしの間に形成される谷間からのワイヤ1の脱落を抑制することができる。よって、ワイヤ1の経路が所望の経路から外れてしまうことにより隣り合うワイヤ1どうしが接触してしまうことを抑制することができる。

(もっと読む)

半導体装置及びそのワイヤーボンディング方法

【課題】キャピラリーとワイヤーとの干渉・接触を避けながらボンディングパッドとフィンガーが接合される半導体素子及びそのワイヤーボンディング方法を提供すること。

【解決手段】半導体素子10は、ボンディングパッド12を備えた矩形の半導体チップ14とフィンガー16を備えた矩形のリードフレームよりなる。ワイヤー20により、それぞれのボンディングパッド12とそれぞれのフィンガー16は接合される。ワイヤーは、比較的短い第1のワイヤー群20と、比較的長い第2のワイヤー群(図示せず)に振り分けられる。第1のワイヤー群20のボンディングパッド側接合点は、半導体チップ14の外縁に近い位置に、第2のワイヤー群のボンディングパッド側接合点は、半導体チップ14の外縁から離れた位置にずれている。これにより、先行形成されたワイヤーとキャピラリーの干渉を避けることができる。

(もっと読む)

電子装置

【課題】半導体装置のフィルタ回路に高調波成分の周波数帯域に対応する共振回路部を設けて、所望周波数成分以外の高調波成分を、半導体装置を実装する実装基板を介して、GNDに落とす。このとき、高調波成分は、実装基板の寄生インダクタンス成分と、別の共振回路部とを介して、フィルタ回路に戻ってしまう。その結果、高調波成分において、設計値からリジェクション量が減少してしまう。

【解決手段】実装基板の寄生インダクタンスのうち、半導体装置の共振回路部のGNDと別の共振回路部のGNDとの間の寄生インダクタンス成分を大きく設けることによって、高調波成分のリジェクション量の低下を抑制し、寄生インダクタンスを含まない理想的な場合と同等のリジェクション量を得ることができる。

(もっと読む)

半導体装置

【課題】銅からなるワイヤを用いたワイヤボンディングを行う半導体装置の信頼性を向上させる。

【解決手段】半導体装置が有する半導体チップ10の主面(第1主面)10a上に形成されるパッド(電極パッド)11上に、銅製のワイヤ30の一方の端部(幅広部30b)を、バンプ31を介して接合した構造とする。バンプ31は、銅よりも硬度が低い金属材料である金からなり、バンプ31の幅Wcは、ワイヤ30の幅広部30bの幅Wbよりも狭くなっている。

(もっと読む)

半導体装置の製造方法およびボンディング装置

【課題】半導体装置の生産性に大きく影響をおよぼさず、かつ、ボールのつぶれ形状を一定形状に保つことができる半導体装置の製造方法、ボンディング装置を提供する。

【解決手段】ボンディング装置1は、ボール12のボンディング条件を記憶した記憶部13と、半導体素子Sに対して接触させキャピラリ11のZ軸における第一の位置を検出するとともに、キャピラリ11先端のボール12に対してボンディングした際のキャピラリ11のZ軸における第二の位置を検出する検出部14と、検出部14で検出した第一の位置と、第二の位置との差であるボール12のつぶれ量およびボンディング時間を算出し、一定時間あたりのボール12のつぶれ量を算出する算出部15と、一定時間あたりのボール12のつぶれ量が、所定の数値範囲外である場合にはボンディング条件を調整する第一調整部16を有する。

(もっと読む)

半導体装置におけるワイヤボンディング構造及びその設計方法

【課題】半導体装置を大容量化しても、小型軽量且つ安価で耐久性・信頼性が十分確保可能なワイヤボンディング構造が得られるようにする。

【解決手段】ベース体B上に半導体素子Sとこれに電気的に接続すべき回路部品Cとが間隔をおいて設置、固定され、その半導体素子Sの電極部と回路部品Cとの間が、その間に渡って延びる導電性の金属ワイヤWで結線された半導体装置におけるワイヤボンディング構造であって、ワイヤWが、半導体素子Sの電極部表面に接合される一端部Waと、回路部品Cの、前記電極部表面と高低差ΔLのある表面に接合される他端部Wa′と、その一端部Wa及び他端部Wa′間を一体に接続し少なくとも中間部が上方に凸に彎曲したループ部Wmとを備え、前記高低差ΔLが1〜5mmの設定範囲内に、また前記ループ部Wmのループ高さhが2〜7mmの設定範囲内にそれぞれ設定される。

(もっと読む)

半導体用ボンディングワイヤー

【課題】パラジウムめっきされたリードフレームであっても良好なウェッジ接合性を確保でき、耐酸化性に優れた、銅又は銅合金を芯線とする半導体用ボンディングワイヤーを提供する。

【解決手段】銅又は銅合金から成る芯線と、該芯線の表面に、10〜200nmの厚さで形成されたパラジウムを含む被覆層と、該被覆層の表面に、3〜30nmの厚さで形成された銀とパラジウムとの合金層と、を有し、前記銀とパラジウムとの合金層中の銀の濃度が10体積%以上70体積%以下であることを特徴とする半導体用ボンディングワイヤー。

(もっと読む)

電力変換装置

【課題】電力変換装置においてスイッチング素子のオンオフ動作によって発生するコモンモードノイズを低減できるようにする。

【解決手段】上アーム側スイッチング素子(130)が搭載され、搭載された上アーム側スイッチング素子(130)の一方のドレイン(131)が接する上アーム側パターン配線(40)と、下アーム側スイッチング素子(140)のみが1つ搭載され、搭載された下アーム側スイッチング素子(140)の一方のソース(142)が接する複数の下アーム側パターン配線(50)とを設ける。また、各上アーム側スイッチング素子(130)のもう一方のソース(132)と複数の下アーム側パターン配線(50)とを上アーム側ワイヤ配線(70)で1対1に接続する。そして、下アーム側パターン配線(50)と電力出力端子(20)とを出力端子側ワイヤ配線(80)で1対1に接続する。

(もっと読む)

半導体装置の製造方法

【課題】トランスファ・モールド法において、ボイドの発生を防止した半導体装置と製造方法を提供する。

【解決手段】以下の工程を含むことを特徴とする半導体装置の製造方法:(a)チップ搭載面20Xと、チップ搭載面に形成された複数の接続部3と、チップ搭載面とは反対側の裏面と、裏面に形成された複数の電極パッド5とを有する基板20を準備する工程;(b)主面と、主面に形成された複数のボンディングパッド11と、複数のボンディングパッドと電気的に接続された集積回路と、主面とは反対側の裏面とを有する半導体チップ10を、基板のチップ搭載面に搭載する工程;(c)(b)工程の後、基板のチップ搭載面および半導体チップを樹脂で封止する工程;ここで、(b)工程の後、かつ、(c)工程の前に、基板のチップ搭載面および半導体チップを、プラズマにより処理する。

(もっと読む)

半導体装置及びその製造方法

【課題】多ピンの半導体装置における信頼性の向上を図る。

【解決手段】多ピンのBGA9において、半導体チップ1と配線基板2とを電気的に接続する複数のワイヤ7が、短くかつ細くて内側に配置される複数の第1のワイヤ7aと、第1のワイヤ7aより長くかつ太い複数の第2のワイヤ7bとを有することで、樹脂モールディング時のレジンが細い第1のワイヤ7a間から流れ込むため、レジンによって空気が押し出されてボイドの形成を抑えることができ、多ピンのBGA9の信頼性の向上を図ることができる。

(もっと読む)

41 - 60 / 217

[ Back to top ]