Fターム[5F044LL01]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630) | 直接ハンダ付け状態 (1,160)

Fターム[5F044LL01]の下位に属するFターム

基板の貫通孔を介してハンダ付け (18)

Fターム[5F044LL01]に分類される特許

21 - 40 / 1,142

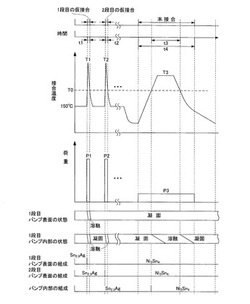

半導体素子の実装方法

【課題】薄型化,狭ピッチ端子化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制することを目的とする。

【解決手段】半導体素子を搭載する毎に加圧状態で加熱して仮接合を行い、全ての半導体素子を仮接合した後、一括して加圧状態で加熱して本接合を行うことにより、薄型化,狭ピッチ端子化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制して積層することができる。

(もっと読む)

はんだ接続用通電部材、配線用基板及びめっき皮膜の形成方法

【課題】CuまたはCu合金からなる通電部材(電極端子)に、Cu成分を含有しないはんだを使用しても、通電部材側とはんだとが十分な接合強度を発現するはんだ接続用通電部材、配線用基板及びめっき皮膜の形成方法を提供する。

【解決手段】CuあるいはCu合金を含む通電部材1上に、ピンホール7を有する置換Snめっき皮膜5と、電解Niめっき皮膜4と、電解Pdめっき皮膜3と、電解Auめっき皮膜2と、がこの順に積層されているはんだ接続用通電部材である。

(もっと読む)

半導体パッケージの製造方法

【課題】接続信頼性が高く、コストに優れた、狭ピッチ化にも対応可能な接続端子を有する半導体パッケージの製造方法を提供する。

【解決手段】半導体素子をフリップチップ実装する配線基板の最上層の導体回路上に、複数の金属ポスト形成用のソルダーレジスト開口を有するソルダーレジスト層を設け、シード層(無電解金属めっき)を形成し、ソルダーレジスト開口と対応する位置にレジスト開口が形成されたドライフィルムレジスト層を形成し、電解金属めっきで金属ポストを形成した後、前記開口内に前記ドライフィルムレジスト層の表面と同等の高さまではんだペーストを充填する工程を含む。はんだを形成する手法として採用されていた電解めっき工法に替わり、はんだペーストの充填(印刷)手法を採用する。

(もっと読む)

電子装置、配線基板、及び、電子装置の製造方法

【課題】フリップチップ接続されて構成される半導体装置などのように、はんだを用いた電極どうしの電気的接続が行われる電子装置においても、チップなどの電子部品の回路、又は、配線基板の回路を変更する以外の手法で、電子部品の電極の接続先を切り替える。

【解決手段】電子装置(例えば、半導体装置100)は、複数の第1電極210を一方の面上に有する配線基板200と、複数の第1電極210とそれぞれ対応して配置された複数の第2電極310を一方の面上に有する電子部品(例えば、チップ300)を有する。第1電極210のうちの少なくとも1つ以上は、複数の分割部分221、222に分割された特定電極220であり、分割部分221、222が、各々異なる配線251、252に接続されている。分割部分221、222のうちの何れか1つ以上が、対応する第2電極310とはんだ110を介して接続されている。

(もっと読む)

三次元実装装置

【課題】半導体デバイスの製造のスループットをさらに向上できるとともに、製造される半導体デバイスの品質の低下を防止できる三次元実装装置を提供する。

【解決手段】三次元実装装置11において、搬送トレイ16は配置面16aaをそれぞれ含む8つの内側トレイ16aを有し且つ各配置面16aaに配置された8つの積層チップ21を搬送し、チャンバ27は全ての内側トレイ16aを収容し、複数の下部ステージ28の各々はチャンバ27内において複数の内側トレイ16aの各々を載置し、複数のチャック29の各々は、チャンバ27内において、配置面16aaに配置された積層チップ21の各々と一対一で対応して配設され、各下部ステージ28及び各複数のチャック29が各下部ステージ28及び各複数のチャック29の間を詰めるように移動する。

(もっと読む)

樹脂封止型半導体装置の製造方法及び樹脂封止型半導体装置

【課題】 狭い隙間への含浸性が優れ、充填剤の沈降及びボイドの発生が少ない液状エポキシ樹脂組成物、及び半導体等の素子の回路形成面が基板の回路形成面とバンプを介して対向するようにフリップチップ実装し、素子と基板の隙間に該樹脂組成物を充填した高成形性、高信頼性の電子部品装置を提供する。

【解決手段】 (A)エポキシ樹脂、(B)硬化剤及び(C)無機充填剤を必須成分とし、必要に応じ(D)硬化促進剤を含む、無溶剤型の液状エポキシ樹脂組成物であって、回転式粘度計の回転数n1及びn2(n1/n2<0.5)で測定した粘度比η1/η2すなわちチキソトロピック指数が、0.8より小さい液状エポキシ樹脂組成物を用いる。

(もっと読む)

半導体装置の製造方法および半導体装置の製造装置

【課題】はんだバンプ表面の酸化膜を良好に除去しつつ、半導体素子の反り等を防止し、はんだバンプの接続性向上を可能にした半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、第1の半導体チップ2と第2の半導体チップ5との間の隙間をスペーサ突起4により保持しつつ、第2の半導体チップ5のはんだバンプ3と第1の半導体チップ2の金属電極1とを仮固定する。次いで、仮固定された積層体を、荷重を負荷しながらギ酸等のカルボン酸ガス雰囲気で加熱し、はんだバンプ3表面の酸化膜を還元・除去しつつはんだバンプ3の接合を行う。

(もっと読む)

活性樹脂組成物及び表面実装技術

【課題】表面実装技術において、フラックスの洗浄工程を不要とし、製造コストの削減、生産性を向上させ、硬化後の塗布樹脂及びアンダーフィル樹脂等に気泡やボイド等が全く生じない活性樹脂組成物の提供。

【解決手段】プリント配線基板1表面の少なくとも一部に下記活性樹脂組成物3を塗布し、表面実装部品4をプリント配線基板1上に搭載し、リフロー半田付けを行い、アンダーフィル樹脂11を充填し、その後、塗布樹脂3及びアンダーフィル樹脂11を加熱硬化する表面実装技術であって、アンダーフィル樹脂11の充填前及び/又は後に、真空操作及び/又は塗布樹脂3とアンダーフィル樹脂11の何れの硬化温度よりも低い温度での加熱を行う。活性樹脂組成物3は、エポキシ樹脂100重量部に対し、ブロックカルボン酸化合物1〜50重量部カルボン酸化合物1〜10重量部、並びに硬化反応開始温度150℃以上の硬化剤1〜30重量部を含有する。

(もっと読む)

半導体パッケージ基板の製造方法

【課題】高密度のバンプピッチに対応可能な半導体パッケージ基板の製造方法を提供する。

【解決手段】半導体パッケージ基板の製造方法は、接続パッド103を有するベース基板を準備する段階と、ベース基板上に、ポリイミドを含む保護層106および金属層を積層する段階と、金属層および保護層にオープン部を形成して接続パッドを露出させる段階と、オープン部にポストバンプ115を形成する段階と、金属層を除去する段階とを含んでなるものである。

(もっと読む)

半導体装置

【課題】半導体パッケージを実装基板から取り外すリペアが容易であって、半導体パッケージと実装基板との接続部の耐衝撃性を向上させることができる半導体装置を提供する。

【解決手段】半導体装置100は、半導体素子4が接続された半導体パッケージ1と、実装基板2とがはんだバンプ3を介して電気的及び機械的に接続されてなり、半導体パッケージ1は、半導体素子4が接続されるとともに実装基板2と接続される半導体パッケージ用配線板5を有し、半導体パッケージ用配線板5に形成された電極パッド22のコア層11側には第1応力緩和層21が配置されており、実装基板2に形成された電極パッド33の層間絶縁層31側には第2応力緩和層34が配置されており、第1応力緩和層21の25℃の弾性率が2.5GPa以下であり、第2応力緩和層34の25℃の弾性率が3GPa以下かつ第2応力緩和層34の平面方向の25℃の熱膨張係数が8×10-6/℃以下である。

(もっと読む)

電子装置の寿命予測方法およびそれを用いた電子装置の設計方法

【課題】従来の方法に比べて寿命予測精度が向上した電子装置の寿命予測方法およびそれに基づく電子装置の設計方法を確立することにある。

【解決手段】高温放置によるはんだ接合部の物性値の変化またははんだの疲労寿命の変化のどちらかを寿命予測に取り入れることによって寿命予測を行なうものである。前記はんだ接合部の物性値の変化またははんだの疲労寿命の変化は、熱処理温度及び熱処理時間との関係により求められるものである。そして、これらの変化を定式化して前記寿命予測に取り入れるものである。

(もっと読む)

プリント基板

【課題】ノーマルレジスト構造のランドを有するプリント基板において、ランド上へのはんだ塗布量のばらつきを抑制しつつ、はんだの接続信頼性を向上すること。

【解決手段】ノーマルレジスト構造のランドを有するプリント基板であって、絶縁基材の一面上に形成されたランドの側面と、ランドを外部に露出させる開口部を有して絶縁基材の一面上に形成されたソルダーレジストの開口部側壁面との対向領域に、ランドの側面及び開口部の側壁面に接しつつ絶縁基材の一面から所定の高さを有する固形状の充填部材を設けた。この充填部材は、はんだ付け時のリフローによって溶融され、且つ、ランドの表面に対する濡れ性が、はんだ付け時にランドの上面に配置されるはんだの溶融状態よりも低い樹脂材料を用いて形成される。

(もっと読む)

高周波モジュールおよび高周波モジュールの検査方法

【課題】高周波回路チップ上の回路と、モジュールを構成する配線基板上の回路についてその相対位置を検出することによって、容易に実装状態が測定できる高周波モジュールおよび高周波モジュールの測定方法を提供する。

【解決手段】入出力端子6を備えた高周波回路チップ1と、高周波回路チップ1の入出力端子6を、バンプ5を介してフリップチップ接続する接続用パッド7を含む配線部を備えた配線基板2とを備えた高周波モジュールであって、入出力端子の2端子間に接続された、スパイラルインダクタ3sと、スパイラルインダクタ3sに対向する位置に配設され、接地電位に接続された検出用導体4dとを備え、接続用パッド間のインダクタンスを測定することによって、スパイラルインダクタ3sと検出用導体4dとの距離の変化に起因する入出力端子6と接続用パッド7間の距離の変化を測定可能に構成される。

(もっと読む)

圧電装置

【課題】

本発明は、集積回路素子の電極パッドと、半田バンプとの接合強度の低下を防ぐ圧電装置を提供することを課題とする。

【解決手段】

本発明の圧電装置100は、素子搭載部材110と、素子搭載部材110に搭載されている圧電素子120と、素子搭載部材110の表面に形成されており、素子搭載領域118aおよび引き回し領域118bを含んでいる金属パターン118と、半田バンプ132によって金属パターン118の素子搭載領域118aに電気的に接続されている集積回路素子130とを備え、金属パターン118が素子搭載領域118aと引き回し領域118bとの間に設けられた凸部119を有しており、凸部119の少なくとも表面部分が金属酸化物から成る。

(もっと読む)

センサ装置

【課題】回路チップの一面側にセンサチップを電気的に接続するとともに、回路チップの一面側に接続部材を設け、接続部材を介して回路チップを基台に支持してなるセンサ装置において、接続部材と基台とのはんだ接合性を向上させる。

【解決手段】接続部材は、Ag−Sn合金の焼結体よりなり、回路チップ20側から基台10側に向かって先窄まりとなるアスペクト比が1以上の円錐形状をなす円錐部材40であり、基台10の一面11に設けられたはんだ60により、円錐部材40の先端部42側と基台10とが接合されている。

(もっと読む)

半導体パッケージ基板及び半導体パッケージ基板の製造方法

【課題】本発明は、半導体パッケージ基板及び半導体パッケージ基板の製造方法に関する。

【解決手段】本発明の一実施例によると、パッドが形成されたキャリア基板を準備する段階と、前記パッドの上部に絶縁層を形成する段階と、前記キャリア基板を除去する段階と、前記絶縁層及び前記パッドの上部に回路層を形成する段階と、前記パッドの一部をエッチングし、前記絶縁層の内部に開口部を形成する段階と、を含む半導体パッケージ基板の製造方法が提供される。

(もっと読む)

半導体装置、半導体装置の製造方法及び電子機器

【課題】低いリフロー温度で信頼性良く接合できる接合部を備えた半導体装置、半導体装置の製造方法及び電子機器を提供する。

【解決手段】素子11上に形成された第1電極12と、基板21上に形成された第2電極22との上に、それぞれSn-Bi又はSn-Inを含むはんだ層13、23を形成し、これらのはんだ層13、23の間にSn-Ga合金ボール14を、はんだ層13、23の融点よりも高く、且つSn-Ga合金ボール14の融点よりも低い温度でリフロー接合する。リフロー接合の際にはんだ層13、23とSn-Ga合金ボール14との界面にSn-Bi-Ga合金層15又はSn-In-Ga合金層が形成され、Sn-Ga合金ボール14からのGaを含む融液の拡散が阻止される。

(もっと読む)

ダイシングテープ一体型接着シート、半導体装置、多層回路基板及び電子部品

【課題】対向する部材の端子間の接続および封止を同時に行うことができるダイシングテープ一体型接着シートを提供する。

【解決手段】ダイシングテープ一体型接着シート10は、支持体の第一の端子と、被着体の第二の端子を、半田を用いて電気的に接続し、前記支持体と前記被着体とを接着する接着フィルム3と、ダイシングテープ2とを含む積層構造を有し、前記接着フィルム3を前記支持体の第一の端子が形成された面に貼り付ける際の貼り付け温度をT[℃]、前記接着フィルム3に掛ける圧力をP[Pa]、前記貼り付け温度における接着フィルム3の溶融粘度をη[Pa・s]としたとき、1.2×103≦(T×P)/η≦1.5×109の関係を満足し、前記貼り付け温度Tは、60〜150℃、前記圧力Pは、0.2〜1.0MPa、前記貼り付け温度Tにおける接着フィルム3の溶融粘度ηは、0.1〜100,000Pa・sである。

(もっと読む)

はんだ実装基板及びその製造方法、並びに半導体装置

【課題】 低コストで製造でき且つ実装信頼性に優れたはんだ実装基板及びその製造方法、並びに半導体装置を提供する。

【解決手段】 はんだ実装基板100は、銅を含む銅系金属層20を備える配線22及びはんだ実装部21を少なくとも一方面に複数備え、配線22及びはんだ実装部21の銅系金属層20が露出した領域に、銅と反応する官能基を少なくとも一つを有する有機化合物を反応させることにより、有機化合物からなる有機皮膜30を形成する工程と、有機皮膜30が形成されたはんだ実装部21の該有機皮膜30の一部を除去して開口31を設けて、銅系金属層20の一部を露出させる工程と、を具備する。

(もっと読む)

回路基板、半導体パワーモジュール、製造方法

【課題】半導体素子から多層基板への熱拡散性能の向上、および、多層基板と半導体素子との接合強度の向上。

【解決手段】半導体パワーモジュール30は、セラミックス多層基板300と、接合層310と、半導体素子330を備える。接合層310は、セラミックス多層基板100側が平面状に形成されている薄膜層である。接合層310の絶縁接合部312は、半導体素子330側の端部からセラミックス多層基板300側の端部に向けて先細な形状に形成されている。半導体素子130の実装時、半導体素子330の突状部335は窪み部316内に収められ、接合層310の導電接合部311と導通する。こうすれば、半導体素子330と接合層との接合面積を広く接合でき、多層基板と半導体素子との接合強度、絶縁性能を確保しつつ、半導体素子から多層基板への熱拡散性能を向上できる。

(もっと読む)

21 - 40 / 1,142

[ Back to top ]