Fターム[5H740BC02]の内容

電力変換一般 (12,896) | 主回路スイッチング素子の制御態様 (2,095) | ターンオフ (1,003)

Fターム[5H740BC02]に分類される特許

41 - 60 / 1,003

インバータ装置

【課題】複数のインバータの間における電圧の干渉による悪影響の抑制を、省スペースな装置において実現することができるインバータ装置を提供する。

【解決手段】インバータ装置は、PN母線に接続された第1インバータと、PN母線に接続された第2インバータと、PN母線における第1インバータと第2インバータの間に接続されたクランプ回路とを備える。クランプ回路は、ツェナーダイオードと、スイッチング素子とを備える。ツェナーダイオードは、PN母線におけるP母線にカソードが接続しN母線にアノードが接続する。スイッチング素子は、P母線とN母線との間に介在し、制御端子がツェナーダイオードのアノードと接続したものである。

(もっと読む)

電流検出回路、およびモータ制御装置

【課題】プリント配線基板上に搭載されるFETに流れる電流を、FETオン時のオン抵抗Ronと配線パターン抵抗Rpによる電圧降下VDGを基に検出する際に、配線パターンの抵抗Rpにより発生する電圧降下分(オフセット分)をキャンセルして、FET(Qo)のドレイン・ソース間電圧VDSを検出する。

【解決手段】本発明の電流検出回路1は、FET(Qo)のドレイン端子Dと回路グランドGとの間に、第1の抵抗Rdと第2の抵抗Roの抵抗直列回路を接続する。そして、第2の抵抗Ronと第1の抵抗Rdの抵抗値の比(Ro/Rd)が、FET(Qo)のオン抵抗Ronと配線パターンRpの抵抗値の比(Ron/Rp)に一致するように設定する。そして、この第1の抵抗Rdと第2の抵抗Roとの接続点(ノードN1)と回路グランドGとの間の電圧VRoを、FET(Qo)に流れる電流の検出信号として出力する。

(もっと読む)

電源スイッチ保護回路及び車載機器

【課題】過電流から電源スイッチ回路を適切に保護する技術を提供する。

【解決手段】電源スイッチ保護回路は、電源スイッチ回路と、第1回路素子及び第2回路素子の両方がオン状態を示す場合に電源スイッチ回路をオン状態とし、第1回路素子及び第2回路素子の少なくとも一方がオフ状態を示す場合に電源スイッチ回路をオフ状態とする電源スイッチ制御回路と、電源スイッチ回路の出力側の短絡を検出し、短絡が検出されているか否かを示しかつ第1回路素子のオフ状態及びオン状態を切り換えるための短絡検出信号を出力する短絡検出回路と、所定時間内における短絡検出信号の状態変化に応じて、短絡が発生しているか否かを判定し、短絡が発生していると判定すると、第2回路素子がオフ状態を維持するように電源スイッチ制御回路を制御する制御部と、を備える。

(もっと読む)

ゲート駆動回路、電力変換回路、3相インバータ、及びゲート駆動方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】ハイサイドトランジスタ21とローサイドトランジスタ22の少なくとも一方は、ノーマリオン型トランジスタである。2つのゲート駆動回路11、12の少なくとも一方は、正電源から供給される第1電源電圧VDDと、負電圧源30から供給され接地電圧GNDよりも低い第2電源電圧VNEGとに応じた駆動電圧GH、GLを、ノーマリオン型のトランジスタのゲートに出力する。制御回路40は、第2電源電圧VNEGが参照電圧Vrefよりも高い場合、ハイサイドトランジスタ21に流れるドレイン電流を遮断する。

(もっと読む)

電源装置、および電源装置の電圧切替方法

【課題】フレア現像用高圧出力として、NchFET駆動によるフルブリッジ回路を構成する場合、NchFET駆動用の電源は、DC(直流)バイアス電源から生成し、単独のFET駆動用電源を不要とするとともに、NchFETのスイッチング駆動に必要な最低限のゲート−ソース端子間への電圧の供給を可能とする。

【解決手段】スイッチング素子によりパルス電圧をトナーに印加し、前記トナーを浮遊させて現像を行うフレア現像方式の画像形成装置に用いられる電源装置であって、DCバイアス電源111の出力電圧を分圧して、前記スイッチング素子のゲート端子−ソース端子に所定の電圧を出力する分圧部111aを備える。

(もっと読む)

ラインフィルタ、ラインフィルタを搭載したスイッチング電源及び画像形成装置

【課題】 スイッチング部からの熱を放熱する放熱部の影響によるノイズを低減し、且つ、Xコンデンサの電荷を放電する放電抵抗による消費電力を低減する。

【解決手段】 スイッチング部の放熱部とトランスの入力側を接続して、前記放熱部に流れる電流をスイッチング手段に還流する第1の電流経路を形成し、整流部と前記トランスとの間のライン間に接続されたコンデンサと、トランスの出力側と、コンデンサを接続した第2の電流経路を形成したラインフィルタ。

(もっと読む)

電流制限回路

【課題】ノイズ耐性が高く、且つ、製造プロセス、電源、及び電源電圧が変動するような場合においても精度が高い、出力トランジスタに対する電流制限回路を提供する。

【解決手段】電流制限回路が、基準トランジスタと、基準トランジスタに所定の電流を流す電流源と、出力トランジスタがオンした時の両端の第1の電位差と基準トランジスタの両端の第2の電位差を比較する比較器であって、第1の電位差が第2の電位差よりも大きくなった場合に、出力トランジスタをオフするように制御する電流制限信号を出力する、比較器とを備える。基準トランジスタは、出力トランジスタとは素子サイズの異なる同型のトランジスタであり、基準トランジスタがオンした時のオン抵抗は、出力トランジスタがオンした時のオン抵抗の1/Nの大きさ(Nは1より大きい数)であり、更に、基準トランジスタがオンするように基準トランジスタのゲートにバイアスがかけられている。

(もっと読む)

半導体モジュール

【課題】半導体スイッチを小さい負担で駆動できるとともに、半導体スイッチに十分なゲート電流を流すことができ、しかも、ゲート配線のインピーダンスによる障害を回避できる半導体モジュール。

【解決手段】ゲートに印加される電圧に応じてオンオフする半導体スイッチQ1と、半導体スイッチのソース電位に対して正極性を有する正極コンデンサ110と、半導体スイッチのソース電位に対して負極性を有する負極コンデンサ111と、正極コンデンサを充電する機能を有し、半導体スイッチをターンオンさせる場合は正極コンデンサからの電流を半導体スイッチのゲートに流すターンオン制御部112と、負極コンデンサを充電する機能を有し、半導体スイッチをターンオフさせる場合は負極コンデンサからの電流を半導体スイッチのゲートに流すターンオフ制御部113を備える。

(もっと読む)

パワー半導体モジュール

【課題】 電力損失が小さく、発生ノイズが小さいパワー半導体モジュールを実現する。

【解決手段】 ワイドバンドギャップ半導体を利用したユニポーラ型スイッチング素子(ワイドバンドギャップ半導体スイッチング素子)1とシリコン半導体を利用した絶縁ゲート型バイポーラトランジスタ(Si−IGBT)2を並列接続したパワー半導体モジュールで、ワイドバンドギャップ半導体素子1のチップ面積はSi−IGBT2のチップ面積よりも小さいことを特徴とする。

(もっと読む)

ノイズ低減装置およびこれを備えた電力変換装置

【課題】電力変換回路の入力側主回路ラインとアースとの間に生じる雑音端子電圧を効果的に低減することができるノイズ低減装置を提供する。

【解決手段】インバータ回路4の直流入力端子間に直列接続されたコンデンサ41,42の接続中点とアースとの間に、補償コンデンサCcと接地コンデンサCeとを直列接続し、補償コンデンサCcの両端に二次巻線を並列に接続した相殺変圧器T2とを備え、インバータ回路4のスイッチング素子がオンオフ動作するときに発生する雑音電圧と逆極性で大きさが同じ相殺電圧を補償コンデンサCcの両端に発生させる。相殺電圧は、補償コンデンサCcと相殺変圧器T2との間に挿入された波形調整回路によって雑音電圧の波形と同形状に波形調整される。

(もっと読む)

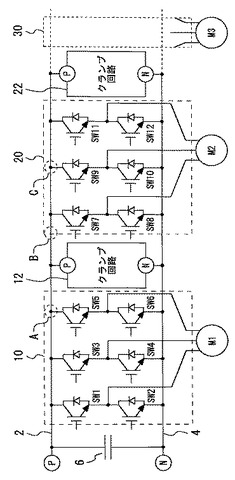

電力変換装置

【課題】スイッチング素子を複数並列に接続して逆変換器等を構成した場合にも簡易かつ確実に電流アンバランスを解消することができる電力変換装置を提供する。

【解決手段】ゲート調整回路12は、基準素子ユニット501における直流電流検出器541の直流電流の検出値Id1および、基準素子ユニット501以外の素子ユニット502における直流電流検出器542の直流電流の検出値Id2に基づいて、それぞれ時間γ1および時間γ2から時間差Δtを電流アンバランス量として算出する。ゲート調整回路12は、時間差Δtを次の第1状態におけるターンオフのタイミングで、ゲート駆動回路552uの動作信号S2uに遅延時間として付加する。

(もっと読む)

ゲート駆動回路

【課題】ワイドギャップ半導体のターンオフの速度を高速化できるゲート駆動回路。

【解決手段】負極が接地された正電源E1と、正極が接地された負電源E2と、正電源の正極と負電源の負極との間に設けられ、制御信号を生成する制御回路11と、正電源の正極と負電源の負極との間に設けられたトランジスタQ1とトランジスタQ2との直列回路と、ドレイン端子、接地されたソース端子及びQ1とQ2との接続点に接続されたゲート端子を備えたワイドバンドギャップ半導体からなるスイッチング素子GaNFETと、制御信号のオフ時にQ1を所定時間だけオンさせQ1を介して負電源の電圧をスイッチング素子のゲート端子に印加するターンオフ制御回路13と、スイッチング素子のゲート端子と接地との間に設けられ、制御信号のオフ時にそのゲート端子とソース端子を短絡させるトランジスタQ3とトランジスタQ4との直列回路を備える。

(もっと読む)

出力駆動回路及びトランジスタ出力回路

【課題】本発明は、出力駆動回路及びトランジスタ出力回路を提供する。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

(もっと読む)

温度検知回路

【課題】電力変換器のヒートシンクに実装された複数のサーマルリードスイッチを使用した温度検知回路において、最小の構成にて、動作したサーマルリードスイッチを特定することが可能な温度検知回路を提供することである。

【解決手段】設定温度以上で開放するサーマルリードスイッチと並列に抵抗器を接続し、測定点分を直列に接続し、各抵抗器の抵抗値は異なる値とする。開放するサーマルリードスイッチにより、この直列体のインピーダンスが変化するため、抵抗値や分圧された電圧値を判別することで動作したサーマルリードスイッチを特定することができる。複数使用したサーマルリードスイッチの動作部位を簡略な回路構成にて判別することが可能である。

(もっと読む)

絶縁不良診断装置および絶縁不良診断方法

【課題】高電圧バッテリ10に接続される部材(インバータINV1〜INV4)が増加すると、高電圧バッテリ10と車体との間の浮遊容量が大きくなったり、絶縁抵抗の抵抗値が小さくなったりすることで、これら浮遊容量や絶縁抵抗に起因したインピーダンスが低下し、絶縁不良の診断精度の低下を招くおそれがあること。

【解決手段】製品出荷に先立ち、高電圧バッテリ10にインバータINV1〜INV4が接続され、これらが車体に搭載された後、出力部40から診断信号dsを出力する。そして、これに伴う抵抗体42およびコンデンサ44間の電位の変動量に基づき、絶縁不良の有無を判断する判定値を生成して、不揮発性メモリ48に記憶する。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

電源装置の駆動回路及び電源装置

【課題】遷移期間においてハイサイドトランジスタQ1がオンしないようにする。

【解決手段】高電位電源ラインと低電位電源ラインとの間に直列に接続されたハイサイドトランジスタとロウサイドトランジスタと,両トランジスタの接続ノードと出力端子との間に設けられたインダクタとを有する電源装置の前記両トランジスタを駆動する駆動回路であって,前記ハイサイドトランジスタのゲートを駆動する第1のゲートドライバと,前記ロウサイドトランジスタのゲートを駆動する第2のゲートドライバとを有し,前記ハイサイドトランジスタがオンでロウサイドトランジスタがオフの第1の状態から,前記ハイサイドトランジスタがオフでロウサイドトランジスタがオンの第2の状態に遷移する遷移期間で,前記第1のゲートドライバは前記ハイサイドトランジスタのゲートを前記低電位電源ラインの電位より低い第1の電圧に駆動する電源装置の駆動回路。

(もっと読む)

半導体装置

【課題】パワーデバイスの誤動作を防ぐ。

【解決手段】直列に接続された2つのパワーデバイスのうち高電位側のパワーデバイスを駆動制御する半導体装置であって、高電位側のパワーデバイスの導通を示す第1状態及び高電位側のパワーデバイスの非導通を示す第2状態を有する入力信号の第1,第2状態へのレベル遷移に対応して、それぞれ第1,第2のパルス信号を発生させるパルス発生回路と、第1,第2のパルス信号を高電位側へレベルシフトして、それぞれ第1,第2のレベルシフト済みパルス信号を得るレベルシフト回路と、第1,第2のレベルシフト済みパルス信号を少なくとも第1,第2のパルス信号のパルス幅分遅延させて、それぞれ第1,第2の遅延済みパルス信号を得る遅延回路と、第1の遅延済みパルス信号をセット入力から入力し、第2の遅延済みパルス信号をリセット入力から入力するSR型フリップフロップとを備える。

(もっと読む)

電力変換装置

【課題】還流ダイオードの逆回復による損失を低減し、スイッチング時に発生する振動を抑制する電力変換装置を提供することにある。

【解決手段】電力変換装置1は、対になる2つのスイッチング素子4a,4bと、スイッチング素子4a,4bのそれぞれに逆並列に接続された還流ダイオード5a,5bと、スイッチング素子4a,4bに印加される主電圧よりも低い電圧の補助電源21a,21bと、スイッチング素子4aのターンオフ後からスイッチング素子4bのターンオンまでの間に、スイッチング素子4a及び還流ダイオード5aに補助電源21aの電圧を印加し、スイッチング素子4aのターンオン動作中に、スイッチング素子4aのスイッチング速度を変化させる主素子制御回路6aとを備える。

(もっと読む)

41 - 60 / 1,003

[ Back to top ]