Fターム[5J043DD00]の内容

パルス発生器 (3,485) | 回路要素、回路素子 (407)

Fターム[5J043DD00]の下位に属するFターム

特殊素子 (4)

FET (49)

BiTr (5)

ダイオード(電流ミラー回路のものを除く) (15)

FF(全体がFFのものを除く) (34)

レジスタ、シフトレジスタ (17)

論理回路(アンド、インバータ等) (62)

カウンタ (26)

CPU、メモリ (25)

遅延素子、遅延線 (30)

単安定回路(全体が単安定回路を除く) (8)

変成器、トランス、コイル(リレーを除く) (9)

水晶、圧電振動子(ブロック図を除く) (17)

比較回路、ヒステリシス、シュミット回路 (42)

定電流回路(差動増幅器の電流源を除く) (26)

Fターム[5J043DD00]に分類される特許

1 - 20 / 38

ディジタル制御発振装置および高周波信号処理装置

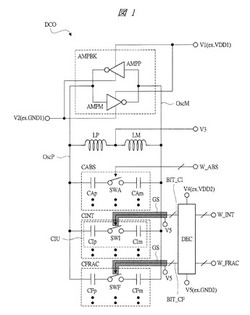

【課題】DNLの低減を実現可能なディジタル制御発振装置を提供する。

【解決手段】例えば、発振出力ノードOscP,OscM間に並列に結合されるアンプ回路ブロックAMPBK、コイル素子LP,LM、複数の単位容量ユニットCIU等を備え、各CIUは、容量素子CIp,CImと、当該CIp,CImを発振周波数の設定パラメータとして寄与させるか否かを選択するスイッチSWIを備える。ここで、SWIは、デコーダ回路DECからのオン・オフ制御線BIT_CIによって駆動され、当該BIT_CIは、シールド部GSによってOscP,OscMとの間でシールドされる。

(もっと読む)

発振回路、発振装置およびクロックジェネレータ

【課題】消費電力を低減することができる発振回路を提供する。

【解決手段】入力信号が含むアナログ成分をデジタル信号に変換するアナログ/デジタル変換回路100と、アナログ/デジタル変換回路100で変換されたデジタル信号D1について、予め設定された周波数帯域成分のみを基準信号として通過させるバンドパスフィルタ101と、バンドパスフィルタ101を通過した基準信号D2と、PLLループ内に設けられる電圧制御発振器203からの出力信号D3との位相差が一定となるように電圧制御発振器203にフィードバック制御を行って発振させるPLL回路200とを備え、バンドパスフィルタ101は、所定の条件に基づいて、アナログ/デジタル変換回路100で変換されたデジタル信号D1の所定ビット幅について、「0」に固定するマスク処理を実行するマスク処理部102を備える。

(もっと読む)

正極側へまたは負極側へパルスを一つだけ発生する回路

【課題】ワンスイッチでワンパルスを出力し、トランジスターへの接続も可能な信号を出力できる技術を提供する。

【解決手段】コンデンサーの放電、または、充電が完了することで、電圧の変化が得られることを利用した技術であって、正極9に接続された抵抗1を、片方が負極8に接続されたコンデンサー2と片方が負極8に接続された通電のためのスイッチ3に、直列に接続する。さらに、この接続ノード7を、コンデンサー5とコンデンサー4に接続し、コンデンサー5の他方は負極8に接続し、コンデンサー4の他方は抵抗6を介して負極8に接続する。このコンデンサー4と抵抗6の接続ノードから信号を出力する構成を有する。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

大きな温度変動に対する発信周波数の安定化方法

【課題】

超高温から極低温までの温度変動が極めて大きい環境に設置される無線機器に適用できる発信周波数の安定化方法を提供する。

【解決手段】

複数の発信回路を備え、筐体内の温度を測定する筐体内温度測定ステップと、測定した筐体内温度Tと予め定められた温度T0、T1、・、Tk、・Tnとの大小関係から測定した温度範囲を判定する温度範囲判定ステップと、 温度範囲判定ステップが判定した温度範囲に応じて複数の発信回路のいずれかを選択する回路選択ステップとを有し、筐体内温度TがTk−1≦T<Tkの範囲であった場合に、回路選択ステップは当該温度範囲において、発信器の発信周波数が希望の範囲に納まるように予め調整されている発信回路等を選択する。

(もっと読む)

半導体装置

【課題】周囲温度や外部電源電圧の変化による高速OCOに与える参照電圧および参照電流の変動を防止し、電源モジュールの回路面積が小さい半導体装置を提供する。

【解決手段】高速OCO10は、参照電流および参照電圧で定まる大きさの高速クロックを出力する。温度センサ5は、高速OCO10の周囲温度を検出し、電圧センサ4は、高速OCO10の動作電圧を検出する。電源モジュール12は、BGRを含み、BGRが出力する基準電圧に基づいて、参照電圧、参照電流、高速OCOの動作電圧を生成する。フラッシュメモリ8は、高速OCO10の周囲温度および動作電圧に対応する、参照電圧および参照電流のトリミングコードを定めたテーブルを記憶する。ロジック部13は、検出された周囲温度および動作電圧に対応する参照電圧および参照電流のトリミングコードに基づいて、参照電流および参照電圧の値を調整する。

(もっと読む)

パルス生成回路およびパルス生成方法

【課題】電源電圧の変動しやすい容量の小さい電源である環境下でも、安定したパルス信号を生成できるようにする。

【解決手段】タイミング制御回路1−1,1−2と論理回路2−1とを設ける。タイミング制御回路1−1,1−2は、放電制御端子S11,S21と充電制御端子S12,S22,と信号出力端子T1,T2を有し、内部に時定数素子を備えている。先ず、充電制御端子S12,S22へ充電の開始を指示し、端子T1,T2から出力される電圧VT1,VT2を「H」レベルとする。次に、放電制御端子S11へ放電の開始を指示し、遅延時間τ1経過後に電圧VT1を「L」レベルとし、タイミング制御回路1−2での放電を開始させ、遅延時間τ2経過後に電圧VT2を「L」レベルとする。このタイミング制御回路1−1,1−2からの電圧VT1,VT2を論理回路2−1へ与え、論理回路2−1よりタイミング制御回路1−2での遅延時間τ2をパルス幅とするパルス信号PS1を得る。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

パルス発生回路

【課題】電源オフした直後に電源を再投入しても正常にパルス生成動作を再開できるようにすること。

【解決手段】このパルス発生回路は、第1のDフリップフロップ回路11のセット端子及びリセット端子をそれぞれコンデンサC11,C12を介してグラウンド又は電源に接続し、第1のDフリップフロップ回路11のQ出力端子とセット端子間及びQバー出力端子とリセット端子間にそれぞれ第1の抵抗R11,R12を接続し、前記セット端子、リセット端子、Q出力端子又はQバー出力端子のうちのいずれかの端子とグラウンド間に第2の抵抗RGを接続している。また、第1のDフリップフロップ回路11のQ出力端子を第2のDフリップフロップ回路20のクロック端子に接続し、第2のDフリップフロップ回路20のデータ端子及びセット端子を電源に接続し、第2のDフリップフロップ回路20のQバー出力端子とリセット端子間に第3の抵抗R2を接続した。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

パルス発生装置

【課題】良好な信号レベルのパルス信号を効率よく発生するのに好適なパルス発生装置を提供する。

【解決手段】パルス発生装置100を、起動開始信号D0の入力に応じて単位パルス信号を発生する、各々の信号出力部が独立した単位パルス発生回路20_1〜20_Nと、単位パルス発生回路20_1〜20_Nのうち単位パルス信号を出力する予定の一部の回路の信号出力端子を順次選択して、該選択した信号出力端子を共通の信号出力線Pu_Coutに電気的に接続し、残りの単位パルス発生回路の信号出力端子を共通の信号出力線Pu_Coutから電気的に切断するスイッチ制御回路30及び選択スイッチ40とを含む構成とした。

(もっと読む)

クロック信号生成装置

【課題】本発明は、温度特性、電源電圧特性、個体バラツキを吸収し、最適なノンオーバーラップ時間を有する2相クロック信号を確実に生成できる信頼性の高いクロック信号生成装置を提供することを目的とする。

【解決手段】本発明のクロック信号生成装置は、ノンオーバーラップクロック信号を使用する負荷回路において使用される2相クロック信号の遅延時間を可変する可変遅延器と、2相クロック信号におけるHレベル区間のノンオーバーラップ時間を検出し、ノンオーバーラップ時間に応じた検出信号を出力するノンオーバーラップ検出器と、ノンオーバーラップ検出器からの検出信号に基づいて可変遅延器を制御する制御信号を生成する制御信号生成部と、を備えている。

(もっと読む)

基準クロック補正回路、基準クロック補正方法およびプログラム

【課題】基準信号を切り替えても発振器を自走状態にさせることの少ない基準クロック補正回路を提供する。

【解決手段】本発明に係る基準クロック補正回路1は、複数の基準信号の各々の安定度が良好であるか否かを判断する複数のクロック安定度検出部21a〜cと、複数の基準信号の中で安定度が良好である基準信号を選択基準信号102とする基準信号設定部22と、選択基準信号と基準クロック信号101を用いて制御値105を算出する発振器制御部12と、制御値に基づいて基準クロック信号を発振する発振器13とを有する。

(もっと読む)

電圧制御装置およびクロック出力装置

【課題】電圧制御型水晶発振器(VCXO)から出力される信号の周波数をより高精度に制御することができる電圧制御装置20を提供する。

【解決手段】本発明の電圧制御装置20は、電圧制御型水晶発振器(VCXO)の温度毎の制御電圧値を、異なる条件下で予め2種類測定しておき、実際に温度補正を行う際には、現在のVCXOの温度に対応する制御電圧値を、それぞれの測定条件毎に1つずつ抽出し、抽出した制御電圧値を平均したものを現在の温度における制御電圧としてVCXOに供給する。

(もっと読む)

データ受信装置およびマイクロコンピュータ

【課題】CR発振回路に温度変化や経年変化が生じても正確な周波数を持つクロック信号を生成する。

【解決手段】CR発振器12の温度を示すA/D変換値とCR発振回路8の逓倍数を決める逓倍数設定値FMULRとを対応付けてEEPROM3に記憶し、A/D変換値(検出温度T)に応じた逓倍数設定値FMULRを読み出してCR発振回路8のレジスタに設定する。通信回路7が同期信号を受信するごとにクロック信号CLKを計数して1ビット長を計測し、その計数値XAと正規の1ビット時間に対する基準周期に基づく基準計数値XBとに基づいて逓倍数設定値FMULRを補正し、補正後の逓倍数設定値FMULRを検出温度Tに対応させてEEPROM3に書き込む。

(もっと読む)

パルス発生回路およびUWB通信装置

【課題】素子性能限界に近い超広帯域超高周波でスカート特性の良いバンドパスフィルタが必要であった。

【解決手段】起動信号に呼応して所定形状のパルスを出力端子に出力するパルス発生回路において、該起動信号から該起動信号と所定量の時間差を伴った複数の信号{Di}を発生する回路と、所定の電気量の電気エネルギーを供給する複数の電源{Ej}と前記信号{Di}の少なくとも一部の信号の論理関数値によって所定順序で前記出力端子に前記電源{Ej}を順次切り替えて接続するスイッチ回路と、を含んでパルス発生回路を構成する。

(もっと読む)

電圧制御発振器の位相雑音最適化方法および位相雑音最適化装置

【課題】電圧制御発振器から出力される発振信号の発振周波数にかかわらず電圧制御発振器の位相雑音を最適化する位相雑音最適化方法および位相雑音最適化装置を提供する。

【解決手段】電圧制御発振器の発振信号を平滑化した検出電圧値を生成する。電圧制御発振器から出力される発振信号の出力振幅と位相雑音との関係によって示される位相雑音が最適となる出力振幅に基づいて設定された基準電圧値の範囲と検出電圧値とを比較して、比較結果に応じた判定信号を出力する。判定信号に基づいて電圧制御発振器の電流源のスイッチの開/閉を制御する電流切り替え信号を生成して出力することで出力振幅が安定し、位相雑音が最適となる。

(もっと読む)

同期回路

【課題】広い範囲で遅延調整を可能にしてACタイミングを確保し易くする。

【解決手段】フリップフロップ回路FF1と組合せ論理回路LOGIC1との間にフリップフロップ回路FF1aを挿入し、セレクタMUX1によりいずれか一方のフリップフロップ回路の出力データ信号を選択可能にする。フリップフロップ回路FF1に入力するクロック信号をフリップフロップ回路FF1aに入力するクロック信号よりも遅らせる。

(もっと読む)

1 - 20 / 38

[ Back to top ]