Fターム[5J079FA02]の内容

電気機械共振器を用いた発振回路 (23,106) | 回路素子 (3,033) | 半導体素子 (1,687) | バイポーラトランジスタ (227)

Fターム[5J079FA02]の下位に属するFターム

構造や閾値 (4)

Fターム[5J079FA02]に分類される特許

21 - 40 / 223

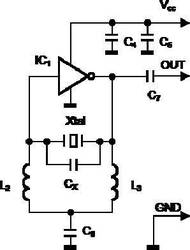

圧電振動回路

【課題】

インバーターを用いて大きな負性抵抗を得、さらに広い発振周波数可変幅を得る圧電発振回路を提供する。及び、大きな負性抵抗を得ることができることを論理的に証明する。

【解決手段】

圧電振動回路として、インバーターの入出力間にコンデンサーと圧電振動子を並列接続した回路と、第1のコイル、第2のコイルを直列接続した回路を備え、第1のコイル、第2のコイルの接続点と回路の接地点間にパスコンデンサーを備え、接続点と接地点間を交流に対して短絡させ、さらに電源と接地間にはコンデンサーを挿入し、交流に対して短絡させ、前記インバーターの電源端子と接地端子間に電圧を印加し、発振回路として構成した。

(もっと読む)

発振回路および圧電振動デバイス

【課題】部品点数を増やさず、また、電力を上げずに、複数の周波数を切り替え制御する。

【解決手段】発振回路1は、2つの水晶振動子X1,X2を接続させて2つの周波数に対応するものであり、増幅素子である発振用トランジスタQと、発振用トランジスタQに接続された容量部とが設けられている。容量部には、容量を可変させる可変容量素子であるバリキャップダイオードC12が含まれ、バリキャップダイオードC12の容量に基づいて、発振させる水晶振動子X1,X2を切替制御する。

(もっと読む)

発振回路及び霧化装置

【課題】 昇圧電源回路を要することなく電源電圧の2倍以上の振幅を持った発振信号を得ることができ、かつ、コストをより低減することが可能な発振回路を提供する。

【解決手段】 発振回路1は、入力される信号を増幅する増幅部10と、増幅された信号を昇圧する昇圧部20と、該昇圧部20から出力される信号を増幅部10の入力に帰還させる帰還部30とを備える。増幅部10は、トランジスタQ1を用いたエミッタ接地型増幅回路である。昇圧部20は、一端が電源Vccに接続される第1コイルL1、及び、一端が該第1コイルL1の他端に接続され、他端がトランジスタQ1のエミッタに接続される第2コイルL2を有する。帰還部30は、第1コイルL1と第2コイルL2との接続部に一端が接続されるとともに、他端が圧電振動子40を介してトランジスタQ1のベースに接続され、信号の位相を90°遅らせて帰還させる。

(もっと読む)

発振回路、アクティブタグ及び発振出力制御方法

【課題】出力特性の変化を抑制でき、構成を簡略化できる発振回路、アクティブタグ及び発振出力制御方法を提供すること。

【解決手段】交流電流を出力する発振回路3であって、電源部と、エミッタQ3、ベースQ2及びコレクタQ1を有し、コレクタQ1に電源部からの直流電圧が印加されるトランジスターQと、コレクタQ1に接続され、前記交流電流が出力される出力端子Tと、エミッタQ3から出力されるエミッタ電圧を測定する電圧測定手段(A/Dコンバーター)53と、電圧測定手段53によるエミッタ電圧の測定結果に基づいて、エミッタ電圧が一定となるように、ベースQ2に印加されるベース電圧を制御する電圧制御手段(CPU)6とを有する。

(もっと読む)

コルピッツ型発振回路

【課題】圧電振動子を励振するドライブレベルの周囲温度変化に対する変動を抑圧したコルピッツ型発振回路を提供する。

【解決手段】発振用トランジスタTR1のベースと接地間に負荷容量の一部となるコンデンサC1とコンデンサC2との直列回路を接続し、この直列回路の接続中点と発振用トランジスタTR1のエミッタとを接続し、更に、エミッタと接地との間にエミッタ抵抗R1を接続する。そして、エミッタ抵抗R1に並列に抵抗R2とサーミスタTH1の直列回路を接続している。発振用トランジスタTR1のベースに抵抗R3及び抵抗R4とからなるベースバイアス回路を接続すると共に、発振用トランジスタTR1のベース−接地間に圧電振動子X1を接続するようにした。

(もっと読む)

電圧制御型圧電発振器

【課題】ECL出力回路を有する電圧制御型圧電発振器の周波数温度特性を改善する手段

を得る。

【解決手段】圧電振動子Y1と、発振回路11と、周波数電圧制御回路12と、発振回路

11の出力に接続されるECL出力回路13と、各要素を搭載する絶縁基板5と、絶縁基

板5を収容するケースと、を備えた電圧制御型圧電発振器である。圧電振動子Y1は、水

晶のX軸(電気軸)の回りにθ回転し、更にZ’軸(光学軸)の回りにφ回転した二回回

転カット水晶振動子である。発振回路11は、コルピッツ型発振回路、又はピアース型発

振回路であり、周波数電圧制御回路12は、容量素子とインダクタと少なくとも1つの可

変容量素子とを有する回路からなる。ECL出力回路13は、発振回路11の出力をデジ

タル出力に変換して出力するECL回路を有し、圧電振動子Y1とECL出力回路13と

を絶縁基板5上に近接配置して電圧制御型圧電発振器を構成する。

(もっと読む)

電圧制御型圧電発振器

【課題】ECL出力回路を備えて電圧制御型圧電発振器の周波数温度特性を改善する手段

を得る。

【解決手段】電圧制御型圧電発振器は、圧電振動子Y1と、発振回路11と、周波数電圧

制御回路12と、圧電振動子Y1を加熱する発熱体7と、発熱体を制御する温度制御回路

8と、発振回路11の出力に接続されるECL出力回路13と、を備えた電圧制御型圧電

発振器である。圧電振動子Y1は、ATカット水晶振動子であり、ECL出力回路13は

、発振回路11の出力をデジタル出力に変換して出力するECL回路を有し、圧電振動子

Y1の温度が常温以下では発熱体7を温度制御回路8で制御して圧電振動子Y1の温度を

常温に保持し、常温以上は圧電振動子Y1の周波数温度特性を用いる電圧制御型圧電発振

器を構成する。

(もっと読む)

圧電発振器

【課題】圧電片の厚みすべり振動のオーバトーンを利用した圧電発振器において、基本波振動による電気エネルギーを抑え、位相雑音を低減できる技術を提供すること。

【解決手段】ATカットの水晶片1の一面側の電極2における励振電極部分は、厚みすべり振動方向と直交する方向(Z´軸方向)に互いに離間し、平行に短冊状に分割電極21、22として形成される。これらの端部同士は接続され、全体としてコ字型形状とする。他面側の電極3は、一面側の第1の分割電極21及び第2の分割電極22に夫々対向する位置に短冊状の励振電極部31、32が形成され、逆向きのコ字型上の電極とする。このため分割電極21、22だけが励振電極部として機能する。

(もっと読む)

基本波/オーバートーン水晶発振器

【課題】 1つの水晶振動子で基本波発振とオーバートーン発振を実現すると共に、励振電流を基本波発振とオーバートーン発振に応じて最適化できる基本波/オーバートーン水晶発振器を提供する。

【解決手段】 基本波発振又はオーバートーン発振が可能な水晶振動子1と、水晶振動子1からの励振電流を増幅して発振周波数を出力する発振回路30とを備え、発振回路30のトランジスタTr31のベースにコンデンサCfとコンデンサCoが並列接続されて、エミッタに接続され、エミッタにコンデンサC32と抵抗R32が並列接続され、切替信号によってコンデンサCfを回路に接続又は切り離すためのスイッチSW31を設け、スイッチSW31が基本波で発振させる場合にはオンとなり、オーバートーンで発振させる場合にはオフするよう動作する基本波/オーバートーン水晶発振器である。

(もっと読む)

発振器、発振装置

【課題】発振出力開始時のノイズに起因する異常発振や、電源立上時の過渡応答に起因する不要なパルスの出力を防止する為、ローパスフィルタの構成を変えて対応を可能とする発振器の提供。

【解決手段】発振手段からの発振信号の、発振開始からのパルス数が所定の閾値に達したことを発振パルスカウント回路3が検出すると、発振手段からの発振信号を選択して出力する。

(もっと読む)

発振回路

【課題】 クロック発振回路のジッタが音質に重要だとは気が付かなかったか、CMOSの発振回路のジッタ性能で十分だと思われていた。しかし、ジッタが多いと、音質的に十分でないことが判明した。そこで、高音質化のため低ジッタ化し、なおかつ高周波化、低電圧化、波形のエッジの急峻さ、波形の対称性を達成する必要性がある。

【解決手段】 CMOSよりもノイズ特性に優れるバイポーラトランジスタを使い、これをコンプリメンタリ接続にすることで、低ジッタ、高周波化、低電圧化、波形のエッジの急峻さ、高い対象性を得ることができた。

(もっと読む)

圧電発振器の製造方法、圧電発振器

【課題】圧電発振器の製造方法、及び圧電発振器を提供する。

【解決手段】圧電振動子12の発振周波数の温度特性を近似するための温度特性情報76に基づいて第1の近似式70を算出し、前記第1の近似式70と前記圧電振動子12の温度に対応する情報(検出電圧66)を用いて温度補償量80を算出可能な温度補償回路40に、発振信号58と前記温度特性情報76を出力する圧電発振器10の製造方法であって、前記圧電振動子12の温度と前記発振周波数との関係を離散的に示す離散温度特性情報74を生成し、前記離散温度特性情報74に基づいて前記第1の近似式70より高次である第2の近似式72を算出し、前記第2の近似式72から前記第1の近似式70が生成可能となる特徴点を抽出することにより前記温度特性情報76を生成することを特徴とする。

(もっと読む)

水晶発振器

【課題】 温度変動による周波数ずれを補正容易とし、選択された発振周波数で高安定な発振状態及び位相雑音を低減した水晶発振器を提供する。

【解決手段】 システム機器処理部に基準信号を提供する水晶発振器であって、3次以上のオーバトーン水晶振動子11と、水晶振動子11に接続し、発振周波数をシステム機器処理部2に出力する発振回路12と、発振回路12からの発振周波数を可変に分周するための分周比の情報を記憶するメモリ17と、発振回路12とシステム機器処理部2との間に設けられ、発振回路からの発振周波数をメモリ17からの分周比の情報に従って分周する可変分周器とを有する構成とする。

(もっと読む)

発振回路及び霧化装置

【課題】 少ない部品点数で電源電圧の2倍以上の振幅を得ることができ、かつ、回路を構成する電子部品の定数ばらつきに起因する発振周波数変動を低減することが可能な発振回路を提供する。

【解決手段】 発振回路1は、入力される信号を増幅する増幅部10と、一次側コイルL1と二次側コイルL2とを有し、増幅部10の出力端に一次側コイルL1が接続されたトランス20と、トランス20の二次側コイルL2に一端が接続されるとともに、他端が圧電振動子40を介して増幅部10の入力端に接続される帰還部30とを備える。増幅部10及び前記トランス20は特定の共振周波数を持たず、帰還部30は、トランス20の二次側コイルL2から出力される信号の内、圧電振動子40を共振させる周波数の発振信号を選択して増幅部10へ帰還させる。

(もっと読む)

圧電発振回路

【課題】 高周波領域で少ない部品数で大きな負性抵抗が得られ、安定した発振を実現できる圧電発振回路を提供する。

【解決手段】 第1のトランジスタQ1のベースに水晶振動子X1が接続され、第1のトランジスタQ1のコレクタに第2のトランジスタQ2のエミッタを接続してカスケード接続を構成し、更に第2のトランジスタQ2のコレクタから第1のトランジスタQ1のエミッタにコンデンサC3又は抵抗R7を介して帰還接続し、第2のトランジスタQ2のコレクタには電源電圧Vccが負荷抵抗R6を介して印加される圧電発振回路である。

(もっと読む)

恒温型の水晶発振器

【課題】周囲温度を精度良く検出して、安定した発振周波数を得ることができる恒温型発振器を提供する。

【解決手段】水晶振動子2、発振回路3及び温度制御回路4が一主面または両主面に配設された回路基板6と、回路基板6を収容して外底面に実装端子を有する容器本体5、10とを備え、温度制御回路4は少なくとも水晶振動子2の動作温度を検出する第1温度センサ11と、容器本体の周囲温度を検出する第2温度センサ12と、水晶振動子2を加熱する加熱抵抗16とからなり、回路基板6からリード線7が延出して実装端子に電気的に接続した恒温型の水晶発振器1において、第2温度センサ12に最も近接したリード線7である第1リード線7a及び第2温度センサ12と加熱抵抗16との間に回路基板6を厚み方向に貫通する断熱溝19が形成された構成とする。

(もっと読む)

分周回路及び半導体装置

【課題】回路動作の安定性の向上と、消費電力の低減とを両立できるようにした分周回路及び半導体装置を提供する。

【解決手段】発振回路に近い前段の側にあって高い周波数で動作するFF回路10と、発振回路から遠い後段の側にあって低い周波数で動作するFF回路10と、を備え、前段と後段の各FF回路10は、分周回路の動作時に通常、オン、オフを繰り返すFB−SOI−MOSFET11〜14、21、25をそれぞれ有し、前段の各FF回路10が有するMOSFET11〜14、21、25の閾値電圧の絶対値を│Vth1│とし、後段の各FF回路10が有するMOSFET11〜14、21、25の閾値電圧の絶対値を│Vth2│としたとき、│Vth1│<│Vth2│に設定されている。

(もっと読む)

発振回路

【課題】高周波発振であっても安定した発振を行なえる。

【解決手段】発振回路1は、圧電振動子を所定の周波数で励振させる発振回路部を備え、発振回路部の等価回路ECは、負性抵抗RLと容量性リアクタンスCLが直接接続された直列モデルで構成されている。発振回路部の一方の端子ECAにコイルLSの一方の端子が直列接続され、発振回路部の他方の端子ECBとコイルLSの他方の端子との間に抵抗RPが並列接続されている。コイルLSの他方の端子と抵抗RPの一方の端子との接続点が、圧電振動子との接続を行う一方の圧電振動子接続用端子Aとされ、抵抗RPの他方の端子と発振回路部の他方の端子ECBとの接続点が、圧電振動子との接続を行う他方の圧電振動子接続用端子Bとされている。また、抵抗RPの絶対値は、負性抵抗RLの絶対値よりも大きい。

(もっと読む)

クリスタル発振器

【課題】製造試験段階で出力周波数を調節するために、負荷容量を調節する際に、発振器コア電流を自動的に変化することによって出力信号のスイングを一定に維持する。

【解決手段】クリスタル発振器はクリスタル1とクリスタル発振器回路3とを具備する。負荷コンデンサのバンクC1からC6はそれぞれのスイッチ9から19によって回路にあるいは回路から切り換えられることができる。スイッチは制御ラインD0からD5によって制御され、トリムレジスタとして既知である6ビットレジスタによって設定される。トリムレジスタの値は出力信号の周波数に従って設定される。出力信号のスイングを打ち消すために、電流スイッチのバンクT1からT4が設けられ、抵抗R1からR4が回路にあるいは回路から切り換えることができるようにする。各抵抗R1からR4は制御ラインのそれぞれの1つによって切り換えられる。

(もっと読む)

発振回路

【課題】デューティの設計値に対して、発振信号の振幅や周波数の変化に依存したズレが生じない、デューティ調整部を有する発振回路を提供することを目的とする。

【解決手段】発振回路は、発振部からの第1の発振信号が入力され、この第1の発振信号の振幅及び周波数に依存しない立ち上がり及び立下り時間を持つ第2の発振信号を生成する第1の差動回路と、第2の発振信号が入力され、バイアス電圧源から与えられる電圧に依存したデューティを持つ第3の発振信号を生成する第2の差動回路とを有する。

(もっと読む)

21 - 40 / 223

[ Back to top ]