Fターム[4M106AA02]の内容

半導体等の試験・測定 (39,904) | 対象 (8,684) | チップ (1,932)

Fターム[4M106AA02]に分類される特許

21 - 40 / 1,932

半導体装置検査方法および半導体装置検査プログラム

【課題】半導体装置の検査する際の各種データを一時的に保存しておくためのデバイスを用いることなく、半導体装置の検査を行うことのできる半導体装置検査方法を提供する。

【解決手段】測定部12は、異なる設定条件によって、互いの測定結果データを用いることなく独立した第1の測定結果データ(例えば、第1の設定条件での検査における比較電圧VREFの測定値VR1と、温度特性を持つ出力電圧VPTATの測定値VP1等。)と、第2の測定結果データ(例えば、第2の設定条件での検査における比較電圧VREFの測定値VR2と、出力電圧VPTATの測定値VP2等。)とを得る。その後で、制御部13は、第1の測定結果データと第2の測定結果データとを用いて、予め定められた計算式によって得られた計算結果(TSD機能動作温度TP3)を、その上限値TP3H(℃)および下限値TP3L(℃)と比較することによって、デバイスの良否判定を行う。

(もっと読む)

半導体集積回路の検査方法および半導体集積回路

【課題】半導体集積回路のクロックに一定周波数のクロックのみを供給しつつ半導体集積回路の内部クロックを動的に変化させて半導体集積回路のランダム・ロジックを検査する。

【解決手段】複数の組み合わせ回路と当該複数の組み合わせ回路のスキャンテストを行うためのスキャンチェーンを構成する複数のスキャンフリップフロップとを有する半導体集積回路、の検査方法を、クロック生成装置から前記半導体集積回路に一定周波数の第1クロックを入力する入力工程と、前記半導体集積回路の内蔵する分周器が前記第1クロックを分周して第2クロックを生成する分周工程と、前記複数のスキャンフリップフロップに入力するクロックを、前記第1クロックと前記第2クロックとの間で動的に切り替えつつ前記半導体集積回路を検査する検査工程と、により構成する。

(もっと読む)

検査装置及び検査システム

【課題】汎用性を有し、高速で動作する半導体装置を検査できる検査装置を提供する。

【解決手段】検査装置は、第1貫通電極24bと、テスト信号を生成する信号生成ユニット30とを有する第1半導体基板24と、複数の接触子60を有するプローブ基板27と、第2貫通電極25bと、複数の接触子60と信号生成ユニット30との間の信号経路をプログラム可能に設定するスイッチマトリックス20eとを有する第2半導体基板と、を備え、第1半導体基板24と第2半導体基板25とは積層されており、第1貫通電極24bは、信号生成ユニット30が生成したテスト信号をスイッチマトリックス20eに伝達し、第2貫通電極25bは、スイッチマトリックス20eによって経路設定されたテスト信号を所定の接触子60に伝達し、信号生成ユニット30から、着脱自在に接続される電気的接続部を介さずに、接触子60にテスト信号が伝達される。

(もっと読む)

パワー半導体測定用コンタクトプローブ

【課題】簡単な構造で、かつ小型で精密な電気特性検査が可能なパワー半導体測定用コンタクトプローブを提供する。

【解決手段】パワー半導体測定用コンタクトプローブ1は、円筒状のスリーブ2と、スリーブ2内を摺動自在に嵌合するプランジャーコンタクト3と、プランジャーコンタクト3をパワー半導体の外部接続用端子へ向けて付勢するコイルスプリング4とを備え、プランジャーコンタクト4のコンタクト側を可動軸受け5に圧入して固定し、非コンタクト側を固定軸受け6に摺動自在に挿通し、可動軸受け5と、固定軸受け6とで、スリーブ2内にプランジャーコンタクト3を摺動自在とし、可動軸受け5と、固定軸受け6との間にコイルスプリング4をプランジャーコンタクト3に装着して配置し、コイルスプリング4を、スリーブ2、プランジャーコンタクト3、可動軸受け5、固定軸受け6に対して電気的に絶縁した。

(もっと読む)

半導体装置の不良解析方法ならびに不良解析装置および不良解析プログラム

【課題】半導体装置の不良解析技術において、解析成功率の向上や解析時間の短縮を図ることができる技術を提供する。

【解決手段】ショートしていると推測される一方の特定配線を特定(S103)し、その相手と推測される隣接配線の抽出(S104)をおこない、両配線間において電圧状態(論理状態)が異なる異電圧時間帯の算出(S107)をし、その異電圧時間帯で発生する発光現象の頻度を調査することにより、上記一方の特定配線に対して、どの隣接する配線がショートしているのかを短時間で確実に推定する。

(もっと読む)

半導体装置の製造方法

【課題】目視による外観検査を不要としながら、高精度に効率よく半導体ウエハの外観異常を検出する。

【解決手段】検査装置により、欠陥の検出感度を標準感度にして半導体ウエハの欠陥箇所を検出する。これにより、欠陥箇所F1,F2が検出される。続いて、検出感度を標準感度よりも検出感度が高い高感度に設定して、半導体ウエハの欠陥箇所を検出する。これにより、欠陥箇所F3〜F6(図中、点線で示す)が得られる。そして、標準感度にて検出された欠陥箇所と高感度にて検出された欠陥箇所とが重複している欠陥箇所において、高感度にて検出された欠陥箇所(欠陥箇所F6,F3)を欠陥箇所エリアと決定し、該欠陥箇所エリアに該当する半導体チップを不良チップとする処理を行う。

(もっと読む)

プローブカード

【課題】 各プローブの針先の挙動量の差を小さくするプローブカードを提供する。

【解決手段】半導体回路の電気的検査のために、テスタと半導体回路の複数の電極とを接続するプローブカード。テスタに接続される配線路が形成され、半導体回路の電極に対向して該電極から間隔をおいて配置される回路基板と、多数のプローブであってそれぞれが対応する配線路に接続される基端及び半導体回路の対応する電極に接続可能な針先を有し、各プローブが、半導体回路へ向けての所定の侵入角度を有するように回路基板に関して傾斜配置されかつ多段に配置された多数のプローブと、各プローブの基端と針先を含む自由端部分との間で、プローブを回路基板に保持する保持部材とを含む。少なくとも一部のプローブは、保持部材内を伸長する第1の直線部分及び該第1の直線部分に所定の角度をなして保持部内を伸長し該保持部材の外方で自由端部分に連なる第2の直線部分を備える。

(もっと読む)

光伝導素子、レンズ、テラヘルツ放射顕微鏡及びデバイスの製造方法

【課題】テラヘルツ電磁波の検出精度を向上させることができるテラヘルツ放射顕微鏡、これに用いられる、光伝導素子、レンズ及びデバイスの製造方法を提供すること。

【解決手段】光伝導素子は、基材と、電極と、膜材とを具備する。前記基材は、光源から発生したパルスレーザーが、観察対象であるデバイスに照射されることにより発生するテラヘルツ電磁波が入射する入射面を有する。前記電極は、前記基材に形成され、前記基材の入射面に入射された前記テラヘルツ電磁波を検出する。前記膜材は、前記基材の前記入射面に形成され、前記テラヘルツ電磁波を透過させ、前記パルスレーザーを反射させる。

(もっと読む)

同一箇所から分離可能なカンチレバー型プローブ

【課題】シングルアーム構成及びダブルアーム構成のカンチレバー型プローブの交換をする際に、アーム部が引き剥がし易いプローブ構造を提供する。

【解決手段】接触子12と、一方の端部に前記接触子12が取り付けられ、他方の端部が固定された板材で構成されたアーム部とから成るプローブを備え、アーム部の固定は、基板に接合された台座26に、剥離層24を介して接合されていることを特徴とするプローブカードである。剥離層24は、台座26と基板28の接合部よりも狭い面積である。また、アーム部は、スペーサを介して下側アーム16と、下側アーム16の厚さと同等かより厚い上側アーム22の2つのアームを備えたダブルアーム構造とし、台座26に剥離層24を介して接合され、下側アーム16を上側アーム22より長くしたことを特徴とするプローブカードである。

(もっと読む)

半導体試験装置および半導体試験装置のタイミング調整方法

【課題】複数の被試験デバイスに対して電源供給部から電源の供給を行って試験を行うときに、同時スイッチングノイズの影響を抑制することを目的とする。

【解決手段】本発明の半導体試験装置1は、複数のDUT3に電源を供給するデバイスパワーサプライ5を備える半導体試験装置1であって、DUT3の試験を行うピンエレクトロニクスカード2のドライバ12およびコンパレータ13とDUT3との間の伝送経路15の伝播遅延Tpdを校正するデータをタイミング校正データとして記憶するタイミング校正データ記憶部21と、DUT3を複数のグループに分割して、当該グループごとに異なる遅延量をタイミング校正データに加算する遅延量加算部25と、を備えたことを特徴としている。

(もっと読む)

プローブ装置

【課題】パワーデバイスの静特性及び動特性の双方をウエハレベルで測定することができ、特に静特性に使用される測定ラインに影響されることなく、パワーデバイスの動特性をウエハレベルで確実に測定することができるプローブ装置を提供する。

【解決手段】本発明のプローブ装置10は、複数のパワーデバイスが形成されたウエハWを載置する移動可能な載置台12と、載置台12の上方に配置された複数のプローブ14Aを有するプローブカード14と、載置台12の載置面とその外周面に形成された導体膜電極13と、導体膜電極13とテスタ17とを電気的に接続する測定ライン16と、を備え、載置台12上のパワーデバイスの電気的特性をウエハレベルで測定するプローブ装置であって、第2の測定ライン16には、導体膜電極13とテスタ17の間で測定ライン16の電路を開閉するスイッチ機構18を設けたものである。

(もっと読む)

自動化ウェハ欠陥検査システムおよびこのような検査を実行する方法

【課題】現在の手動検査プロセスを置き換える自動化検査システムおよび方法を提供すること。

【解決手段】自動化欠陥検査システム(10)が発明され、これはパターン化されたウェハ、全ウェハ、破損ウェハ、部分ウェハ、ワッフルパック、MCMなどを検査するために使用される。この検査システムは、特に、スクラッチ、ボイド、腐食およびブリッジング、などの金属化欠陥、ならびに拡散欠陥、被覆保護層欠陥、書きこみ欠陥、ガラス絶縁欠陥、切込みからのチップおよびクラック、半田隆起欠陥、ボンドパッド領域欠陥、などの欠陥のための第二の光学的ウェハ検査のために意図され、そして設計される。

(もっと読む)

半導体チップテスト方法、半導体チップテスト装置

【課題】高い信頼性を有する半導体チップテスト方法及び半導体チップテスト装置を提供する。

【解決手段】(a)所定の関連を有する所定枚数の半導体ウェハ上に形成された各半導体チップについて、ウェハ状態またはチップ状態でその電気的特性を検査し、良否判定する工程と、(b)前記所定枚数の半導体ウェハ上の前記半導体チップの前記判定結果から、前記判定結果がNGである前記半導体チップの割合を、前記半導体チップの前記半導体ウェハ上の位置を示すウェハアドレス毎に不良率として算出する工程と、(c)前記不良率が閾値以上と算出された前記ウェハアドレスに係る前記半導体チップについて、前記判定結果が良の場合に当該判定結果を否に更新する工程とを備える半導体チップテスト方法及び装置。

(もっと読む)

検査用プローブ及びその製造方法

【課題】被検査体の電極への影響を抑えつつ効率的に被検査体の検査を行うことができる低コストの検査用プローブ及びその製造方法を提供する。

【解決手段】絶縁性の基板12と、基板12の縁部から外に延在されて並列に配置された弾性を有する複数の導電性の接触子13と、基板12に形成されて接触子13と導通する配線パターン14とを備え、被検査体の検査を行う際に接触子13の先端からなる接点15が被検査体の電極に接触される検査用プローブ11であって、接触子13及び配線パターン14が、MEMS技術によって基板12に形成され、接触子13の接点15における電極との接触箇所に、凸曲面状に突出する電極接触凸部16が形成されている。

(もっと読む)

半導体検査装置、および半導体検査方法

【課題】本発明は、テストパターンを長く複雑なパターンにする必要がなく、スクリーニングで検出することができる回路パターンの不具合の割合を増やすことができる半導体検査装置、および半導体検査方法を提供する。

【解決手段】本発明は、半導体基板に形成した複数の半導体チップに対してスクリーニングを行なう半導体検査装置10である。半導体検査装置10は、ステージ2と、プローブ4と、テスタ部8と、光検出部5と、発光解析部6と、主制御部7と、異常判定部9とを備えている。光検出部5は、光学的なスクリーニングを行なうために、回路パターンに印加した電気信号に基づく発光を、半導体基板の他方の面側から検出する。異常判定部9は、テスタ部8で検出した出力信号に基づき、回路パターンの不具合を判断し、発光解析部6で解析した発光に基づき、回路パターンの不具合を判断して、半導体チップの異常を判定する。

(もっと読む)

プローブカード、半導体装置、半導体装置の試験方法、及び、半導体装置の製造方法

【課題】差動伝送方式を採用した半導体装置の試験で行われるTDRタイミング測定の校正精度の低減を抑制すること。

【解決手段】複数のプローブ針を有し、プローブ針を半導体装置の電極パッドと接続させて所定の試験を行うためのプローブカードであって、互いに異なる電極パッドP1及びP2に接続するよう配置され、対となっている差動信号入力用の第1及び第2のプローブ針1a及び2aと、互いに異なる電極パッドP1及びP2に接続するよう配置された第3及び第4のプローブ針1b乃至2b´と、第3及び第4のプローブ針1b乃至2b´各々と接続して、第3及び第4のプローブ針1b乃至2b´を導通させる配線3及び抵抗部材RTと、を有し、第3及び第4のプローブ針1b乃至2b´、配線3及び抵抗部材RTは電気的にフローティングな状態となっている。

(もっと読む)

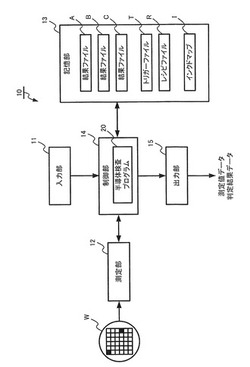

スクリーニング方法、スクリーニング装置およびプログラム

【課題】半導体装置の特性がウエハ上の位置に応じて変動する場合においても、半導体装置の不良品を高い精度で検出できるようにすること。

【解決手段】スクリーニング方法は、ウエハに含まれる複数の半導体装置のそれぞれの電気的特性値を測定する工程と、前記ウエハ上における前記複数の半導体装置のそれぞれの位置情報を取得する工程と、前記複数の半導体装置の電気的特性値の変動のうちの前記ウエハ面上で相対的に緩やかに変動する成分を、前記複数の半導体装置のそれぞれの電気的特性値から差し引いて、前記複数の半導体装置のそれぞれの電気的特性値を補正する工程と、前記補正後の電気的特性値の分布を前記複数の半導体装置に対して生成する工程と、前記分布に基づいて、前記補正後の電気的特性値が外れ値となる半導体装置を前記複数の半導体装置の中から検出する工程と、を含む。

(もっと読む)

接続端子及び接続治具

【課題】円筒形状部が抵抗溶接による固定の前後においてほぼ円形形状を維持している接続端子を提供する。

【解決手段】対象点間を接続する接続治具に用いられる接続端子は、小径の導電部とそれを囲むように配置された大径の円筒形状部とを備え、小径の導電部の先端部が、大径の円筒形状部の先端部から突出し、小径の導電部の一部が、大径の円筒形状部の一部に接合されており、小径の導電部に接合された大径の円筒形状部の部分を少なくとも含む円筒形状部の軸線の周りの帯状部分の一部に切欠き部が形成されている。

(もっと読む)

試験器インタフェース接触要素及び支持ハードウエアを清浄化するための器具、装置、及び方法

【課題】試験器インタフェース接触要素及び支持ハードウエアを清浄化するための装置を提供する。

【解決手段】試験される半導体ウェーハ、個別化IC装置、又はパッケージ化IC装置にウェーハ探針器又はパッケージ装置ハンドラ内に清浄化媒体20を装着する段階を含み、清浄化媒体は、研磨性、粘着性、硬度のような所定の特性を有し、接触要素及びサポート構造体を清浄化する上面を有する。接触要素を清浄化媒体に接触させる段階を更に含み、それによってウェーハ探針器又はパッケージ装置ハンドラの通常の作動中にプローブ要素からあらゆるデブリが除去される。

(もっと読む)

シュリンク前形状推定方法およびCD−SEM装置

【課題】 電子線照射によってシュリンクするレジストをCD−SEMで測長する際に、シュリンク前の形状や寸法を高精度に推定する。

【解決手段】 あらかじめ様々なパターンについて、電子線照射前断面形状データと、様々な電子線照射条件で得られる断面形状データ群やCD−SEM画像データ群と、それらに基づくモデルを含むシュリンクデータベースを準備し、被測定レジストパターンのCD−SEM画像を取得し(S102)、CD−SEM画像とシュリンクデータベースとを照合し(S103)、被測定パターンのシュリンク前の形状や寸法を推定し、出力する(S104)。

(もっと読む)

21 - 40 / 1,932

[ Back to top ]