Fターム[5F004DB02]の内容

半導体のドライエッチング (64,834) | 被エッチング物 (6,778) | Si (1,365) | 多結晶Si (435)

Fターム[5F004DB02]に分類される特許

21 - 40 / 435

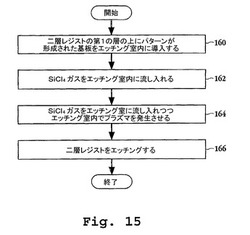

二層レジストプラズマエッチングの方法

【課題】プラズマエッチング室内において、基板の上に形成された二層レジストをエッチングするための方法を提供する。

【解決手段】二層レジストの第1の層の上にパターンを形成された基板をエッチング室に導入する工程から開始される。次いで、SiCl4ガスがエッチング室に流し込まれる。次に、SiCl4ガスを流し入れつつエッチング室内においてプラズマを発生させる。次いで、二層レジストがエッチングされる。

(もっと読む)

プラズマ処理装置

【課題】 プラズマ処理の特性を多様に変化させることができるプラズマ処理装置を提供する。

【解決手段】

このプラズマ処理装置は、マイクロ波のエネルギーを、処理容器2の上部に配置された誘電体窓16を介して処理容器2内に供給して、ガス供給源100から処理容器2内に供給した処理ガスをプラズマ化して、処理容器2の下部に配置された基板Wをプラズマ処理するプラズマ処理装置であって、ガス供給源100から供給される処理ガスを、誘電体窓16からの距離が異なる位置に導入する少なくとも第1及び第2のガス導入部を備えている。

(もっと読む)

アンテナ、誘電体窓、プラズマ処理装置及びプラズマ処理方法

【課題】基板表面処理量の面内均一性も改善することができるアンテナ、誘電体窓、プラズマ処理装置及びプラズマ処理方法を提供する。

【解決手段】アンテナは、誘電体窓と、前記誘電体窓の一方面に設けられたスロット板とを備えている。前記誘電体窓の他方面は、環状の第1凹部147に囲まれた平坦面146と、平坦面146の重心位置を囲むように、平坦面146内に形成された複数の第2凹部153とを有している。前記スロット板の主表面に垂直な方向からみた場合、前記スロット板におけるそれぞれのスロット133内に、それぞれの第2凹部153の重心位置が重なって位置している。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】不純物領域の自己整合的な形成を精度よく行うことができる、炭化珪素半導体装置の製造方法を提供する。

【解決手段】マスク層31の開口部OPを介して炭化珪素基板90上に第1導電型不純物が注入される。第1および第2の材料のそれぞれから作られた第1および第2の膜32、33が成膜される。異方性エッチング中に第1の材料のエッチングが生じたことが検知され、異方性エッチングが停止される。第1および第2の膜32、33によって狭められた開口部OPを介して、炭化珪素基板90上に第2導電型不純物が注入される。

(もっと読む)

半導体装置の作製方法

【課題】チャネル形成領域が形成される半導体層のチャネル形成領域と逆側近傍の加工方法を工夫した半導体装置の作製方法を提供する。

【解決手段】少なくとも結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、少なくとも第1のエッチングと第2のエッチングを行い、第1のエッチングは非晶質半導体膜の一部を残存させつつ行い、第2のエッチングは非晶質半導体膜上の被覆膜を除去させた後に、非晶質半導体膜に対するエッチングレートが高く、且つ結晶性半導体膜に対するエッチングレートが低い条件により行い、積層半導体膜に設けられた結晶性半導体膜の一部を露出させる。

(もっと読む)

半導体装置の製造方法及半導体製造装置

【課題】 エッチングの終点を精度良く制御する。

【解決手段】エッチング装置1は、処理ユニット2と制御ユニット3とを有する。処理ユニット内のプラズマの発光強度は、OES検出器21で取得され、エッチング制御装置31が非線形回帰分析して回帰式を決定する。非線形回帰分析は、プラズマの発光強度がピークを超えた第1の時間までに取得したプラズマの発光強度を用いて行われ、回帰式を用いてエッチング終点となる第2の時間が算出される。エッチング終点は、第1の時間から発光強度が所定値だけ減少する時間として算出される。エッチング装置1は、エッチング終点に達したら、エッチングを終了する。

(もっと読む)

テクスチャ形成面を有するシリコン基板、およびその製造方法

【課題】精密なテクスチャを有するテクスチャ形成面を有するシリコン基板を提供することを目的とする。

【解決手段】テクスチャ形成面を有するシリコン基板において、前記テクスチャ形成面には、複数の第一の凹凸と、前記第一の凹凸のそれぞれに形成された複数の第二の凹凸とが形成されており、前記第一の凹凸の頂点同士の間隔は3〜20μmであるシリコン基板を提供する。このようなシリコン基板は、好ましくは、前記シリコン基板の表面に複数の第一の凹凸を形成し;前記複数の第一の凹凸を形成されたシリコン基板の表面にエッチングガスを吹き付けて、前記第一の凹凸のそれぞれに、複数の第二の凹凸を形成して製造される。ここで、前記エッチングガスには、ClF3,XeF2,BrF3,BrF5およびNF3からなる群から選ばれる一以上のガスが含まれる。

(もっと読む)

シリコン含有物のエッチング方法

【課題】被処理物が有機物にて汚染されている場合でも、シリコン含有物を効率良くエッチングする。

【解決手段】原料ガスを大気圧近傍のプラズマ空間23に導入してエッチングガスを生成する(生成工程)。エッチングガスを、温度を10℃〜50℃とした被処理物90に接触させる(エッチング反応工程)。原料ガスは、フッ素含有成分と、水(H2O)と、窒素(N2)と、酸素(O2)と、キャリアガスを含む。原料ガス中の窒素と酸素とキャリアガスの合計体積流量(A)とフッ素含有成分の体積流量(B)との比は、(A):(B)=97:3〜60:40である。原料ガス中の窒素と酸素の合計体積流量は、窒素と酸素とキャリアガスの合計体積流量の2分の1以下である。窒素と酸素の体積流量比は、N2:O2=1:4〜4:1である。

(もっと読む)

半導体素子の形成方法

【課題】相互接続領域の具現が困難なパッドレイアウトを具現化し、オーバレイマージンを増大できる半導体素子の形成方法を提供する。

【解決手段】半導体基板に被食刻層、第1のハードマスク物質層、第1の分割パターン物質層及び第2のハードマスク物質層を形成して選択食刻し第2のハードマスクパターンを形成し、これをマスクとし第1の分割パターン物質層を食刻し第1の分割パターンを形成する。第1のハードマスク物質層の上部にスペーサ物質層及び第2の分割パターン物質層を形成し、第1の分割パターンが現われるまでスペーサ物質層及び第2の分割パターン物質層を部分食刻しスペーサ物質層を露出させ、複数の第1の分割パターン間に第2の分割パターンを形成し、第1、第2の分割パターンをマスクとしスペーサ物質層及び第1のハードマスク物質層を食刻し第1のハードマスクパターンを形成し、これをマスクとし被食刻層を食刻し微細パターンを形成する。

(もっと読む)

プラズマ処理装置

【課題】処理ガスをプラズマ生成空間及び吹出路に通して吹出し、被処理物を表面処理する際、吹出路からの電界の漏洩を防止する。

【解決手段】プラズマ生成部10の一対の電極11,12を対向方向に対向させ、これらの間にプラズマ生成空間19を形成する。ノズル部20を電気的に接地された金属製の角材21,22にて構成し、これをプラズマ生成部10の処理位置Pを向く面に配置する。連結部材31,32にてノズル部20をプラズマ生成部10に連結して支持する。吹出路29の吹出方向の長さをノズル部20の吹出路29を画成する面から上記対向方向の外側面までの寸法より大きくか略等しくする。

(もっと読む)

プラズマ処理方法およびプラズマ処理装置

【課題】段差を有する膜構造を高精度にエッチングするプラズマ処理装置またはドライエッチング方法を提供する。

【解決手段】真空容器107と、この真空容器内部の処理室内に配置されその上面にエッチング対象のウェハ112が載せられる下部電極113と、下部電極113にバイアス電位を形成するための高周波電力を供給するバイアス印加装置118,120と、前記処理室内に反応性ガスを導入するガス供給手段111と、前記処理室内にプラズマを生成するための電界を供給する電界供給手段101〜103と、前記高周波電力により前記ウェハ112に入射する前記プラズマ中のイオンのエネルギーの分布を調節する調節装置127とを備えたプラズマ処理装置。

(もっと読む)

半導体装置の製造方法、製造システムおよび調整装置

【課題】製品の歩留まりを向上させることができる半導体装置の製造方法、製造システムおよび調整装置を提供すること。

【解決手段】実施形態にかかる半導体装置の製造方法は、成膜工程と、加工工程と、イオン注入工程と、アニール工程と、調整工程とを含む。成膜工程では、基板上に半導体の薄膜を成膜する。加工工程では、薄膜を所定の形状に加工する。イオン注入工程では、所定の形状に加工された薄膜に対してイオン注入処理を行う。アニール工程では、イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成する。調整工程では、成膜工程における薄膜の成膜条件および成膜結果と加工工程における薄膜の加工結果とのうち、少なくともいずれか1つに基づき、イオン注入工程におけるイオン注入処理の処理条件およびアニール工程におけるアニール処理の処理条件の双方または一方を調整する。

(もっと読む)

半導体装置の製造方法

【課題】エッチング加工により高アスペクト比の構造体の形成が可能な半導体装置の製造方法を提供すること。

【解決手段】異なる材料からなる複数の膜を積層して少なくとも酸化シリコン膜を含む積層膜を形成する工程と、前記積層膜上にハードマスクパターンを形成する工程と、前記ハードマスクパターンをエッチングマスクに用いて前記積層膜を異方性エッチングして所定の形状の積層膜パターンを形成する工程と、前記ハードマスクパターンを除去する工程と、を含み、前記ハードマスクパターンは、第1ハードマスク層と第2ハードマスク層とが少なくとも1層ずつ以上積層されて構成され、前記第1ハードマスク層は、前記第2ハードマスク層よりもウェットエッチングによる剥離性が良い材料からなり、前記積層膜の直上には前記第1ハードマスク層が配置される。

(もっと読む)

流体制御装置およびこれを用いたガス処理装置

【課題】 ラインの増設・変更に容易に対応できる集積化流体制御装置およびこのような流体制御装置を備えたガス処理装置を提供する。

【解決手段】 流体制御装置は、各ラインA1,A2,A3,A4,A5,B1,B2,B3が複数のブラケット8,9,18,19,20を介して基板1に着脱可能に取り付けられ、通路接続手段47,48が上方に取り外し可能とされている。複数の継手部材11,12,13,14,15,16,17として、複数の管状継手部材13,15,17と複数のブロック状継手部材11,12,14,16とが使用されている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置の製造方法及びコンピュータ記録媒体

【課題】効率良く多段の良好な形状の階段状の構造を形成することのできる半導体装置の製造方法及びコンピュータ記録媒体を提供する。

【解決手段】第1の誘電率の第1の膜と、第1の誘電率とは異なる第2の誘電率の第2の膜とが交互に積層された多層膜と、多層膜の上層に位置しエッチングマスクとして機能するフォトレジスト層とを有する基板をエッチングして、階段状の構造を形成する半導体装置の製造方法であって、フォトレジスト層をマスクとして第1の膜をプラズマエッチングする第1工程と、水素含有プラズマにフォトレジスト層を晒す第2工程と、フォトレジスト層をトリミングする第3工程と、第3工程によってトリミングしたフォトレジスト層及び第1工程でプラズマエッチングした第1の膜をマスクとして第2の膜をエッチングする第4工程とを有し、第1工程乃至第4工程を繰り返して行うことにより、多層膜を階段状の構造とする。

(もっと読む)

エッチング方法、エッチング装置およびコンピュータ読み取り可能な記憶媒体

【課題】 多層構造体中にあるシリコン膜であっても、レジスト膜や有機膜をマスクに用いてエッチングすることが可能であり、かつ、シリコン膜、及びこのシリコン膜の下に存在するシリコン酸化物膜を一括してエッチングすることも可能なエッチング方法を提供すること。

【解決手段】 シリコン酸化物膜2、及びこのシリコン酸化物膜2上に形成されたシリコン膜3を含む多層構造体をエッチングするエッチング方法であって、多層構造体中のシリコン膜3及びシリコン酸化物膜2をエッチングするとき、レジスト膜6又は有機膜をエッチングのマスクに用い、エッチングガスとしてCH2F2ガスを含むエッチングガスを用いて、多層構造体中のシリコン膜3及びシリコン酸化物膜2を一括してエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】ウエハ処理後のパターンの出来映え形状を高精度で予測することのできる技術を提供する。

【解決手段】各反応生成物の量をそれぞれプラズマ発光強度によって表し、これらを規格化する。そして、規格化された各反応生成物のプラズマ発光強度をそれぞれ予測値補正データに変換し、これら予測値補正データのなかから開口率に応じた最適な予測値補正データを選択し、この最適な予測値補正データを、モニタリング信号から得られた予測値データに加えることにより、パターンの出来映え形状を予測する。

(もっと読む)

半導体装置の製造方法

【課題】所望の微細化パターンを高精度かつ効率良く形成することができ、生産効率を向上させることのできる半導体装置の製造方法を提供する。

【解決手段】トリミングされたフォトレジスト層104のラインパターンの上に第1の膜105を成膜する工程と、前記ラインパターンの側壁部以外にある第1の膜105およびフォトレジスト層104を除去する工程と、該除去後に残った部分の第1の膜105をマスクとして反射防止膜103とコア層102をエッチングし、コア層102をラインパターンとする工程と、ラインパターン化コア層102の上に第2の膜106を成膜する工程と、ラインパターン化コア層102の側壁部以外にある第2の膜106およびラインパターン化コア層102を除去する工程と、該除去後に残った部分の第2の膜106をマスクとして被エッチング層101をエッチングし、ラインパターンとする工程とを備えた製造方法とする。

(もっと読む)

基板処理方法及び記憶媒体

【課題】エッチングレートを低下させることなくアスペクト比の高いホール等をシリコン層に形成することができる基板処理方法を提供する。

【解決手段】ウエハ上のポリシリコン層38が臭化水素ガス、酸素ガス及び三弗化窒素ガスを含む処理ガスから生成されたプラズマ中の臭素陽イオン45aや臭素ラジカル45bでエッチングされ、次いで、該エッチング中に生成された臭化珪素系デポ物44が酸素ガス及び窒素ガスを含む処理ガスから生成されたプラズマ中の酸素ラジカル46や窒素ラジカル47で酸化処理されて酸化珪素に変成し、該酸化珪素がアルゴンガス及び三弗化窒素ガスを含む処理ガスから生成されたプラズマ中のフッ素陽イオン48aやフッ素ラジカル48bで引き続きエッチングされることによって、ホール43のエッチングレート低下が防止される。

(もっと読む)

21 - 40 / 435

[ Back to top ]