Fターム[5F033LL09]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 組成比 (303)

Fターム[5F033LL09]の下位に属するFターム

シリサイド、化合物の組成が理論比と異なる (12)

Fターム[5F033LL09]に分類される特許

61 - 80 / 291

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】基板側から順に、Al合金膜と、当該Al合金膜と直接接続する薄膜トランジスタの酸化物半導体層と、を有し、TiやMoなどの高融点金属を省略してAl合金膜を酸化物半導体層と直接接続しても低コンタクト抵抗を実現できる新規な表示装置用Al合金膜を有する配線構造を提供する。

【解決手段】上記配線構造において、半導体層は酸化物半導体からなり、Al合金膜は、Niおよび/またはCoを含むものである。

(もっと読む)

半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲット

【課題】 バリア膜形成による配線の抵抗値増大及びボイドの発生を防ぐことができる半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲットを提供すること。

【解決手段】 Si酸化物を含む絶縁膜1にCuの配線が設けられている半導体装置であって、絶縁膜1に設けられた溝状の開口部1aの内面に形成されたバリア膜4と、開口部1a内であってバリア膜4上に形成されたCuからなる配線本体2と、を備え、バリア膜4が、バリア膜4が、少なくとも絶縁膜1上に形成されたCa酸化物を含有するCu合金下地層4aを有し、該Cu合金下地層4aと絶縁膜1との界面にCaSi酸化物が偏析している。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

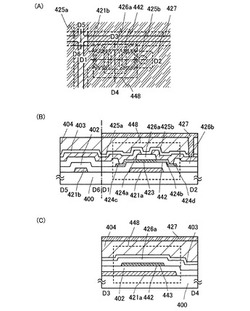

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたGe:0.3原子%〜1.2原子%、Co:0.05原子%〜2.0原子%、Laおよび/またはNd:0.1原子%〜0.5 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

反射電極、および反射電極を備えた表示デバイス

【課題】高い反射率および低い接触抵抗を有しており、しかも、ヒロックなどの欠陥を生じることのない耐熱性にも優れた反射電極を提供する。

【解決手段】基板1上に形成される表示デバイス用の反射電極2であって、前記反射電極は、0.05〜2原子%のNi及び/又はCo、並びに0.1〜2原子%のNdを含有する第1のAl−(Ni/Co)−Nd合金層2aとAlとO(酸素)を含有する第2のAl酸化物層2bと、を有している。上記Al酸化物層は透明画素電極3と直接接続しており、前記Al酸化物層中のO原子数とAl原子数との比である[O]/[Al]が、0.30以下であり、前記Al酸化物層の最も薄い部分の厚みが、10nm以下である。上記反射電極は、前記Al酸化物層と前記透明画素電極とが直接接続する領域において、前記透明画素電極と前記基板との間に形成されている。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたGe:0.3〜1.2原子%、Ni:0.1〜1.0原子%未満、Laおよび/またはNd:0.1原子%〜1.0 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

表示装置用Al合金膜、表示装置およびAl合金スパッタリングターゲット

【課題】バリアメタル層を省略して透明画素電極と直接接続させた場合にも低コンタクト抵抗を示し、且つ、表示装置の製造過程における現像液耐食性や剥離液耐食性も高められた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、Al合金膜は、グループAに属するNiおよび/またはCoの元素を0.5原子%以下(0原子%を含まない。)と、Geを0.2〜2.0原子%と、グループBに属するYおよび/またはZrの元素を3原子%以下(0原子%を含まない。)とを含有する。

(もっと読む)

配線形成方法

【課題】樹脂基板上に、接着層等を形成するための別の工程を加えることなく、基板との密着性の高い導電性配線を簡単に形成することができる配線形成方法を提供することを目的とする。

【解決手段】樹脂基板1上に、導電性微粒子を含有する分散溶液の塗布層3を形成する工程と、レーザ光6を塗布層3の特定領域に連続的に照射していくことで、導電性微細配線4を形成する工程と、導電性微細配線4以外の領域の材料を除去する工程とを備え、塗布層3の厚さをd、塗布層3の光吸収係数をα、レーザ光6の入射光強度をI0、樹脂基板1上に到達するレーザ光6の透過光強度をI1とするとき、以下の関係式から成り立つことを特徴とする。

log(I1/I0)=−αd

(もっと読む)

配線構造及びその形成方法

【課題】良質な配線構造、及びその形成方法を提供する。

【解決手段】第1の導電材及び第1の絶縁層を有する第1の配線層と、前記第1の絶縁層上の第2の配線層とを備え、前記第2の配線層は第2の絶縁層と、ヴィア及びトレンチを有する開口部とを有し、前記開口部は、第2の導電材と、前記第2の導電材と、前記第2の絶縁層との間の2層以上のバリア層とを有し、前記第2の導電材は、前記第1の導電材と電気的に接続され、前記2層以上のバリア層は、前記開口内の前記第2の絶縁層と第1のバリア層とが接触し、且つ前記第1のバリア層とMnOx含有バリア層とが接触する領域と、前記第2の絶縁層と前記MnOx含有バリア層が接触する領域とを有する。

(もっと読む)

配線層構造及びその製造方法

【課題】半導体基板又はガラス基板の下地基板に対する密着性が高く、下地基板への拡散バリア性に優れ、かつ水素プラズマ耐性に優れた低抵抗な配線層構造、及びその製造方法を提供する。

【解決手段】半導体又はガラス基板の下地基板1と、下地基板1上に形成された酸素含有Cu合金層2と、酸素含有Cu合金層2上に形成された、Al、Zr、Tiのうち少なくとも一種を含有する酸化物層3と、酸化物層3上に形成された、Al、Zr、Tiのうち少なくとも一種を含有するCu合金層4と、Cu合金層4上に形成された、Cu導電層5とを有する。

(もっと読む)

アモルファスなタンタル−イリジウム拡散バリアを用いた銅相互接続構造、その形成方法、および該方法による半導体デバイス製造方法

【課題】ライナ/銅界面のボイド生成部位の排除により、高い信頼性および生産歩留まりが得られる半導体デバイス製造方法を提供する。

【解決手段】半導体デバイス製造に用いる拡散バリアを形成する方法は、物理蒸着(PVD)工程によって、パターン形成された中間誘電体(ILD)層の上に、イリジウム・ドープされたタンタル・ベースのバリア層を堆積するステップを含み、該バリア層は、原子量で少なくとも60%のイリジウム濃度で、バリア層が結果としてアモルファス構造を有するように堆積される。

(もっと読む)

配線部材、その製造方法及びそれを用いた電子部品

【課題】600℃〜700℃の高温であっても高い耐酸化性と低抵抗を両立し、かつ低コストで形成可能な配線材料を提供する。

【解決手段】基板上に形成される銅配線と、銅配線上に50nm以上200nm以下の膜厚で形成される50重量%以上のアルミニウムを含有する銅合金薄膜と、を具備する配線部材を用いる。上記銅配線の膜厚は、1μm以上50μm以下である。基板と銅配線の間には下地層が配置されている。配線部材の電気抵抗率は、4×10-6Ωcm以下である。

(もっと読む)

貫通シリコンビアを有するめっき物及びその形成方法

【課題】貫通シリコンビア形成時におけるビア内側壁の銅シード層のカバレッジが良好で均一な銅配線層を有するめっき物を提供することを目的とする。

【解決手段】基材上にバリア層として形成された、タングステン及びタングステンと合金化した際に銅に対するバリア性を有する金属(A)との合金薄膜、その上に無電解置換銅めっきにより銅シード層、さらに前記無電解置換銅めっきを実施したのと同一のめっき液を用いた電気銅めっきにより銅配線層がこの順番で形成されてなる、貫通シリコンビアを有するめっき物。

(もっと読む)

電子部品素子

【課題】金属膜の酸化を防止し、さらに金属膜の酸化を防止するだけでなく、酸化防止を行うことで新たに発生した不具合(腐食)も防止する。

【解決手段】

電子部品素子1では、基板2上に少なくとも3層からなる金属膜群5が形成されている。この金属膜群5は、少なくとも、金属膜51と、金属膜51を保護する保護膜52と、金属膜51と保護膜52との電位差を無くす調整膜53とから構成されている。この電子部品素子1では、基板2上に、金属膜51、調整膜53、および保護膜52の順に積層されている。

(もっと読む)

半導体構造体及びその形成方法

【課題】 相互接続構造の信頼性及び拡張性を改善する相互接続構造のための冗長金属拡散バリア層を提供する。

【解決手段】 冗長金属拡散バリア層は、誘電体材料内に設けられた開口内に配置され、且つ開口内に存在する拡散バリア層及び導電性材料の間に配置される。冗長拡散バリア層は、Ru並びに純粋なCo若しくはN,B及びPのうちの少なくとも1つを含むCo合金からなる単層若しくは多層構造である。

(もっと読む)

現像液耐性に優れた表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理を適用した場合でも十分に低い電気抵抗を示すと共に、直接接続された透明画素電極とのコンタクト抵抗が十分に低減され、かつ現像液耐性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で透明導電膜と直接接続されるAl合金膜であって、上記Al合金膜は、グループAに属するNiおよび/またはCoの元素を2.0原子%以下(0原子%を含まない)、並びにグループBに属する少なくとも一種の元素を0.05〜2.5原子%含み、上記グループBの元素はGd、Nd、La、Y、Sc、Pr、Dy、Ce、Ho、Er、Tb、Pm、Tm、Yb、Lu、Hf、Zr、Zn、Mg、Ti、Mn、およびGeから構成されている。

(もっと読む)

スパッタリングターゲット及びこれを利用して製造される半導体素子

【課題】スパッタリングターゲット及びこれを利用して製造される半導体素子を提供する。

【解決手段】重量%で0.01%以上から1%未満のNi、及び残部としてW及びその他の不回避な不純物で構成されるスパッタリングターゲットであり、また、バリア層と、バリア層上のシード層と、シード層上の導電層と、を備え、導電層は、重量%で0.01%以上から1%未満のNi、及び残部としてW及びその他の不回避な不純物で構成される、タングステンとニッケルとの合金薄膜を備える半導体素子である。

(もっと読む)

スパッタリングターゲット及び透明導電膜及び透明導電ガラス基板

【課題】 特定の金属を含有する透明導電材料を画素電極、透明電極に使用することにより、バリヤーメタル等を堆積するための工程が不要な簡略化されたTFT(薄膜トランジスタ)基板の製造方法を提供することである。

【解決手段】 酸化インジウムを主成分とし、W、Mo、Nb、Ni、Pt、Pdからなる第1金属群M1から選ばれた1種又は2種以上の金属又はその金属の酸化物と、ランタノイド系金属からなる第2金属群M2から選ばれた1種又は2種以上の金属の酸化物と、を含むスパッタリングターゲットを利用して、透明導電膜を作製する。この透明導電膜を画素電極として利用することによって、ソース電極7等との接触抵抗を小さく抑えることができる。更に、バリヤーメタル等を用いる必要がなくなったため、バリヤーメタル等を堆積する工程をなくすことができ、TFT基板の製造工程が簡略化される。

(もっと読む)

表示装置およびこれに用いるCu合金膜

【課題】Cu系材料の特徴である低電気抵抗を維持しつつ、絶縁膜を構成するSiN膜や半導体膜におけるSiN層との密着性に優れると共に、エッチング時に良好にテーパ状にエッチングできるCu合金膜を提供する。

【解決手段】絶縁膜および/または半導体膜と直接接触する表示装置用Cu合金膜であって、該Cu合金膜は、上記SiN膜やSiN層と直接接触する第一層と、該第一層上に形成される第二層とを含み、前記第一層は、窒素を0.4原子%以上5.0原子%未満含むと共に、Ni、Al、Zn、MnおよびFeよりなる群から選択される1種以上の元素(X元素)を0.1〜0.5原子%、および/または、Ge、Hf、Nb、MoおよびWよりなる群から選択される1種以上の元素(Z元素)を0.1〜0.3原子%含み、かつ前記第一層の膜厚が2〜100nmである表示装置用Cu合金膜。

(もっと読む)

61 - 80 / 291

[ Back to top ]