Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,741 - 2,760 / 2,805

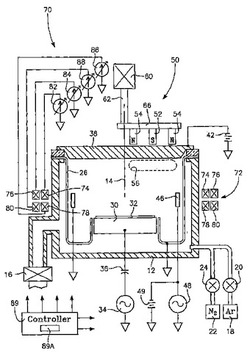

スパッタ反応装置内で金属バリアを形成するために特にマルチステッププロセスで使用される可変四重電磁石アレー

スパッタチャンバ(70)及びそれが可能にするマルチステッププロセス。チャンバ軸と同軸な四重電磁石矩形アレー(72)はチャンバ内のRFコイル(46)の裏側にあることが好ましい。異なる磁場分布を生成するために、例えば、ターゲット材料をウエハ(32)上にスパッタするためにスパッタターゲット(38)が給電されるスパッタ堆積モードとRFコイルがアルゴンスパッタリングプラズマをサポートするスパッタエッチングモードとの間でコイル電流を個別に制御できる。ターゲット材料のRFコイルにおいては、コイルにDCバイアスをかけることができ、コイルアレーがマグネトロンとしての機能を果たす。このようなプラズマスパッタチャンバ内で行なわれるマルチステッププロセスは、様々な条件下でのターゲットからのバリア材料のスパッタ堆積と、基板のアルゴンスパッタエッチングとを含んでいてもよい。ターゲット電力及びウエハバイアスの減少を伴うフラッシュステップが適用される。 (もっと読む)

付着材料を除去するための反応性流体システムおよびそれを使用するための方法

本発明は、一般に材料を処理するための方法に関する。より詳細には、本発明は反応性流体、および被覆材料、金属、非金属、層状材料、有機物、ポリマーおよび半導体材料を非限定的に含む付着材料を除去するための反応性流体の使用に関する。本発明は、半導体チップ生産のような商用プロセスに適用することが可能である。

(もっと読む)

(もっと読む)

半導体装置用のバックエンド工程伝送線路構造(バックエンド工程処理におけるサスペンデッド伝送線路構造の形成方法)

【課題】 半導体装置用のバックエンド工程伝送線路構造を提供する。

【解決手段】 半導体装置用の伝送線路構造(300)を形成する方法は、第1のメタライゼーション層上に層間絶縁膜を形成するステップと、前記層間絶縁膜の一部を除去するステップと、前記層間絶縁膜の一部の除去により生じた一つ以上のボイド(308)内に犠牲材を形成するステップとを含む。前記層間絶縁膜上に形成された第2のメタリゼーション層中に信号伝送線路(302)が形成され、該信号伝送線路(302)は前記犠牲材上に設けられている。前記第2のメタリゼーション層中に含まれる誘電体の一部が除去されて前記犠牲材が露出され、このとき該犠牲材の一部は前記信号伝送線路(302)を貫通して形成された複数のアクセスホール(310)を介して露出される。前記犠牲材は除去され、それにより前記信号伝送線路(302)の下部にエアギャップが形成される。

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

感光性誘電体層を分解することによる相互接続構造の形成

本発明は、感光性材料の層が直接にパターン化される方法を提供する。その後、感光性材料は、少なくとも部分的に分解され、層内にボイドまたは空隙を残し、低減された抵抗キャパシタンス遅延特性を有する低誘電率の層を提供する。  (もっと読む)

(もっと読む)

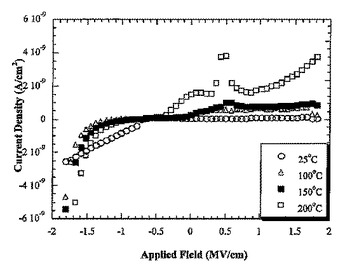

低κ誘電体付与のためのシロキサンエポキシポリマー

低κ誘電性フィルムとしてシロキサンエポキシポリマーを用いる半導体デバイスを開示する。前記デバイスは、半導体基板、1種以上の金属層又は構造及び1種以上の誘電性フィルムを含み、そこでデバイス中の少なくとも1種の誘電性フィルムがシロキサンエポキシポリマーである。シロキサンエポキシポリマーの使用は有利である。理由の一つは、ポリマーがよく金属に接着し、1.8という低い誘電定数を有するためである。従って、開示した半導体デバイスは、従来の誘電体材料を用いて製造したデバイスよりもはるかに良好な性能を提供する。更に、シロキサンエポキシポリマー誘電体は低温で十分に硬化可能であり、低い漏洩電流を示し、400℃を超える温度で安定した状態を保つ。そのことが前記誘電体の半導体産業での使用を特に魅力的にする。  (もっと読む)

(もっと読む)

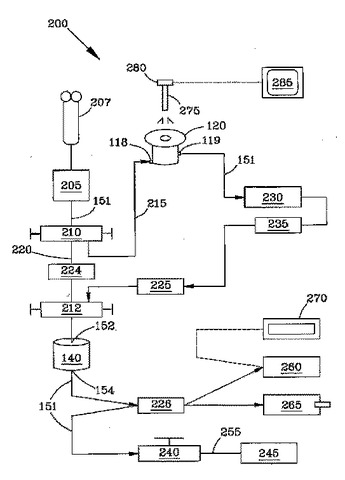

イオン化物理蒸着方法

iPVDシステム(200)は、真空チャンバー(30)内で突出部(14)を最小化または除去しながら、フィールド(10)と底部(15)被覆と比較して側壁(16)被覆性を向上させる処理を用いて、障壁層材料(912)のような均一な材料を半導体基板(21)上の高いアスペクト比のナノサイズの開口部(11)に蒸着するために調整される。そのiPVDシステム(200)は、そのターゲットから材料をスパッタするために、低いターゲットパワーと50mTより高い圧力で動作される。RFエネルギーは、高密度プラズマを生成するそのチャンバーに連結される。小さなRFバイアス(数ボルト未満)は、特に、底部における被覆性を高めることを助けるために印加されることができる。  (もっと読む)

(もっと読む)

下にあるバリア層への多孔性低誘電率膜の接着を促進する手法

下にあるバリア層に対する多孔性低誘電率膜の接着は、その上にある多孔性低誘電率膜より炭素含量が低く、シリコン酸化物が豊富な中間層を形成することにより向上する。この接着層は、多数の手法のうち一つを単独で又は組み合わせて利用して形成されてもよい。一つのアプローチでは、接着層は、低誘電率材料の堆積直前にO2/CO2/などの濃酸化ガスを導入してSi前駆体を酸化することにより形成することができる。別のアプローチでは、α−テルピネン、シメン及びその他の酸素非含有有機物などの熱的に不安定な化学物質が、低誘電率膜の堆積前に除去される。また別のアプローチでは、ハードウェア又はシリコン非含有成分を導入する方式などの処理パラメータが変更されて、低誘電率膜の堆積の前に酸化物界面の形成を可能とすることもできる。さらに別のアプローチでは、吸収量、エネルギー又は熱アニール処理の使用などの電子ビーム処理のパラメータが制御され、バリアと低誘電率膜との間の界面で炭素種を除去することもできる。さらなるアプローチでは、低誘電率堆積の前に前処理プラズマが導入されバリア界面の加熱を増進することにより、低誘電率堆積ガスが導入され、低誘電率膜が堆積される時、薄い酸化物界面を形成することもできる。 (もっと読む)

低誘電率ナノ細孔性膜の多段階硬化

本発明に従った実施形態は、化学気相堆積された低誘電率材料の多段階硬化プロセスに関する。特定の実施形態では、電子ビーム放射および熱暴露ステップの組合せが、膜に組み込まれているポロゲンの選択的脱ガス化をコントロールするために採用されてもよく、ナノ細孔の形成をもたらす。一具体的な実施形態によると、シリコン含有成分と、不安定基を特徴付ける非シリコン含有成分との反応に起因する低誘電率層は、電子ビーム形態の放射印加が続く熱エネルギーの初期印加によって硬化されてもよい。 (もっと読む)

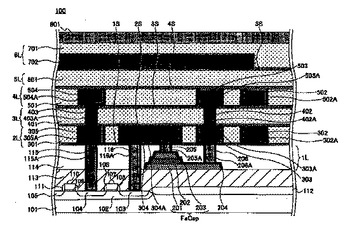

多層配線構造

【課題】 導電性のパターンを配置することができない領域があっても、CMP後の表面の平坦度を高めることが可能な多層配線構造を提供する。

【解決手段】 支持基板(20)の表面に、第1の領域(10)、該第1の領域を取り囲む環状の第2の領域(11)、及び該第2の領域を取り囲む第3の領域(12)が画定されている。支持基板の上に第1の配線層(M8L)が配置されている。第1の配線層の第3の領域内に配線が形成され、第2の領域内にダミーパターンが形成され、第1の領域内には導電パターンが形成されていない。第1の配線層の上であって、かつ第1の領域内に機能素子(1)が配置されている。

(もっと読む)

カーボンナノチューブ複合材相互接続ビアを用いた集積回路チップ

【課題】 カーボンナノチューブを用いて集積回路の導電性パスを形成することによって、好結果のデバイスを設計する。

【解決手段】 集積回路の導電体パスが、銅であることが好ましい導電性金属に埋設された複数の画一的なカーボンナノチューブを用いて形成される。導電体パスは、導電体層の間に延びるビアを含むことが好ましい。複合材ビアは、導電体上のビアが作られる位置に金属触媒パッドを形成するステップと、誘電体層を堆積しエッチングして空洞部を形成するステップと、空洞部内の触媒の上に実質的に平行なカーボンナノチューブを成長させるステップと、残された空洞部内の空隙を銅で埋めるステップによって形成されることが好ましい。次に、ビア・ホールの上に導電体層が形成される。

(もっと読む)

配線構造の形成方法及び半導体装置

下層配線(101)と不図示の上層配線とを接続するためのビア孔(102)を絶縁膜(103)にエッチングストッパー膜(104)及びハードマスク(105)を用いて形成した後、本発明の1ステップの低パワー・バイアス・スパッタ法によりビア孔(102)の内壁を覆うように絶縁膜(103)上にTaからなる下地膜(106)を形成する。ここで、ビア孔(102)の内壁面から絶縁膜(103)上にわたって薄く均一な膜厚の下地膜(106)が得られる。このように、比較的簡素な工程により、配線形成上の不都合を生ぜしめることなく、開口の内壁面、即ち側壁面から底面にかけて薄く均一に下地膜を成膜することを可能とし、信頼性の高い極微細な配線構造を実現する。

(もっと読む)

(もっと読む)

基板処理方法、プラズマ室および半導体デバイス

【課題】

【解決手段】基板処理のシステムおよび方法には、プラズマ室に基板を装填しプラズマ室の圧力を所定の圧力設定値に設定することが含まれる。プラズマ領域を構成するいくつかの内面が約200℃以上の処理温度に加熱される。プラズマを形成するために処理ガスがプラズマ領域に注入され、基板が処理される。

(もっと読む)

半導体装置、半導体装置の製造方法

本発明では、水素またはH2Oの拡散を防止することで強誘電体キャパシタの劣化を防止し、高品質の強誘電体キャパシタを有する半導体装置を提供することを課題とする。そのため、本発明では、基板上に形成された強誘電体キャパシタと、前記強誘電体キャパシタ上に形成された配線構造とを有する半導体装置であって、前

記配線構造は、層間絶縁層と当該層間絶縁層中に形成されたCu配線部を含み、前記層間絶縁層に面するように、水素拡散防止層を含むエッチングストッパー層が形成されていることを特徴とする半導体装置を用いた。  (もっと読む)

(もっと読む)

配線構造及びその製造方法

【課題】 高温で保持されても動作不良を起こさない、信頼性の高い多層配線構造を実現する。

【解決手段】 第1配線102Aと第2配線111とは、層間絶縁膜(SiO2 膜104及びFSG膜105)中に形成されたビア110Aを介して接続されている。第2配線111におけるビア110Aの接続部分の近傍にダミービア110Bが接続されている。ダミービア110Bは、実使用時において閉回路の一部分とはならない。

(もっと読む)

多孔質絶縁膜及びその製造方法並びに多孔質絶縁膜を用いた半導体装置

半導体装置を構成する絶縁膜として有効な多孔質絶縁膜の作製方法、該絶縁膜の上下界面に接する半導体材料と高い密着性を有する多孔質絶縁膜の作製方法を提供。

少なくとも一つ以上の、分子中に環状シリカ骨格を有し且つ該環状シリカ骨格に少なくとも一つ以上の不飽和炭化水素基が結合されている有機シリカ化合物の分子蒸気、を含む気体をプラズマ中に導入し、半導体基板上に多孔質絶縁膜の成長を行う。

(もっと読む)

集積回路相互接続の製作システム及び方法

ウエハ上の導電性表面を処理するシステム(100)は、前記ウエハの前記正面上に実質的に平面化される導電層を形成するように構成された電気化学機械処理(ECMPR)モジュール(106)と、前記ウエハのエッジ領域から導電物質を除去するように構成された、前記ECMPRモジュール内のチェンバーと、前記ECMPRモジュールから前記ウエハを受取り、平面化された前記導電層を研摩して前記金属の相互接続構造を形成するように構成されたCMPモジュールと、前記ECMPRモジュールから前記CMPモジュールへ前記ウエハを移送するように構成されたロボット(111)とを備える。

発明の1つの側面では、ECMPRモジュールは前記ウエハの前記正面上に物質を成膜させる。ECMPRモジュールは、前記ウエハの前記正面から前記導電層の少なくとも一部を除去する。本発明の利点は、成膜された金属の制御性を改善して素子の信頼性及び生産性を改善することを含む。  (もっと読む)

(もっと読む)

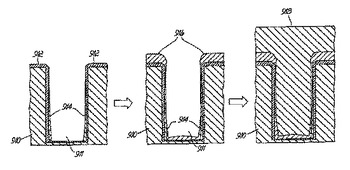

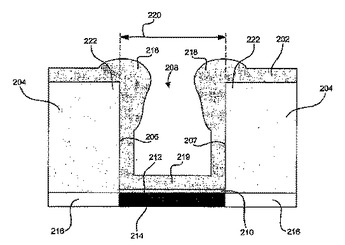

コンタクトの形成中、コンタクトホール幅の増大を防ぐ方法

一形態によれば、半導体ダイに位置するシリサイド層(214)上にコンタクトを形成する方法は、コンタクトホール(208)の各側壁(206、207)、及び、コンタクトホール(208)の底部に位置する自然酸化物層(210)に、バリア層(202)を堆積するステップを含み、各側壁(206、207)は、絶縁層(204)のコンタクトホールによって形成される。コンタクトホール(208)の各側壁(206、207)、及び、酸化物層(210)にバリア層(202)を堆積する(150)ステップにおいて、バリア層(202)の厚さを、コンタクトホール(208)の上部が、コンタクトホール(208)の底部よりも厚くなるよう最適化してもよい。この形態によれば、バリア層(202)の一部分(219)及びコンタクトホール(208)の底部に位置する酸化物層(210)を除去し、シリサイド層(214)を露出させるステップを含む方法も提供される。  (もっと読む)

(もっと読む)

低静電容量配線のための調節可能な自己整合型エアーギャップ誘電体

【課題】 低静電容量配線のための調節可能な自己整合型エアーギャップ誘電体を形成すること。

【解決手段】 調節可能で自己整合型の低静電容量集積回路のエアーギャップ構造は、相互接続層上で第二相互接続部に隣接する第一相互接続部と、該第一相互接続部及び該第二相互接続部の隣接する側部に沿って形成されたスペーサと、該第一相互接続部と該第二相互接続部との間に形成されたエアーギャップとを含む。エアーギャップは、第一相互接続部及び第二相互接続部の少なくとも一方の上面より上方で、かつ、該第一相互接続部及び該第二相互接続部の少なくとも一方の下面より下方に延び、スペーサ間の距離が該エアーギャップの幅を定める。エアーギャップは、第一相互接続部及び第二相互接続部の隣接する側部に自己整合する。

(もっと読む)

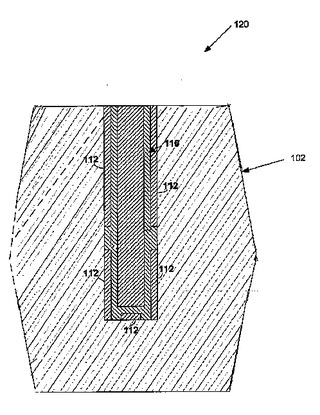

無電解メッキ化学反応を用いた深いビアシードの修復

高アスペクト比ビア内に連続シード層を形成する方法とそれに関連付けられる構造体を記載する。この方法は、基板内に凹部(104)を形成する段階と、凹部内に非連続金属層を形成する段階と、凹部内の非連続金属層(112)と、少なくとも1つの非堆積領域(109)を活性化させる段階と、凹部内の非連続金属層及び少なくとも1つの非堆積領域上にシード層(116)を無電解メッキする段階と、実質的にボイドがなく、金属が充填された凹部を形成するようシード層上に金属充填層を形成する段階を含む。  (もっと読む)

(もっと読む)

2,741 - 2,760 / 2,805

[ Back to top ]