Fターム[5F033PP03]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 原料ガス (624) | 無機系ガス (381)

Fターム[5F033PP03]の下位に属するFターム

ハロゲン化物 (210)

Fターム[5F033PP03]に分類される特許

61 - 80 / 171

半導体装置及び半導体装置の製造方法

【目的】コンタクトプラグ材料の基板への拡散を抑制する半導体装置及び半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、半導体基板200と導通するコンタクトプラグとなるCu膜260と、Cu膜260の少なくとも底面側に、半導体基板200と接触して配置された柱状結晶構造をもつTiN膜242と、Cu膜260の少なくとも底面側に、TiN膜242と接触して配置された、TiNのアモルファス膜244と、Cu膜260の底面側と側面側に、少なくとも一部がアモルファス膜244とCu膜260とに接触して配置された、TiN膜242材と同じ材料で柱状結晶構造をもつTiN膜246と、Cu膜260の側面側に配置されたSiO2膜220と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法、半導体装置、電子機器、半導体製造装置及び記憶媒体

【課題】基板上の凹部が形成された層間絶縁膜の露出面にバリア膜を成膜し、凹部内に下層側の金属配線と電気的に接続される銅配線を形成するにあたり、段差被覆性の良好なバリア膜を形成することができ、しかも配線抵抗の上昇を抑えた半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜に形成された凹部21の底面に露出した下層側の銅配線13の表面の酸化膜を還元あるいはエッチングして、当該銅配線13の表面の酸素を除去した後、マンガンを含み、酸素を含まない有機金属化合物を供給することによって、凹部21の側壁及び層間絶縁膜の表面などの酸素を含む部位に自己形成バリア膜である酸化マンガン25を選択的に生成させる一方、銅配線13の表面にはこの酸化マンガン25を生成させないようにして、その後この凹部に銅を埋め込む。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】半導体装置に適用される比較的膜厚の厚い絶縁膜中の水素濃度を大幅に低減する。

【解決手段】半導体装置70には、半導体基板1上に複数のメモリセルトランジスタが設けられる。n型拡散層7、シャロートレンチアイソレーション(STI)2、及び絶縁膜6上と、側壁絶縁膜8の側面とには積層シリコン窒化膜9が形成される。メモリセルトランジスタのゲートの周囲に積層シリコン窒化膜9が設けられる。積層シリコン窒化膜9は、例えば膜厚が略100nmであり、n層のシリコン窒化膜から構成される。n層のシリコン窒化膜の膜厚は、それぞれ3nm以下に設定される。n層のシリコン窒化膜は、それぞれ膜中の水素結合がプラズマ処理で置換され、水素が離脱され、膜中の水素濃度が大幅に低減されたシリコン窒化膜である。

(もっと読む)

ナノ構造処理のための導電性補助層の形成及び選択的除去

一又は複数のナノ構造の作成方法が開示されており、当該方法は:基板の上部表面上に導電層を形成すること;導電層上に触媒のパターン層を形成すること;触媒層上に一又は複数のナノ構造を成長させること;及び一又は複数のナノ構造の間及び周囲の導電層を選択的に除去することを含んでなる。デバイスもまた開示されており、該デバイスは、基板、ここで基板は一又は複数の絶縁領域によって隔てられた一又は複数の露出金属島を含んでなる;一又は複数の露出金属島又は絶縁領域の少なくともいくつかを覆う基板上に配された導電性補助層;導電性補助層上に配された触媒層;及び触媒層上に配された一又は複数のナノ構造を含んでなる。 (もっと読む)

半導体装置及びその製造方法

【課題】Wを材料とする接続部の下地膜の形成工程として、形成容易なプロセスを選択することができ、下層のCu配線である第1の配線のCuの浸食を抑制することにより、第1の配線と接続部との間における接触抵抗を低く抑えるとともにその均一性を高め、信頼性の高い半導体装置を実現する。

【解決手段】熱CVD法によりWF6、H2及びB2H6を含有し、シラン系ガスを含有しない第1の供給ガスを用いてW膜18aを形成した後、WF6及びH2を含有する第2の供給ガスを用いてW膜18bを形成し、CMPを経て、ビア孔16をW膜18で充填するWプラグ19を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ソースドレイン領域のサイズが増大することがない局所配線構造を備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極22及び半導体基板11におけるゲート電極22の両側方にそれぞれ形成された第1のソースドレイン領域29A及び第2のソースドレイン領域29Bを有するトランジスタ12と、半導体基板11の上における第1のソースドレイン領域29Aを挟んでゲート電極22と反対側に形成されたゲート配線42と、ゲート配線42と第1のソースドレイン領域29Aとを接続する局所配線構造60とを備えている。局所配線構造60は、第1のソースドレイン領域29A及びゲート配線42の上面に跨って形成されたSiGe層61によって構成されている。

(もっと読む)

Cu配線の形成方法

【課題】微細なトレンチまたはホールにも確実にCuを埋め込むことができるCu配線の形成方法を提供すること。

【解決手段】シリコン基板1上に形成されたトレンチ3を有するLow−k膜2にバリア層4を介してCu配線を形成するにあたり、バリア層4の上にCVDによりCuが濡れる金属材料で構成された被濡れ層5を形成し、被濡れ層5の上にPVDによりCu層6を形成し、Cu層6を形成した後、シリコン基板1を加熱してCu層6を流動させ、トレンチ3内にCuを流し込む。

(もっと読む)

ルテニウムの選択堆積を半導体デバイスの作製に統合する方法

Ruの選択堆積を半導体デバイスの作製に統合することで、Cuメタライゼーションにおけるエレクトロマイグレーションとストレスマイグレーションを改善する方法。当該方法は、熱化学気相成長法によって、Ru3(CO)12先駆体蒸気及びCOガスを有するプロセスガスを用いて、メタライゼーション層(302)上及びバルクCu(322)上にRu金属膜を選択的に堆積する工程を有する。1つ以上の選択的に堆積されたRu金属膜を有する半導体デバイスが記載されている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクト抵抗をより一層低減することができる半導体装置及びその製造方法を提供する。

【解決手段】コンタクトホール22の側面及び下面並びに層間絶縁膜21上にバリアメタル膜23を形成する。次に、バリアメタル膜23を覆うニッケル膜24をスパッタリング法により形成する。次に、ニッケル膜24を覆うと共に、コンタクトホール22を埋め込むタングステン膜25を熱CVD法により形成する。そして、CMP法により層間絶縁膜21上のバリアメタル膜23、ニッケル膜24及びタングステン膜25を除去する。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】メタルキャップ層の信頼性と生産性を向上させた半導体装置の製造方法及び半導体装置の製造装置を提供する。

【解決手段】成膜チャンバ40Dの内部空間Sに吸着期間の間だけZr(BH4)4を導入した。そして、シリコン基板2の表面、すなわち第2層間絶縁膜の表面及び第1配線の表面に、あるいはハードマスクの表面及び第2配線の表面にZr(BH4)4を吸着させ、吸着分子からなる単分子層を形成した。また、吸着期間の経過後、照射管47の内部に改質期間の間だけマイクロ波を照射し、プラズマ化したH2を、すなわち水素活性種をシリコン基板2の表面に供給した。そして、Zr(BH4)4の供給と、水素活性種の供給と、を交互に繰り返した。

(もっと読む)

マイクロデバイス用基板及びその製造方法並びにマイクロデバイス及びその製造方法

【課題】微細径で且つ高アスペクト比の貫通配線を有するマイクロデバイス用基板及びその製造方法並びにマイクロデバイス及びその製造方法を提供する。

【解決手段】基板本体31と、この基板本体31を厚さ方向に貫通する貫通孔32と、この貫通孔32内に埋め込まれ且つIV族元素と該IV族元素との化合物を形成する金属との化合物を含む貫通配線37とを具備することを特徴とするマイクロデバイス用基板にある。

(もっと読む)

低コンタクト抵抗を示すMOS構造およびその形成方法

低コンタクト抵抗を示すMOS構造(100,200)と、このようなMOS構造の形成方法が提供される。一方法では、半導体基板(106)が提供され、前記半導体基板上にゲートスタック(146)が形成される。前記半導体基板内に、前記ゲートスタックと整合された不純物ドープ領域(116)が形成される。前記不純物ドープ領域から延びる隣接するコンタクトフィン(186)が形成され、前記コンタクトフィン上に金属シリサイド層(126)が形成される。前記コンタクトフィンの少なくとも1つに存在する前記金属シリサイド層の少なくとも一部に対するコンタクト(122)が形成される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート形成溝内に埋め込んで形成される金属系ゲート電極を有するトランジスタ群と抵抗とを有する半導体装置で、抵抗値のばらつきをなくした抵抗形成を可能とする。

【解決手段】半導体基板11に、第1トランジスタ群と、これよりも低い動作電圧の第2トランジスタ群と、抵抗3とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介してシリコン系材料層71で形成された第1ゲート電極15を有し、第2トランジスタ群は、半導体基板11上の第1層間絶縁膜38に形成したゲート形成溝42内に第2ゲート絶縁膜43を介して金属系ゲート材料を埋め込むように形成された第2ゲート電極47、48を有し、抵抗3は、半導体基板11上に絶縁膜61を介してシリコン系材料層71と同一層で形成された抵抗本体部62と、この上部に形成された抵抗保護層63を有することを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体記憶装置の製造方法

【課題】セルサイズを縮小することのできるSRAMを提供する。

【解決手段】駆動MISFETおよび転送MISFETの上部には、縦型MISFET

が形成されている。縦型MISFETは、下部半導体層(ドレイン)57、中間半導体層

58、上部半導体層(ソース)59を積層した四角柱状の積層体(P1、P2)と、この積層体(P1、P2)の側壁にゲート絶縁膜63を介して形成されたゲート電極66とによって構成されている。縦型MISFETは、下部半導体層57がドレインを構成し、中間半導体層58が基板(チャネル領域)を構成し、上部半導体層59がソースを構成している。下部半導体層57、中間半導体層58、上部半導体層59の夫々は、シリコン膜で構成され、下部半導体層57および上部半導体層59はp型にドープされ、p型シリコン膜で構成される。

(もっと読む)

気相成長を介して連続的な銅薄膜を形成する方法

【課題】多層基材を調製するための方法を提供する。

【解決手段】本方法は、バリア領域と銅領域を含む第1層を提供する工程と、該第1層上に銅を含む第2層を堆積する堆積工程とを含み、該堆積工程が、前記バリア領域上に約20Å〜約2,000Åの第1の厚さと、前記第1層の前記銅領域上に約0Å〜約1,000Åの第2の厚さとを含む第2層を提供し、該第1の厚さが該第2の厚さよりも大きい、第1層と第2層を含む多層基材を提供する。

(もっと読む)

電子装置の製造方法及びそれを用いた電子装置

【課題】カービンナノチューブを用いた電流容量の大きいトランジスタや配線を製造容易な方法で作製する。

【解決手段】基板上に形成した触媒から垂直方向に、カーボンナノチューブ細線密度の高い、長さの揃ったカーボンナノチューブ束を配向成長し、この側面近傍に、カーボンナノチューブ束に親和性を有する液体である有機溶媒を滴下し、これを、窒素ガスを用いて、横倒ししたい方向の反対側からカーボンナノチューブ束方向に向かってブローして有機溶媒と共に垂直に立ったカーボンナノチューブ束を横倒しし、かつ基板表面に一定長さ(領域)をもって接触させる。有機溶媒を乾燥後、この接触領域の一部を、チャネル部として用いてバックゲート型トランジスタを、あるいは導体として配線を製造する。

(もっと読む)

タングステン材料の原子層堆積法

【課題】ALDプロセスを使用して、均一性が良好で、ほとんどまたは全く汚染がなく、かつ導電率が高いつまり抵抗率が低いタングステン含有材料を堆積するための改良されたプロセスを提供する。

【解決手段】一実施形態では、プロセスチャンバ内に基板を位置決めするステップであって、該基板がこの上に配置されている下地層を含有するステップと、該基板をタングステン前駆体および還元ガスに順次曝してALDプロセス時に該下地層上にタングステン核形成層を堆積するステップであって、該還元ガスが約40:1、100:1、500:1、800:1、1,000:1以上の水素/ハイドライド流量比を含有するステップと、該タングステン核形成層上にタングステンバルク層を堆積するステップとを含む、基板上にタングステン含有材料を形成するための方法が提供される。該還元ガスはジボラン、シランまたはジシランなどのハイドライド化合物を含有している。

(もっと読む)

半導体素子及びその製造方法

【課題】コンタクトプラグの形成のための平坦化工程で障壁層が損傷することを防止することができる半導体素子及びその製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、半導体基板上に複数の導電性構造物間の空間を埋め立てて上面が平坦化された絶縁膜を形成し、絶縁膜を部分的に除去して基板の一部を露出する開口を形成する。その後、開口の下部側壁及び底面に沿って形成された残留金属膜と開口の上部側壁及び残留金属膜の表面に沿って形成された金属窒化膜とを含む障壁層を形成する。障壁層を含む開口を埋め立てて金属プラグを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

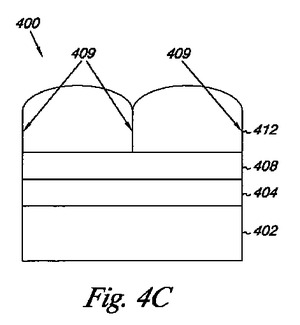

タングステンディジット線、その形成方法及び動作方法

タングステンディジット線を使用するための、及び、形成するための、方法、デバイス、及び、システムが記載されている。本開示の実施例に従って形成されたタングステンディジット線は、窒化タングステン(WNX)基板(402)上のタングステン(W)単分子層(404)と、W単分子層上のホウ素(B)単分子層(308)と、B単分子層上のバルクW層(412)とで形成されうる。バルクW層は、100nmから600nmの間の粒子サイズを有する。ディジット線は50nm未満の幅となりえる。従って、ディジット線のキャパシタンス及び抵抗は減少する。  (もっと読む)

(もっと読む)

61 - 80 / 171

[ Back to top ]