Fターム[5F033QQ30]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287) | エッチング後も残存させるもの (194)

Fターム[5F033QQ30]に分類される特許

21 - 40 / 194

半導体装置の製造方法

【課題】 金属部材の表面に、再現性よくバリア膜を形成する技術が望まれている。

【解決手段】 基板の上に、下部バリア膜を形成する。下部バリア膜の上にシード膜を形成する。シード膜の一部の領域上に、導電部材を形成する。導電部材をエッチングマスクとして、シード膜をエッチングし、導電部材の形成されていない領域において、下部バリア膜を露出させる。下部バリア膜の表面には堆積しない条件で、導電部材の表面に選択的に上部バリア膜を成長させる。上部バリア膜をエッチングマスクとして、下部バリア膜をエッチングする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コストが低い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、絶縁膜及び電極膜が交互に積層された積層体を形成する工程と、前記積層体上に、サイズが相互に異なる複数のホールが形成されたハードマスクを形成する工程と、マスク材料を堆積させることにより、最も小さい前記ホールを閉塞させると共に、その他の前記ホールを小さくする工程と、前記マスク材料及び前記ハードマスクをマスクとしてエッチングを施すことにより、前記その他のホールの直下域において、各所定枚数の前記絶縁膜及び前記電極膜を除去して、コンタクトホールを形成する工程と、前記コンタクトホールを介してエッチングを施すことにより、前記電極膜の一部分を除去して隙間を形成する工程と、前記隙間内に絶縁材料を埋め込む工程と、前記コンタクトホール内に導電材料を埋め込む工程と、を備える。

(もっと読む)

銅の光子誘起除去

【課題】基板から銅含有層の少なくとも一部を除去する方法を提供する。

【解決手段】第1反応チャンバ中で、銅含有表面層4の少なくとも一部を、ハロゲン化銅表面層5に変える工程と、第2反応チャンバ中で、光子含有雰囲気6に晒して、ハロゲン化銅表面層5の少なくとも一部を除去して、揮発性のハロゲン化銅生成物8の形成を始める工程とを含む。光子含有雰囲気6に晒す間に、この方法は、更に、第2反応チャンバから揮発性のハロゲン化銅生成物8を除去し、第2反応チャンバ中で揮発性のハロゲン化銅生成物8の飽和を避ける工程を含む。本発明の具体例にかかる方法は、銅含有層のパターニングに用いられる。例えば、本発明の具体例にかかる方法は、半導体デバイス中に銅含有相互接続構造を形成するのに使用される。

(もっと読む)

半導体装置及びその製造方法

【課題】ヒートシンクに生じる不具合を低減すること。

【解決手段】半導体装置は、第1面及び第2面を有し、第1面と第2面とを貫通するバイアホールを有する半導体基板と、第1面上に、バイアホールの開口と少なくとも部分的に重複するように形成された配線又は電極と、第2面上に形成され、バイアホールの開口と少なくとも部分的に重複する開口を有する応力緩衝層と、応力緩衝層上からバイアホールの内壁面に沿って延在し、配線又は電極と電気的に接続されたヒートシンクと、を備える。バイアホールの第2面における開口の大きさは、第1面における開口の大きさよりも大きい。応力緩衝層の熱膨張係数は、ヒートシンクの熱膨張係数未満である。

(もっと読む)

表面被覆方法、並びに半導体装置、及び実装回路基板

【課題】配線及び絶縁膜へダメージを与えることなく、絶縁膜上の導電性の不純物によるめっきの異常成長を抑制することができる表面被覆方法、並びに該方法を用いて製造される半導体装置、及び実装回路基板の提供。

【解決手段】水溶性樹脂、有機溶剤、及び水を含有する表面被覆材料を、表面に露出した絶縁膜及び表面に露出したパターニングされた金属配線を有する積層体の少なくとも前記絶縁膜の表面を覆うように塗布し、前記絶縁膜の表面に被膜を形成する表面被覆方法である。

(もっと読む)

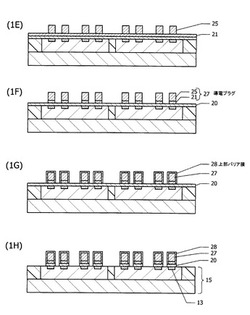

半導体装置及びその製造方法

【課題】多結晶シリコンプラグと上層の導体プラグとの界面に十分な膜厚の金属シリサイド層を形成してコンタクト抵抗の低減を図る。

【解決手段】多結晶シリコンプラグを形成した後、多結晶シリコンプラグの表面からゲルマニウムイオン注入を実施してゲルマニウム含有多結晶シリコン16Gとし、その後、シリサイド化可能な金属膜を成膜して金属シリサイド層19を形成し、金属シリサイド19上に導体膜(バリア膜20、W膜21)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】金属コンタクトを安定に形成できる半導体装置の製造方法を提供する。

【解決手段】セル領域にストレージノードコンタクトプラグ12を形成するステップと、第1の層間絶縁膜17を形成するステップと、周辺領域の第1の層間絶縁膜上に第1のビットライン20を形成するステップと、第2の層間絶縁膜22を形成するステップと、周辺領域の第2の層間絶縁膜上に第1のビットラインと電気的に接続された第2のビットライン25を形成するステップと、セル領域のストレージノードコンタクトプラグの上面を露出させるステップと、セル領域にストレージノードコンタクトプラグと接するキャパシタを形成するステップと、キャパシタが形成された基板の全面に第3の層間絶縁膜31を形成するステップと、周辺領域の第3の層間絶縁膜を貫通して第2のビットラインに接する金属コンタクト33を形成するステップとを含むことを特徴とする。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置の製造方法

【課題】低コストで、かつ簡便な方法で、コンタクトプラグ上に形成される銅配線の上面にヒロックが生じて短絡が発生することを抑制可能な半導体装置の製造方法を提供する。

【解決手段】配線13を覆う層間絶縁膜15の上面に、層間絶縁膜よりもエッチング速度の遅いエッチングストッパ膜16を形成する。エッチングストッパ膜のうち、配線と対向する部分を貫通する第1の開口部16Aを形成する。エッチングストッパ膜よりも層間絶縁膜がエッチングされやすい条件を用いて、配線の上面が露出するまで第1の開口部の下方に位置する層間絶縁膜をエッチングして、第1の開口部と共にコンタクトホールを構成する第2の開口部15Aを形成する。第1の開口部を埋め込むように、コンタクトホール内に導電膜を成膜することでコンタクトプラグ27を形成する。電解メッキ法により、コンタクトプラグの上面と接触する銅配線39を形成する。

(もっと読む)

半導体装置

【課題】工程数の増大を抑制しつつ、チップ上に形成された再配線または突出電極の信頼性を向上させる。

【解決手段】配線2bおよびパッド電極2aが形成された半導体基板と、半導体基板上に形成された応力緩和層4と、応力緩和層4上に合金シード膜5を形成した後、応力緩和層4と合金シード膜5とを熱処理にて反応させることで、応力緩和層4と合金シード膜5との間に反応性バリア絶縁膜6を形成する。再配線8または突出電極は合金シード膜5上に形成する。

(もっと読む)

貫通電極基板

【課題】 貫通電極を細くすると、基板に形成した貫通孔を金属材料で埋め込むことが困難になる。また、体積の大きな金属部材が基板内に埋め込まれると、熱膨張係数の差に起因して、機械的な破壊が生じやすくなる。

【解決手段】 基板の第1の表面に、第1の導電膜を含む積層膜が形成されている。基板の、第1の表面とは反対側の第2の表面から内部に向かって、第1の表面までは達しない凹部が形成されている。凹部の底面から第1の表面まで達する貫通孔が形成されている。この貫通孔は、凹部よりも細い。貫通孔内に第2の導電膜が埋め込まれている。第2の導電膜は、第1の導電膜に接続され、凹部の側面及び底面を覆うが、凹部を完全には埋め尽くしていない。

(もっと読む)

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】再配線のパターン形成後のレジストパターンの剥離性を確保しつつ、再配線のパターン形成前のレジストパターンとその下地との密着性を向上させる。

【解決手段】半導体チップ上に形成されたメタル膜5の表層には、レジスト膜6との密着性を上げる表面改質層16が形成され、表面改質層16を介してメタル膜5上に再配線7a〜7cが形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 外部接続用電極の周囲を封止膜で覆ったCSPと呼ばれる半導体装置において、封止膜の上面側を研削するとき、外部接続用電極の上面にバリが発生しないようにする。

【解決手段】 メッキレジスト膜を用いた電解メッキにより外部接続用電極10を形成した後に、サーフェスプレーナーを用いて全ての外部接続用電極10の上部およびそれに対応するメッキレジスト膜の上面側を切って除去し、外部接続用電極10の高さを揃える。この場合、外部接続用電極10の上面にバリが発生することはない。次に、メッキレジスト膜を剥離し、封止膜11を形成し、封止膜11の上面側を研削し、外部接続用電極10上に封止膜11が僅か例えば厚さ数μm〜10μm残るようにする。この場合、外部接続用電極10の上部は研削しないため、外部接続用電極10の上面にバリが発生することはない。次に、外部接続用電極10の上面中央部に対応する部分における封止膜11に、レーザビームを照射するレーザ加工により、開口部12を形成する。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

配線の形成方法及びその配線を有する表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】配線の形成方法及び配線を有する表示装置の形成方法は、基板上若しくは回路素子上に設けられた第1の金属拡散防止膜上に、金属シード層をCVD法により形成し、フォトレジストマスクを用いて選択的に無電解メッキ法、又は電解メッキ法により、金属配線層を形成し、金属シード層及び第1の金属拡散防止膜の不要領域除去と、金属シード層及び金属配線層及び第1の金属拡散防止膜の側面を含む表面を覆うように無電解メッキ法による第2の金属拡散防止膜の選択的な形成とにより配線及び電極を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】再配線間のリークを抑制しつつ、再配線のピッチを微細化するとともに、再配線上のビア開口時のマージンを上げる。

【解決手段】緩衝層4上には再配線7bが形成され、再配線7b上には表面層8bが形成されている。表面層8bは、再配線7bから幅方向にはみ出すようにして再配線7bに沿うように配置され、再配線7bよりもエッチング耐性が高い。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作マージンを確保した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセル及び前記複数のメモリセルを選択する複数の選択配線を有するセルアレイを複数積層してなるセルアレイブロックと、第1高さから第2高さまで積層方向に延び、前記セルアレイブロックの選択配線のうちの所定の第1配線が側面に接続された柱状の第1ビアと、前記第1高さから第2高さまで積層方向に延び、前記セルアレイブロックの選択配線のうち前記第1配線よりも上層の所定の第2配線が側面に接続された柱状の第2ビアとを備え、前記第2配線は、前記第1配線よりも積層方向に厚く、且つ、前記第1配線よりも抵抗率が高いことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

回路基板及びその製造方法

【課題】配線抵抗が低く配線間の絶縁性の高い回路基板及びその製造方法を提供する。

【解決手段】基板上に、Cuを含む導電性材料の配線構造体を形成し、配線構造体の表面に、Cu−N結合を有する絶縁性の拡散防止膜を形成した後、拡散防止膜が形成された配線構造体を覆うように、絶縁膜を形成する。

(もっと読む)

21 - 40 / 194

[ Back to top ]