Fターム[5J039MM00]の内容

パルスの操作 (9,993) | 目的、機能 (1,546)

Fターム[5J039MM00]の下位に属するFターム

電圧変動に対する補償 (54)

温度変化に対する補償 (49)

高速化 (185)

低消費電力化 (218)

出力パルス幅の制御 (94)

出力パルス波高値の制御 (17)

ノイズ対策 (207)

ジッタの除去 (43)

点検、監視 (131)

パルスの欠落対策 (8)

ジッタ、歪の付加 (41)

表示 (3)

フェイルセーフ (23)

その他 (351)

Fターム[5J039MM00]に分類される特許

101 - 120 / 122

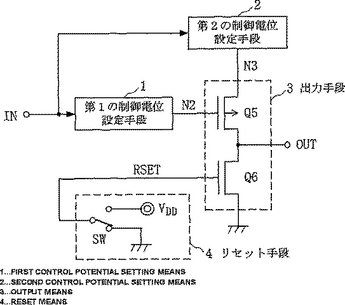

波形整形回路

第1の制御電位設定手段(1)は入力信号(IN)が論理閾値の近傍に達したときに第2の制御電位(N3)との大小関係が逆転する第1の制御電位(N2)を生成する。第2の制御電位設定手段(2)は、入力信号(IN)の変化に応じて入力信号(IN)と同方向に変化する第2の制御電位(N3)を生成する。出力手段(3)は、トランジスタ(Q5,Q6)からなり、第1の制御電位(N2)と第2の制御電位(N3)とリセット信号(RSET)とに基づいて所定の電位の出力信号(OUT)を生成する。リセット手段(4)は、波形整形回路の動作時にトランジスタ(Q6)をオフにする。  (もっと読む)

(もっと読む)

シフトレジスタ及びその駆動方法

本発明は、インバータの入力部をインバータの閾値電位にし、インバータの入力部に容量手段を介してCK信号を入力することで、CK信号は増幅され、その増幅されたCK信号をシフトレジスタに用いる。つまり、インバータの閾値電位を取得することで、トランジスタの特性ばらつきに殆ど影響しないシフトレジスタを提供することができる。  (もっと読む)

(もっと読む)

半導体集積回路及びその制御方法

【課題】

本発明の目的は、感度調整回路を備えたコンパレータおよびこのコンパレータ有

したデータ通信装置を提供することである。

【解決手段】

本発明においては、CMOSトランジスタで構成され、マイクロコンピュータに

よりオフセット(感度)制御可能なコンパレータ(差動増幅アンプ)が実現される

。この感度調整回路を備えたコンパレータを備えることにより、コストおよび回路

面積を増やすことなく感度の高いデータ通信装置が実現できる。そして、このデー

タ通信装置を使用することにより、より遠距離に位置する電波源からの電波受信をすることができる。また、アンプ感度調整回路を任意の感度に調整することによっ

て、特定の通信距離範囲に渡って配置される電波源との間で常に安定した通信が確

保されると共に、無用なノイズに対する感度を落として良質な通信を維持できる。

(もっと読む)

シグマデルタベースのフェーズロックループ

位相周波数検出器(PFD)と、チャージポンプと、電圧制御発振器とを含むシグマデルタベースのフェーズロックループ・デバイスが提供される。PDFは、基準信号とフィードバック信号とを受信し、基準信号とフィードバック信号との比較に基づく信号を出力する。チャージポンプは、PFDからの出力信号に基づくチャージを出力する。チャージポンプは、固定量の電流を流す第1の電流源と、可変量の電流を流す第2の電流源とを含む。電源制御発振器は、チャージポンプからの受け取ったチャージに基づくクロック信号を出力する。  (もっと読む)

(もっと読む)

レベルシフト回路

【課題】 小規模な回路構成で入力信号と出力信号の電圧差が大きい場合であっても十分に動作し、かつ入力信号と出力信号との間で、デューティサイクル及び位相が同一であるレベルシフト回路を提供する。

【解決手段】 レベルシフト回路(3)は、所定の第1正側電源電圧VDD1と所定の負側電源電圧との間の振幅を有する2値の相反するレベルの一対の入力信号を、第1正側電源電圧VDD1よりも大きい所定の第2正側電源電圧VDD2と負側電源電圧との間の振幅を有する2値の相反するレベルの一対の信号にレベルシフトさせて出力する。レベルシフト回路(3)は、一対の入力信号を第2正側電源電圧VDD2と負側電源電圧との間の振幅を有する2値の信号にそれぞれレベルシフトさせて出力するレベルシフト回路部(4)と、レベルシフト回路部(4)からそれぞれ出力された2つの信号のレベル変化のタイミングを調整するタイミング調整回路部(5)とを備える。

(もっと読む)

可変遅延回路及び半導体集積回路装置

【課題】 高い精度で遅延時間を制御できる可変遅延回路を用いた半導体集積回路装置を提供することを目的とする。

【解決手段】入力クロック信号を遅延させる第1のDLL回路3と、第1のDLL回路よりも高い精度で遅延を制御できる第2のDLL回路10とを有し、第1及び第2のDLL回路の位相比較(31、14)を独立に動作させ、かつ第2のDLL回路の遅延量制御を第1のDLL回路の動作に従属させることで、入力クロック信号に対し所定の位相関係を有する出力クロック信号を出力するように第1及び第2のDLL回路で遅延を与える半導体集積回路装置。

(もっと読む)

データ伝送装置、およびデータ伝送方法

【課題】パラレルデータを、シリアルデータに正確に変換して所定のデータ伝送路に出力するデータ伝送装置、および、パラレルデータを、シリアルデータに正確に変換して所定のデータ伝送路に出力するデータ伝送方法を提供する。

【解決手段】伝送されてくるパラレルデータが同期している第1の基準クロックとは別の第2の基準クロックを生成するクロック生成部1311と、上記パラレルデータを、上記第2の基準クロックに基づく第2のパラレルデータに変換するASIC1313と、このASIC1313から出力された第2のパラレルデータを、上記第2の基準クロックに基づくシリアルデータに変換するシリアライザ1315とを、全て同一基板上に備えた。

(もっと読む)

集積回路

【課題】 回路評価において、集積回路に入力するクロックのON/OFF制御を不要とし、その集積回路における他の回路部に影響を与えることなく、複数のクロック断検出回路の動作確認を同時に行うことを可能とする。

【解決手段】 入力されるクロックを停止することなく、クロック断を検出する集積回路10であって、クロック断を検出するクロック断検出部20と、クロック断検出部20に入力されるクロックを、クロック断検出部20に入力される前に入力し、マスク設定がON状態である場合はマスクして、マスク設定がOFF状態である場合はそのままで、クロック断検出部20へ出力するクロックマスク制御部21とを備えた集積回路。

(もっと読む)

多相クロック生成回路

【課題】 基準クロックの高速性やフリップフロップの高速動作を必要とせずに、狭い位相差を有する多相クロックを生成することができる多相クロック生成回路を提供する。

【解決手段】 基準クロックを基に位相が異なる複数の出力クロックを生成する多相クロック生成回路において、位相が異なる第1及び第2の基準クロック(clka,clkb)をそれぞれ分周して出力クロックを生成する第1及び第2の分周回路(diva,divb)と、第1及び第2の分周回路の所定のノード(divbx_qx,divax_qx)間を間欠的に短絡するスイッチとを有し、当該スイッチは、定常動作状態で前記所定のノードが同じレベルに制御されるタイミングで、当該所定のノード間を短絡する。具体的には、スイッチは、第1、第2の基準クロックのいずれかまたは両方により短絡制御される。独立して動作する分周回路が、位相が異なる基準クロックを分周して、位相が異なる出力クロックを生成し、短絡スイッチにより両分周回路の動作を整合させて、分周回路が生成するそれぞれの分周クロックの位相ずれを整合させる。

(もっと読む)

等間隔パルス列生成装置および生成方法

【課題】 低消費電力を図り、かつ周波数の変動を生じない精度の良い出力波を得ることのできる位相合成装置および位相合成方法を提供する。

【解決手段】

クロックに同期した位相データと所定電圧値とのクロス点前後の位相データの差分をサンプルホールドした後アナログ値に変換するD/A変換器2と、D/A変換器により変換されたアナログ値を電流に変換する電流源3および該電流を時間的に積分するコンデンサ4からなる積分器5と、積分器の電荷を放電するリセット回路6とを備える直線補間回路を有する位相合成装置およびそれを用いた位相合成方法により、コンデンサのゲイン変化やD/A変換におけるDCオフセット誤差に影響されることなく、ジッタの小さい精度の良い出力波を合成することができる。

(もっと読む)

クロック生成回路

【課題】

所望の分数逓倍、分周クロックを出力し、面積、電力の増大を抑止するクロック生成回路の提供。

【解決手段】

複数段の遅延回路10A1〜10A4を備え、入力される信号の遅延を測定する第1の遅延回路列と、第1の遅延回路列に対し信号伝播方向が逆向きに配置され、複数段の遅延回路10B1〜10B4を備えた遅延再現用の第2の遅延回路列と、を備え、第1の遅延回路列で遅延が検出された位置の遅延回路から出力される信号に基づき、前記遅延が検出された位置に対応する、前記第2の遅延回路列の遅延回路において、遅延回路の出力端子が入力端子に帰還されて閉ループを構成しリング発振回路を構成し、リング発振回路の発振出力が、第2の遅延回路列の出力端子から取り出される。第1の遅延回路列の前段には、制御信号に基づき、入力信号に対する出力信号の位相が可変に制御する位相補間器201、202を備え、第1の遅延回路列は、位相補間器201、202の出力信号の位相差を測定する。

(もっと読む)

駆動状態検出回路

【課題】交流駆動される被駆動体の駆動状態を検出する駆動状態検出回路に関し、付加的な回路を設けることなく、簡単な構成で被駆動体の状態を検出できる駆動状態検出回路を目的とする。

【解決手段】交流駆動される複数の被駆動手段(21、22)の駆動状態検出回路において、該被駆動手段に流れる交流電流を各々検出する電流検出手段(Rs1、Rs2、Rs3、Rs4、D1、D2)と、該電流検出手段で検出された複数の交流検出信号のうち最大検出出力する最大値出力手段(91)と、該出力手段の出力信号に係数乗算する係数乗算手段(94)と、電流検出された複数の交流検出信号を各々係数乗算手段(94)の出力信号とを比較し、各被駆動手段(21、22)の状態に応じた状態信号を出力する比較手段(95、96)と、この複数の状態信号を論理合成する論理合成手段(99)と、この出力に基づいて駆動状態検出信号生成する出力手段(100)とを有する。

(もっと読む)

クロックツリーの動的な平衡方法

【課題】 より多い電流を発生して、クロックがより遅くなるある沈みの時間遅延を補償することができるクロックツリーの動的な平衡方法を提供する。

【解決手段】クロックツリー回路において、制御可能なバッファを前記クロックツリー回路の特定なレベルに差込み、且つ何れか二つの位相の異なるクロックを接収する制御器を提供し、前記制御器の出力バスC[x:0]により制御可能なバッファにおけるPMOS/NMOSの排列を制御する。

(もっと読む)

チャージポンプ回路

【課題】チャージポンプ回路の効率を向上させるとともに、チャージポンプ回路の全体のパターン面積を小さくする。

【解決手段】第1及び第2の電荷転送用MOSトランジスタM1(N),M2(N)の両方をNチャネル型で構成する。第2の電荷転送用MOSトランジスタM2(N)をスイッチング動作させるために、さらにもう一段のポンピングパケットを追加したものである。そして、第2の電荷転送用MOSトランジスタM2(N)がオンするときのVGS(ゲートソース間電圧)を2VDDにして、低いオン抵抗を得るために、ポンピングパケットを駆動する第2のクロックドライバーCD2の電源としてチャージポンプ回路の出力電圧B(2VDD)を用いた。

(もっと読む)

チャージポンプ回路

【課題】チャージポンプ回路の効率を向上させるとともに、チャージポンプ回路の全体のパターン面積を小さくする。

【解決手段】第1及び第2の電荷転送用MOSトランジスタM1(N),M2(N)の両方をNチャネル型で構成する。第2の電荷転送用MOSトランジスタM2(N)をスイッチング動作させるために、さらにもう一段のポンピングパケットを追加したものである。そして、第2の電荷転送用MOSトランジスタM2(N)がオンするときのVGS(ゲートソース間電圧)を2VDDにして、低いオン抵抗を得るために、ポンピングパケットを駆動する第2のクロックドライバーCD2の電源としてチャージポンプ回路の出力電圧B(2VDD)を用いた。

(もっと読む)

ダイオード回路

【課題】

小面積で集積可能なダイオード回路を形成することは困難であった。

【解決手段】

本発明のダイオード回路は、ソースが第1の入力端子に接続された第1のMOSトランジスタと、ソースが第2の入力端子に接続され、ゲートおよびドレインが前記第1のMOSトランジスタのゲートに接続された第2のMOSトランジスタ、および前記第1のMOSトランジスタのドレインに接続された第1の抵抗性負荷を有する差動回路と、前記差動回路の出力に基づいて導通状態が制御される第3のMOSトランジスタとを有している。

(もっと読む)

半導体集積回路

【課題】 エッジトリガで動作するレジスタ回路に簡単なハードウェアを付加してノイズ等の影響によるレジスタへの誤書き込み防止をはかる。

【解決手段】 書き込み制御回路が、レジスタ回路1に対する新しいデータの書き込み時、レジスタ回路1に記憶されたデータを読み出し、先にラッチ回路3に保持されたデータと一致検出回路2で一致が検出されたときのみその書き込みを許可して、狭パルス状のノイズに対するプロテクトを行う。

(もっと読む)

遅延同期ループ回路の良否検査方法及び遅延同期ループ回路の良否検査回路

【課題】

ディジタルデータをもとに良否判定可能な比較的安価な検査装置を用いて遅延同期ループ回路の良否検査を行うことができる遅延同期ループ回路の良否検査方法及び、遅延同期ループ回路の良否検査回路を提供する。

【解決手段】

基準信号を所定時間ずつ遅延させたN個のタップ信号を出力する遅延同期ループ回路の良否検査回路及びこの良否検査回路により行う良否検査方法において、各タップ信号をクロック信号とするN個のフリップフロップといずれかのタップ信号をクロック信号とするフリップフロップとを直列接続することによってシフトレジスタを形成し、このシフトレジスタを基準信号の1周期分動作させて、N個目のフリップフロップの出力信号とN+1個目のフリップフロップの出力信号とに基づいて遅延同期ループ回路の良否を判定することとした。

(もっと読む)

SMD任意逓倍回路

【課題】

入力信号に同期し逓倍数が可変に設定される信号を出力する逓倍回路の提供。

【解決手段】

入力信号の周波数を可変に逓倍した出力信号を出力する逓倍回路であって、入力信号の周期を測定する周期測定用の遅延回路と、周期測定用の遅延回路で測定された周期に基づき、遅延時間が可変に設定され、遅延時間を再現する遅延再現用の遅延回路とを備えた同期遅延回路10と、同期遅延回路から出力される位相が異なる複数の信号を受けて多重化する多重回路20と、設定逓倍値にしたがって、周期測定用の遅延回路の遅延段数、遅延再現用の複数の遅延回路の段数の設定を可変に設定する制御回路30とを備え、多重回路20から入力信号に同期しその周波数を逓倍した出力信号が出力される。

(もっと読む)

関連付けされていないリンクを介し信号を繰り返す機構

一実施例によるシステムが開示される。本システムは、第1集積回路(IC)と、第1ICに接続される第1インタフェースと、インタフェースに接続される第2ICとを有する。第1ICは、インタフェースに関連付けされていない複数の信号のそれぞれの状態を、当該状態の変化が検出される毎にインタフェースを介し第2ICにインバンドに送信する。 (もっと読む)

101 - 120 / 122

[ Back to top ]