Fターム[5J039MM00]の内容

パルスの操作 (9,993) | 目的、機能 (1,546)

Fターム[5J039MM00]の下位に属するFターム

電圧変動に対する補償 (54)

温度変化に対する補償 (49)

高速化 (185)

低消費電力化 (218)

出力パルス幅の制御 (94)

出力パルス波高値の制御 (17)

ノイズ対策 (207)

ジッタの除去 (43)

点検、監視 (131)

パルスの欠落対策 (8)

ジッタ、歪の付加 (41)

表示 (3)

フェイルセーフ (23)

その他 (351)

Fターム[5J039MM00]に分類される特許

41 - 60 / 122

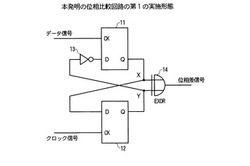

位相制御回路

【課題】 データ信号とクロック信号がどのような位相差であっても位相差に応じたパルス幅の位相差信号を出力する。

【解決手段】 データ信号および反転した信号Yを入力し、反転した信号Yをデータ信号の遷移タイミングで保持して信号Xを出力する第1の保持手段と、クロック信号および信号Xを入力し、信号Xをクロック信号の遷移タイミングで保持して信号Yを出力する第2の保持手段と、信号Xおよび信号Yを入力し、その位相差に応じたパルス幅を有する位相差信号を生成し、データ信号とクロック信号の位相差に応じたパルス幅を有する位相差信号として出力する比較手段とを備える。

(もっと読む)

高速時間ディジタル・コンバータ

【解決手段】 時間ディジタル・コンバータ(TDC)がサブ・インバータ遅延分解能でサンプリングすることを可能にするための手法が開示されている。一実施形態では、TDC中の差動型D−Qフリップフロップへの入力は、シングルエンド型信号、およびこの信号の遅延された形態および反転された形態に接続されてこの信号の時間補間を可能にする。さらに、TDC中の第1遅延ラインおよび相補な遅延ラインの負荷の平衡を保つための手法が開示されている。 (もっと読む)

信号変調回路

【課題】発振回路からの連続信号のレベル調整を行う場合であっても、送信電力を制御することが可能な信号変調回路を提供する。

【解決手段】信号変調回路の一例であるパルス生成回路は、発振回路と、制御信号発生回路と、逓倍回路と、フィルタと、制御部からなる。発振回路、及び逓倍回路は能動素子で構成されるアクティブ回路である。発振回路から連続信号が出力されて逓倍回路に入力され、制御信号発生回路から出力される制御信号によって逓倍回路が間欠的に動作することでパルス信号を生成し、制御部からの信号により電力レベルを簡易に調整する。

(もっと読む)

位相調整回路および試験装置

【課題】被測定信号の位相を、基準信号の位相に精度よく合わせることができる位相調整回路を提供する。

【解決手段】被測定信号の位相を調整する位相調整回路であって、トリガ信号を生成するトリガ発生部と、基準信号を受け取り、共通の前記トリガ信号のタイミングで、被測定信号および基準信号を測定し、被測定信号および基準信号のそれぞれの信号レベルの差分に応じた測定結果を出力するレベル比較部と、レベル比較部が出力する信号レベルの差分が略零となるように、被測定信号の位相を調整する信号位相調整部とを備える位相調整回路を提供する。

(もっと読む)

車載情報伝達装置

【課題】インバータの温度を感知する感温ダイオードSDの温度に関する情報をマイコン20に伝達する際に、マイコン20のタイマ機能やA/D変換機能を備えたポートを使用すると、そのリソースが低減すること。

【解決手段】感温ダイオードSDの出力電圧に基づき周波数変調回路34にて周波数変調された信号は、フォトカプラ36に取り込まれる。フォトカプラ36の出力は、マイコン20に取り込まれる。マイコン20においては、フォトカプラ36の出力電圧が閾値電圧以上であるなら論理「H」と認識し、閾値電圧未満であるなら論理「L」と認識する処理を、ハードウェアにて行う。一方、論理「H」である期間や論理「L」である期間に基づく温度情報の復調処理を、ソフトウェア処理とする。

(もっと読む)

インターフェイス回路およびそれを備える表示装置

【課題】波形整形回路の周波数特性の測定を可能にする。

【解決手段】波形整形回路11は、入力差動信号INN,INPを波形整形する。出力切換回路12は、通常モードのときには、波形整形回路11からの整形差動信号SP,SNを2値化して出力する。一方、出力切換回路12は、テストモードのときには、波形整形回路11からの整形差動信号SN,SPを正弦波信号として出力する。

(もっと読む)

クロック生成回路およびその使用方法

【課題】基準信号の周波数を逓倍又は分周したクロック信号を生成するクロック生成回路において、一つの基準信号から任意周波数のクロック信号を発生可能とする。

【解決手段】クロック生成回路1は、リング状に連結したm個の遅延素子DUからなるパルス遅延回路10と、各遅延素子DUから順次出力される通過信号P1〜Pmに基づき、基準信号CKIの周期を遅延素子DUでの遅延時間を単位として表した周期データDTを生成する周期測定部20と、除数又は乗数として使用される設定値MNを格納する設定値レジスタ50と、周期データDTに、設定値MNを乗・除してクロック信号の出力周期を表す制御データCDを生成する制御部30と、制御データCDと通過信号P1〜Pmとに基づき、基準信号CKIを分周又は逓倍したクロック信号CKOを出力する出力部40とを備え、実数で表された設定値MNを用いる。

(もっと読む)

クロック発生回路

【課題】クロック発生回路において、コストの増大を回避すること。

【解決手段】ディジタル位相比較器1、ディジタルループフィルタ2、DDS3、バンドパスフィルタ4、増幅器5、OCXO6および第1分周器7は、ディジタルPLLを構成する。OCXO6から与えられるDDS3の動作周波数をfSとし、DDS3の出力設定周波数をfOとし、nを自然数とすると、DDS3からは、ディジタル/アナログ変換のイメージ成分として、[n×fS±fO]の周波数の信号が出力される。バンドパスフィルタ4は、このイメージ成分の周波数を通過帯域とする特性を有する。

(もっと読む)

データ受信装置およびマイクロコンピュータ

【課題】CR発振回路に温度変化や経年変化が生じても正確な周波数を持つクロック信号を生成する。

【解決手段】CR発振器12の温度を示すA/D変換値とCR発振回路8の逓倍数を決める逓倍数設定値FMULRとを対応付けてEEPROM3に記憶し、A/D変換値(検出温度T)に応じた逓倍数設定値FMULRを読み出してCR発振回路8のレジスタに設定する。通信回路7が同期信号を受信するごとにクロック信号CLKを計数して1ビット長を計測し、その計数値XAと正規の1ビット時間に対する基準周期に基づく基準計数値XBとに基づいて逓倍数設定値FMULRを補正し、補正後の逓倍数設定値FMULRを検出温度Tに対応させてEEPROM3に書き込む。

(もっと読む)

クロック制御回路およびそれを搭載した半導体集積装置

【課題】ダブルエッジトリガ型フリップフロップ回路に対するクロック信号の供給を停止させるとき、当該フリップフロップ回路が保持するデータが不必要に更新されてしまうことがある。

【解決手段】エッジ検出回路61は、第1クロック信号を受け、そのエッジを検出すると、所定幅のパルス信号を出力する。論理ゲートは、エッジ検出回路61の出力信号と、ダブルエッジトリガ型フリップフロップ回路の使用状態を示すイネーブル信号とを受け、イネーブル信号が有意な期間、エッジ検出回路61の出力信号に追従する信号を出力し、イネーブル信号が非有意な期間、非有意なレベルの信号を出力する。トグル型フリップフロップ回路は、論理ゲートの出力信号を受け、所定幅のパルス信号を検出するたびに、論理レベルが反転する信号を、第2クロック信号として出力する。

(もっと読む)

等位相間隔の閉ループリレードライバ

【課題】一つのシステムに複数のリレーが存在する場合のリレーへの電流を制御するための方法、システムを提供する。

【解決手段】出力分配システムは、少なくとも2つのリレーと等位相間隔にパルス信号を発信する等位相間隔パルス発生器と、パルス信号に基づき、少なくとも2つのリレーへの電流を制御する、少なくとも2つのリレーのそれぞれに1つずつ接続され、パルス信号に基づき、少なくとも2つのリレーに送り込む電流を制御する少なくとも2つのドライバを備える。

(もっと読む)

半導体集積回路およびイコライザの制御方法

【課題】回路規模の増大を抑制しつつ、受信したデータ信号の等化量を調整することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路100は、イコライザと、イコライザにより等化されたデータ信号の位相を検出しこのデータ信号の位相と復元クロック信号の位相とを比較し、等化されたデータ信号のビット幅が復元クロック信号の周期よりも小さいときは第1の比較信号を出力し、一方、大きいときは第2の比較信号を出力し、復元クロック信号の位相がデータ信号の位相よりも進んでいる場合には第3の比較信号を出力し、遅れている場合には第4の比較信号を出力する位相比較回路と、第3、第4の比較信号および基準クロック信号に基づいて、復元クロック信号を生成する復元クロック生成回路と、少なくとも第1、第2の比較信号に基づいて、イコライザのピーキング量を制御する制御回路と、を備える。

(もっと読む)

半導体集積回路装置および出力バッファ遅延変動検出方法

【課題】I/Oバッファの実際の配置場所及び実際の動作タイミングにおけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を容易に検出し、オーバーマージンな設計を回避できるようにした半導体集積回路装置を提供する。

【解決手段】差動アンプ152で、VSS変動の影響を受けている出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP1として求める。差動アンプ153で、VDE変動の影響を受けている出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP2として求める。差動アンプ154で、VDE・VSS変動の影響を受けていない状態での出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP3として求める。

(もっと読む)

検出装置及び検出方法

【課題】自由振動波の位相ズレ成分を簡単な回路構成で精度良く検出する。

【解決手段】検出コイルLとコンデンサCとを接続してなる共振回路2を駆動し、該共振回路2から出力される振動波の位相ズレ成分にもとづいて検出を行う検出装置(近接センサ10)であって、共振回路2に対して所定数の駆動信号を出力し、駆動信号出力停止後に共振回路2から減衰状に出力される自由振動波を、該自由振動波の電圧0地点を検出するゼロクロス回路11に入力し、該ゼロクロス回路11の出力に基づいて自由振動波の数をカウントし、該カウント数が所定数に達したか否かを判断する自由振動波カウント処理を行い、該自由振動波カウント処理に要した時間測定にもとづいて自由振動波の位相ズレ成分を検出する。

(もっと読む)

ディジタル信号の位相差検出方法

【課題】比較的低速かつ小規模のディジタル回路により精度の高い位相差検出を行う。

【解決手段】トラッキングサーボ回路10において、入力部のローパスフィルタ(LPF)12〜18および利得制御増幅器(GCA)20〜26はアナログ回路であり、A/D変換器28〜34より後段のオフセット・キャンセル回路36〜42、イコライザ(EQ)44〜50、位相差検出器52,54、加算器56、LPF58、利得制御増幅器(GCA)60およびサーボDSP154はすべてディジタル回路で構成される。両位相差検出器52,54は本発明の位相差検出方法にしたがって両入力信号の位相差を検出する。

(もっと読む)

クロック信号生成回路、及び半導体装置

【課題】製造プロセスにおけるばらつきが原因による同期期間や同期期間終了後の自走期間において、周波数が変動することがなく、安定した動作を実現し、また安価な半導体装置を提供する。

【解決手段】第1の基準クロック信号を生成する基準クロック信号生成回路と、第1基準クロックの信号及び同期信号を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第1のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第2のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号を分周し、第2の基準クロック信号を生成する第1の分周回路と、第2の基準クロック信号を分周し、クロック信号を生成する第2の分周回路と、を有するクロック生成回路を半導体装置に搭載する。

(もっと読む)

PRI測定装置およびこれを用いたPRI測定方法

【課題】 利用者による手動操作及び画面目視によりパルス列信号のPRIを高精度に測定する。

【解決手段】 測定器本体に設けられた入力端子部と、この入力端子部を介して入力されたパルス列信号のパルス波形を表示する表示部と、この表示部に表示されるパルス波形の表示周期を制御する基準パルス信号を出力する基準信号発生部と、この基準パルス信号発生部から出力された基準パルス信号が入力され、その入力された基準パルス信号の発生周波数に基づいて前記表示部に表示されるパルス列信号の表示データを生成する表示制御部と、この表示制御部により生成された表示データに基づき表示されるパルス波形の表示周期が前記入力端子部を介して入力されたパルス列信号のパルス繰り返し周期と同じになるように前記基準信号発生部に基準パルス信号の発生周波数を指示する操作部とを備えた。

(もっと読む)

入力回路

【課題】入力レベルに対してヒステリシス特性を持たせる。

【解決手段】第1トランジスタM1は、ソースが接地端子P2に接続され、ゲートに入力デジタル信号S1が入力される。第2トランジスタM2は、ソースが電源端子P1に接続され、そのドレインが第1トランジスタM1のドレインに接続される。第2トランジスタM2はデプレッション型で構成する。第1インバータ12は、第1トランジスタM1、第2トランジスタM2の接続点P3、すなわちドレイン電位Vxを反転し、第2トランジスタM2のゲートに出力する。入力回路10は、接続点P3のドレイン電位Vxに応じたレベルを出力する。

(もっと読む)

PLL回路

【課題】入力信号の断、回復状態でも出力の周波数変動を抑制し、周波数精度を維持するPLL回路の提供。

【解決手段】入力を所望周波数に分周する第1分周手段3と、電圧制御発振器7出力を所望周波数に分周する第2分周手段8と、前記第1分周手段3出力と前記第2分周手段出力8間の第1位相比較手段4と、前記第1分周手段3出力と前記第2分周手段8出力の反転の一方の第1選択手段11と、前記第2分周手段8出力と前記第1選択手段11出力間の第2位相比較手段12と、前記第1位相比較手段4出力と、前記第2位相比較手段12出力の一方の第2選択手段6と、入力信号監視手段9と、前記入力信号監視手段9からの監視結果に対して一定時間のタイミングを生成するタイミング生成手段10と、を備え、前記第1選択手段11及び前記第2選択手段6は、前記タイミング生成手段10からの信号状態に従って選択する。

(もっと読む)

半導体装置

【課題】テスト中に所望の位相に対して追随できるテスト回路を備え、安価にDDRifのテストを行うことを目的としている。

【解決手段】本発明における半導体装置は、位相シフト量を決定するDLL200と、テストモード時に所定位相ずらす演算回路300と、位相シフト量を設定するレジスタ11〜16と、設定した位相にシフトして信号の送受信を行う伝送回路10とを備える。伝送回路10は、第1の信号を設定した位相にシフトする位相シフタ1と、テストモード時に第1の信号をループバックする双方向バッファ21と、双方向バッファ21から出力された信号の位相をシフトする位相シフタ2と、第3の信号の位相をシフトする位相シフタ3と、テストモード時に第3の信号をループバックする双方向バッファ22と、双方向バッファ22から出力された信号の位相をシフトする位相シフタ4と、位相シフタ2,4の出力信号を取り出すFIFO30とを備える。

(もっと読む)

41 - 60 / 122

[ Back to top ]