Fターム[5J039MM00]の内容

パルスの操作 (9,993) | 目的、機能 (1,546)

Fターム[5J039MM00]の下位に属するFターム

電圧変動に対する補償 (54)

温度変化に対する補償 (49)

高速化 (185)

低消費電力化 (218)

出力パルス幅の制御 (94)

出力パルス波高値の制御 (17)

ノイズ対策 (207)

ジッタの除去 (43)

点検、監視 (131)

パルスの欠落対策 (8)

ジッタ、歪の付加 (41)

表示 (3)

フェイルセーフ (23)

その他 (351)

Fターム[5J039MM00]に分類される特許

81 - 100 / 122

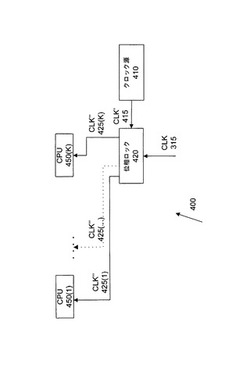

マルチセルコンピューティングシステムにおけるクロック分配

【課題】マルチセルコンピューティングシステムにおけるクロック分配を実現する。

【解決手段】

本発明に係るシステムは、複数のプロセッサを有する複数の処理セルを備える。処理セルは、a)抽出されたクロックが複製されて、それぞれが処理セルのプロセッサに供給される複数のクロックを提供することと、b)抽出されたクロックが、クロック源と共に位相情報として使用されて、処理セルのプロセッサに供給される複数のクロックを提供することとの少なくとも1つで使用される、抽出されたクロックを受信する。抽出されたクロックは、データと結合され、少なくとも2つの処理セルがスイッチを介して互いに通信することを可能にするリンクにより処理セルへ送信された、符号化されたクロックから抽出される。

(もっと読む)

浮遊抵抗体ラダーを用いたインバータベースのフラッシュA/D変換器

【課題】低消費電力などのインバータベースのフラッシュADCの特徴を保有する一方、インバータのサイズまたはパラメータを変えないでインバータ不整合を指示するフラッシュADCを持つことが望まれる。

【解決手段】アナログ信号をデジタル信号に変換するA/D変換器であり、複数の比較器を含む比較器アレーと、直列に接続された複数の抵抗を含む抵抗列と、抵抗列に流れる一定の電流を与えるための電流発生器とを備え、前記比較器の各々は第1のインバータおよび第1のインバータと直列に接続された第2のインバータを含み、前記抵抗器の各々は複数の比較器の1つに対応することを特徴とする。

(もっと読む)

状態検出回路及び発振停止検出装置

【課題】 従来の発振停止検出回路は、クロック信号が何ら停止していないにも拘わらず、通常用電源電圧及び予備用電源電圧の切り替えにより、瞬間的に、クロック信号が停止している旨が出力されるという問題があった。

【解決手段】 本発明に係る発振停止検出回路は、インバータ回路と、1段目、2段目のトランジスタと、第1、第2のコンデンサと、抵抗器と、相互に並列接続された第1、第2のトランジスタと、通常用電源電圧の入力及び予備用電源電圧の入力を選択的に受け、第1のトランジスタの入力端に、通常用電源電圧の入力を受けるとき定電圧を出力し、予備用電源電圧の入力を受けるとき予備用電源電圧を出力する定電圧生成回路とを含む。

(もっと読む)

クロック回路

【課題】 貫通電流を防止するクロック回路を提供すること。

【解決手段】 クロック信号供給回路10と、これに接続された論理ゲートAND1及びAND2と、これに接続された複数段のクロックドライバ回路B2〜B11と、最終段に接続されたクロック信号被供給回路13〜18と、論理ゲートAND1及びAND2に制御信号を入力する制御回路11及び12とを備えている。クロックドライバ回路B1〜B11は、ともにCMOSインバータ回路構成の第1のインバータ回路INV1及びINV2と、振幅制御回路CT1とで構成されている。第1のインバータ回路INV1は、基板に高電位側電源電圧VDDよりも高い電圧が印加されるp型FET(P1)を具備している。振幅制御回路CT1は、2つのn型FET(N3及びN4)で構成されている。

(もっと読む)

パルス信号測定装置及び方法

【課題】パルス信号の入力及びオーバーフローの双方について割り込み信号を発生するタイマを用いてパルス信号の幅や周期を正確に測定可能なパルス信号測定方法を提供する。

【解決手段】リロードレジスタへリロードすると共に割り込み信号を出力し、カウント値がオーバーフローした場合にはリロードレジスタへリロードせずに割り込み信号を出力すると共にオーバーフローフラグをオン状態にするタイマを用いてパルス幅又は周期を測定する際に、割り込み信号を受けてリロードレジスタのカウント値を読み出し(ステップST1)、タイマのオーバーフローフラグの状態を判別し(ステップST2)、オーバーフローフラグがオンしている場合に、リロードレジスタから読み出した今回値と前回値との比較に基づいてパルス信号の入力の有無を判断する(ステップST6)。

(もっと読む)

比較器

【課題】比較器を提供する。

【解決手段】本発明は、第一の入力端子と第二の入力端子、第一の出力端子と第二の出力端子、第一の入力インバータと第二の入力インバータ、第一のロードインバータと第二のロードインバータ、及び、第一のロードインバータと第二のロードインバータの入力端子にそれぞれ第一のバイアス電圧と第二のバイアス電圧を印加するバイアス制御回路を含む比較器を提供する。

(もっと読む)

データスライサ

【課題】入力信号を適切にスライス可能なデータスライサを実現する。

【解決手段】現在の入力電圧信号の最大値と最小値とだけではなく、入力電圧信号に含まれるヘッダパターンにおける平均電圧と、ヘッダパターン検出完了時のピーク電圧・ボトム電圧とにも基づいて、スライスレベルを算出する。具体的には、スライスレベルをS15、ヘッダパターンの平均電圧をS6、ヘッダパターン検出完了時のピーク電圧をS7、ヘッダパターン検出完了時のボトム電圧をS8、最大電圧検出・保持部に保持された最大電圧をS10、最小電圧検出・保持部に保持された最小電圧をS11として、スライスレベルの電圧値を、S15=S6+(S10+S11)/2−(S7+S8)/2と算出する。

(もっと読む)

CMOSラッチ式コンパレータ

【課題】 CMOSラッチ式コンパレータのラッチ回路で使用するMOSトランジスタの数を少なくし、その回路構成をより簡素化できるようにする。

【解決手段】 定電流源を構成するバイアス用MOSトランジスタMB2a,MB2bと、差動対を構成する一対のMOSトランジスタであって、それぞれのゲートにコンパレータ回路1の出力電圧VO+,VO-が印加されるように成された入力信号用MOSトランジスタM5a,M5bと、たすきがけ結合対を構成する一対のMOSトランジスタであって、定電流源MB2a,MB2bと差動対M5a,M5bとの間に直列に接続されたスイッチ用MOSトランジスタM4a,M4bとによりラッチ回路2を構成することにより、ラッチ回路2の状態の切り替えを差動対を成す一対の入力信号用MOSトランジスタM5a,M5bのみで行うことができるようにする。

(もっと読む)

同期回路

【課題】 リセット端子を持たない1:nDEMUXやn:1MUXの複数個を同期させて並列動作させることが可能な同期回路を実現する。

【解決手段】 クロック信号を入力して作動する複数のカウンタIC手段の動作タイミングを一致させる同期回路において、前記複数のカウンタIC手段のうち、基準となるカウンタIC手段のクロック信号と同期対象となる他のカウンタIC手段のクロック信号との位相差を検出する位相差検出手段と、検出された前記位相差に基づいて前記他のカウンタIC手段のクロック信号の位相を制御する位相制御手段と、を備える。

(もっと読む)

クロック補正回路及びクロック補正方法並びにマイクロコントローラ

【課題】

ソフトウェア上の処理が簡略化され、コストの低減を図ることが可能なクロック補正回路を提供すること。

【解決手段】

本発明に係るクロック補正回路は、メインクロックAと、メインクロックAよりも周波数が低いサブクロックBとが入力され、メインクロックAの周波数の誤差を補正して出力するクロック補正回路であって、サブクロックBの1周期に含まれるメインクロックAのパルス数をカウントするパルス数カウンタ201と、パルス数カウンタ201がカウントしたパルス数と予め定められた基準パルス数とを用いて補正情報を算出する演算部203と、補正情報に基づいてクロック補正信号を出力する休止信号カウンタ204と、クロック補正信号に基づいてメインクロックAの出力を補正するゲート205とを有する。

(もっと読む)

半導体集積回路

【課題】 クロックスキューを低減し、動作マージンを十分に確保することが可能な半導体集積回路を提供する。

【解決手段】 遅延回路8による遅延時間DL1とクロックツリー11による遅延時間DL11との和が、遅延回路9による遅延時間DL2とクロックツリー12による遅延時間DL12との和と等しくなるように、遅延回路8,9の遅延時間DL1,DL2が調整される。このように、予め任意に遅延時間をプログラムすることができるプログラマブル遅延回路8,9を設けたことによって、機能ブロック3,4に供給される内部電源電圧V1,V2の差が大きい場合でも、機能ブロック3,4間のクロックスキューを低減することができる。したがって、低消費電力の半導体集積回路において、クロックスキューを低減することができ、動作マージンを十分に確保することが可能になる。

(もっと読む)

チョッパ増幅回路

【課題】回路構成が簡単であって、しかも高い信頼性を有し、低電圧で動作可能なチョッパ増幅回路を提供する。

【解決手段】チョッパ変調器1は入力信号を所定の制御信号に従ってチョッパ変調してチョッパ変調信号を出力する。スイッチドオペアンプ3の増幅回路はチョッパ変調器1から出力されるチョッパ変調信号を増幅して増幅されたチョッパ変調信号を出力する。スイッチドオペアンプ3のチョッパ復調器4は増幅回路から出力される増幅されたチョッパ変調信号を、制御信号に従ってチョッパ復調して復調された出力信号を出力端子からチョッパ増幅された出力信号として出力する。チョッパ変調器5はチョッパ復調器4から出力される復調された信号を、制御信号に従ってチョッパ変調してチョッパ変調信号を増幅手段の入力端子に出力する。

(もっと読む)

クロックジェネレータ

【課題】 チャージポンプ回路の出力電圧変動を抑制する。

【解決手段】 PLL回路1は、位相比較器2、チャージポンプ回路・LPF部3、VCO4、及び分周器5から構成され、チャージポンプ回路・LPF部3には、チャージポンプ回路6の充電電流及び放電電流を同一にするための補正チャージポンプ電流をチャージポンプ回路6に供給するチャージポンプ電流補正回路9が設けられている。

(もっと読む)

入力装置とそれを構成する半導体装置

【課題】カスケード接続された複数のICのクロック信号線にアナログフィルターを挿入することなく、静電気ノイズによる誤動作を防止構成できるようにする。

【解決手段】複数の外部信号入力手段P11と外部信号入力手段P11と読み出し線との間にそれぞれ接続されたスイッチS11を有し、スイッチを導通させることにより外部信号入力手段P11より読み出し線に出力する外部入力部I11と、外部クロック信号CLK0に同期して外部制御信号を順次シフト入力したシフトデータに応じてスイッチS11からS13が導通するように出力するシフトレジスタSE1と、シフトレジスタSE1から出力された外部制御信号O1を外部へ出力する出力回路SO1とを有する半導体装置IC1において分周回路D11で、外部クロック信号CLK0を分周して内部クロック信号CLK11を生成し内部クロック信号CLK11に同期して外部制御信号を外部へ出力回路SO1を用いることでデータのズレを低減するようにした。

(もっと読む)

パルス信号再生装置

【課題】パルス信号に含まれるノイズを除去するパルス信号再生装置において、再生パルスにおいても、アサートエッジを保存できるようにする。

【解決手段】RS−FF10と、入力パルス信号に含まれるノイズを監視するボローパルス生成部200を備えたリセット信号生成部20とを設ける。入力パルス信号がアサートされたときにはRS−FF10をセットし、この後に、ボローパルス生成部200においてノイズの有無の監視を開始する。ノイズが存在せずにノイズ除去対象期間経過したときには、RS−FF10をリセットする。パルス信号のアサートエッジを起点として、再生パルスのアサートエッジを生成し、ノイズがなくノイズゲート期間以上経過した後に再生パルスのネゲートエッジを生成するので、パルス信号にノイズが重畳していた場合でも、アサートエッジの発生タイミングを維持しつつノイズを除去したパルス信号を再生することができる。

(もっと読む)

半導体装置の遅延調節回路、及び遅延調節方法

【課題】動作条件の変化による遅延時間を検出し、この遅延時間を一定範囲内に入るように調節可能な遅延調節回路が開示される。

【解決手段】遅延調節回路は、遅延検出回路、第1パルス発生器、カウンタ制御回路、及びnビットカウンタを備える。遅延検出回路は、出力信号に応答して入力信号を第1時間遅延させ、入力信号と遅延した入力信号とを互いに比較し、第1信号を発生させる。第1パルス発生器は、入力信号に応答して第2信号を発生させる。カウンタ制御回路は、第1信号と第2信号とに応答してカウントアップ信号とカウントダウン信号とを発生させる。nビットカウンタは、カウントアップ信号とカウントダウン信号に応答して第1時間を2n(nは自然数)区間に分けるためのデジタル出力信号を発生させる。従って、遅延調節回路は、半導体製造工程、温度、電圧などの条件が変化しても遅延時間を一定範囲内に入るように調節することができる。

(もっと読む)

タイミング発生回路

【課題】 微小遅延部で発生させる遅延量を精密に制御することができるタイミング発生回路を得る。

【解決手段】 直列接続した粗遅延部及び微小遅延部と、粗遅延部に電源電圧を供給する第1のDLLと、微小遅延部に電源電圧を供給する第2のDLLとを設ける。そして、第1のDLL内のモニタ回路として用いる遅延部を粗遅延部と同じ回路形式とする。また、第2のDLL内のモニタ回路として用いる遅延部を微小遅延部と同じ回路形式とする。

(もっと読む)

個々のパルスの調節可能な開始時点および終了時点を有するパルス列を形成する方法とパルス発生器

【課題】個々のパルスの調節可能な開始時点および終了時点を有するパルス列を形成する改善された方法を提供する。

【解決手段】第1のクロック信号および第2のクロック信号それぞれ1つずつからなる組を提供し、1つの組の第1のクロック信号および第2のクロック信号の特性からタイミングベクトルに従い部分パルスを形成し、パルス列を部分パルスの重畳によって形成する。

(もっと読む)

信号伝達回路

【課題】 コストダウンの障害となるLDMOS(Laterally Diffused Metal Oxide Semiconductor)の使用数を削減しコストダウンを図れる信号伝達回路を提供する。

【解決手段】 低電位の回路において、パルス発生器11aは信号入力端HINから入力した信号の正負のエッジを検出し、それぞれのエッジを表すパルス信号をスイッチング素子Q1〜2に出力する。スイッチング素子Q1〜2は電流源Ires1〜2をオン/オフし、LDMOSQ3を介して高電位の回路において、抵抗R3に電流を供給する。抵抗R3は電流地に応じた電圧を両端に発生し、異なる閾値を有するインバータInv1〜2によって、低電位の回路にて入力された信号の正負のエッジが復元され、パルス検出回路12a、RS(Reset-Set)フリップフロップ13、スイッチング素子Q5〜6、抵抗R13〜14によって、入力された信号が復元される。

(もっと読む)

遅延同期ループ及びこれを具備した半導体メモリー装置

【課題】 互いに異なる位相を有した複数個のクロック信号を発生することができる遅延同期ループを提供する。

【解決手段】 クロック信号とフィードバッククロック信号との位相差を検出し、前記位相差によって変化する複数ビットの遅延制御信号を発生する位相検出器12と、前記複数ビットの遅延制御信号に応答して前記クロック信号を遅延させて複数個の出力クロック信号及び前記フィードバッククロック信号を発生する所定個数の縦続接続された第1の遅延セルを具備する第1の遅延器18と、前記複数個の遅延制御信号に応答して反転クロック信号を遅延させて複数個の反転出力クロック信号を発生する所定個数の縦続接続された第2の遅延セルを具備する第2の遅延器22と、前記複数個の出力クロック信号及び前記複数個の反転出力クロック信号の中で関連があるクロック信号を位相混合して補正された複数個の出力クロック信号を発生する位相混合器24とを含む。

(もっと読む)

81 - 100 / 122

[ Back to top ]