Fターム[5J039MM00]の内容

パルスの操作 (9,993) | 目的、機能 (1,546)

Fターム[5J039MM00]の下位に属するFターム

電圧変動に対する補償 (54)

温度変化に対する補償 (49)

高速化 (185)

低消費電力化 (218)

出力パルス幅の制御 (94)

出力パルス波高値の制御 (17)

ノイズ対策 (207)

ジッタの除去 (43)

点検、監視 (131)

パルスの欠落対策 (8)

ジッタ、歪の付加 (41)

表示 (3)

フェイルセーフ (23)

その他 (351)

Fターム[5J039MM00]に分類される特許

21 - 40 / 122

半導体装置

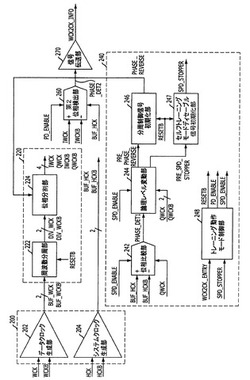

【課題】高速の半導体装置で要求されるクロック整列トレーニング動作を提供すること。

【解決手段】システムクロック及びデータクロックを入力されるクロック入力部(200)と、データクロックの周波数を分周して所定の位相差を有する複数の多重位相データ分周クロックを生成し、分周制御信号に応答して多重位相データ分周クロックの位相の反転可否を決定するクロック分周部(220)と、多重位相データ分周クロックのうち所定の第1選択クロックの位相を基準としてシステムクロックの位相を検出し、その結果に対応して分周制御信号のレベルを決定する第1位相検出部(240)と、多重位相データ分周クロックのうち所定の第2選択クロックの位相を基準としてシステムクロックの位相を検出し、その結果に対応してトレーニング情報信号を生成する第2位相検出部(260)と、トレーニング情報信号を外部に伝送するための信号伝送部(270)とを具備する。

(もっと読む)

入力インターフェース回路

【課題】有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供すること。

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

(もっと読む)

データ取込保持装置

【課題】入力データの取り込みを誤りなくできるデータ取込保持装置を提供する。

【解決手段】パルス発生手段20からのラッチ用パルスPLSのパルス幅区間で入力データを取り込んで保持する第1のデータ取込記憶部を備える保持手段を備える。パルス発生手段20は、第1のデータ取込記憶部と同じあるいは同等の構成の第2のデータ取込記憶部231を備え、クロック信号CLKから、第2のデータ取込記憶部231における入力データの取込時間分のパルス幅区間のパルス信号PLSを生成し、ラッチ用パルスとして、第1のデータ取込記憶部に供給する。

(もっと読む)

信号中継回路、信号中継装置及び信号中継方法

【課題】回路の誤作動を防止することができる信号中継回路、信号中継装置及び信号中継方法を提供すること

【解決手段】本発明にかかる信号中継回路は、2つの入力信号の電圧差に基づいて差動信号を生成する差動信号受信回路41と、差動信号受信回路41に入力される2つの入力信号の電圧差の有無を検出する電圧差検出回路42と、電圧差検出回路42により電圧差が検出されない場合には、所定の値を有する信号を出力し、電圧差検出回路42により電圧差が検出される場合には、差動信号受信回路41により生成された差動信号を出力する差動信号出力回路43と、を備えるものである。

(もっと読む)

オーバーサンプリング回路

【課題】オーバーサンプリング型CDR回路で用いる多相クロックの相互の位相差が等間隔になるように高精度に位相を補正できるオーバーサンプリング回路を提供する。

【解決手段】多相クロックを生成する多相クロック生成部200と、多相クロックの位相差を検出して、該検出結果に基づいて位相制御信号を発生する位相制御部205と、多相クロックの本数分の遅延回路を有し、多相クロックをそれぞれの遅延素子に入力された信号の通過時間を、位相制御信号に基づいて調整することで多相クロック間の位相差を調整する位相調整部203と、を備え、各遅延回路300は、直列に接続されたサイズの異なる複数のインバーターと、該複数のインバーターの後段に接続したインバーターと、からなり、複数のインバーターから選択される一つインバーターの出力抵抗と、後段に接続したインバーターの入力容量の積に基づいて通過時間を調整する。

(もっと読む)

ビット配列入れ替え半導体回路

【課題】基板上で接続されたマイコンとROM、RAMのデータのやりとり及びROM、RAMの内容を解析しづらくする。

【解決手段】

基板上で接続されたマイコンとROM、RAMを接続するデータバスに、スイッチング素子1を配置したビット配列入替回路を設け、アドレスバスの一部と、RAMまたは電気的に書き換え可能なROMとして実現されるメモリ3の内容を用いて、組み合わせ回路であるビット配列入替スイッチ駆動回路2により各スイッチング素子1のオンオフを決定することにより、データバスのビット配列の入替を行う。

(もっと読む)

改善された分解能を有する時間デジタル変換器(TDC:TIME−TO−DIGITALCONVERTER)

【解決手段】一つのインバータ遅延より小さいインバータ遅延の高分解能を含む時間デジタル変換器(TDC)が記載されている。デザイン例において、TDCは、第1及び第2の遅延パス、遅延ユニット、及び位相演算ユニットを含んでいる。第1の遅延パスは、第1の入力信号及び第1の参照信号を受信し、第1の出力を供給する。第2の遅延パスは、第2の入力信号及び第2の参照信号を受信し、第2の出力を供給する。遅延ユニットは、例えば半分のインバータ遅延によって、第1の入力信号に対して第2の入力信号を遅延する、または第1の参照信号に対して第2の参照信号を遅延する。位相演算ユニットは、第1及び第2の出力を受信し、入力信号及び参照信号間の位相差を供給する。構成は、前記第1及び第2の遅延パスについての正確なタイミングを得るために実行され得る。 (もっと読む)

インピーダンス調整回路及びこれを備える半導体装置

【課題】インピーダンス調整回路における調整誤差を低減する。

【解決手段】レプリカ回路1441,1443のインピーダンスをそれぞれ変化させるカウンタ回路1421,1422と、これらカウンタ回路のカウント値を更新するインピーダンス調整制御回路141とを備える。制御回路141は、レプリカ回路1441のインピーダンスが外部抵抗REのインピーダンスよりも低い状態から高い状態に変化したことに応答してカウンタ回路1421のカウント値更新を終了し、レプリカ回路1443のインピーダンスがレプリカ回路1441のインピーダンスよりも高い状態から低い状態に変化したことに応答してカウンタ回路1422のカウント値更新を終了する。これにより、レプリカ回路1441,1443にて生じる調整誤差が相殺される。

(もっと読む)

PLL回路

【課題】感度関数と相補感度関数の両方が低減されたPLL回路を提供する。

【解決手段】本発明のPLL回路10は、一般的なPLL回路の構成を備えた第1ループ50と、相補感度関数を低減するための第2ループ52とを備えて構成されている。第1ループ50では、周波数が高い基準クロック34を用いて比較部14にて位相比較を行うことにより、感度関数を下げている。そして、第2ループ52からの出力により電流補償部16にて電流値を補完することにより、相補感度関数を下げている。

(もっと読む)

半導体集積回路

【課題】エラー検出のためのハードウエア上のオーバーヘッド及び時間的オーバーヘッドを小さくでき、且つエラーを発生した論理素子を特定できる半導体集積回路を提供することを第1目的とする。また、ダイナミック回路のリセット時間による時間的オーバーヘッドを隠蔽でき、実効的な演算スループットを向上させる半導体集積回路を提供することを第2目的とする。

【解決手段】本発明に係る半導体集積回路は、論理素子単位でのハンドシェークを実施し、論理素子単位でのエラー発生の検出を行うことで後段の論理素子にエラー伝搬を行わないこととした。さらに、本発明に係る半導体集積回路は、各論理素子内で同一の論理回路を並列に接続し、2相で動作させることとした。

(もっと読む)

デューティ感知回路およびこれを備えるデューティ補正回路

【課題】デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供すること。

【解決手段】本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、前記出力クロックのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、前記差異値を累積して前記デューティ調節コードを生成する累積部130とを備える。

(もっと読む)

クロック信号供給回路の設計方法、情報処理装置およびプログラム

【課題】半導体集積回路におけるクロック信号の供給において、回路全体を通しクロックラインを短縮し得る構成を提供することを目的とする。

【解決手段】回路素子のグループ間で回路素子の交換、移動を実行し、当該実行の前後でグループごとに回路素子の位置と中心位置との距離の合計し更に全グループについて合計した値が減少する場合には当該実行後のグループを維持し減少しない場合には当該実行前のグループを維持する最適化を実行する構成である。

(もっと読む)

半導体装置及びその制御方法

【課題】半導体装置の製造ばらつきや経年劣化に起因するクロックスキューを補正することができる半導体装置を提供する。

【解決手段】スキュー検出部6は、スキューを検出するための少なくとも1個のクリティカルパス7又はレーシングパス7を含む。クロック調整部5は、スキュー検出部6により検出されたスキューに基づいて、ディレイの設定値を設定する。クロックセル4は、ディレイの設定値に応じて、第1のクロックのディレイを調整して、第2のクロックとして出力する。

(もっと読む)

信号再生回路向け位相比較回路及び信号再生回路向け位相比較回路を備える光通信装置

【課題】 1/Nレート構成に対応可能な高精度な位相比較回路を得る。

【解決手段】それぞれ、N相クロック信号CLKの各クロック信号を、受信データ信号DINの立ち上がりに同期してトラックホールドするN個のトラックホールド回路を備える。これらのN個のトラックホールド回路の出力から、受信データ信号DINの立ち上がりエッジが、クロック信号CLKの立ち上がりエッジに位置しているクロック信号をトラックホールドしているもののみをセレクタで選択して、位相差信号として出力する。

(もっと読む)

半導体集積回路

【課題】クロック信号の位相、デューティー比等の変動に対し耐性の強い、小型の半導体集積回路を提供する。

【解決手段】複数配設される回路部と、クロック信号の立ち上がりエッジから前記クロック信号を逓倍した周期の第1信号を生成する第1カウンタと、前記クロック信号の立ち下がりエッジから前記クロック信号を逓倍した周期の第2信号を生成する第2カウンタと、前記第1信号が転送される第1ラインと、前記第2信号が転送される第2ラインと、前記第1ライン及び前記第2ラインと接続され前記第1信号と前記第2信号との位相差から第3信号を生成し前記回路部に前記第3信号を出力する位相比較器と、を備え、前記位相比較器は、前記第1ライン及び前記第2ライン上に配設され且つ前記第1ライン及び前記第2ラインの末端と前記回路部との間に複数配設される。

(もっと読む)

クロック信号生成装置

【課題】本発明は、温度特性、電源電圧特性、個体バラツキを吸収し、最適なノンオーバーラップ時間を有する2相クロック信号を確実に生成できる信頼性の高いクロック信号生成装置を提供することを目的とする。

【解決手段】本発明のクロック信号生成装置は、ノンオーバーラップクロック信号を使用する負荷回路において使用される2相クロック信号の遅延時間を可変する可変遅延器と、2相クロック信号におけるHレベル区間のノンオーバーラップ時間を検出し、ノンオーバーラップ時間に応じた検出信号を出力するノンオーバーラップ検出器と、ノンオーバーラップ検出器からの検出信号に基づいて可変遅延器を制御する制御信号を生成する制御信号生成部と、を備えている。

(もっと読む)

DDS回路及び電子装置

【課題】 チューニングワードのビット長を増加させずに、分解能を向上させ得るDDS回路及び電子装置を提供することを目的とする。

【解決手段】 リファレンスクロックの周波数に基づいて、チューニングワードから正弦波の信号を出力するDDS部11と、リファレンスクロックの周波数を分周する分周器12aと、DDS部11で出力された正弦波の信号の周波数を分周する分周器12bと、分周器12aで分周された周波数と分周器12bで分周された周波数とを合成した合成周波数を備える正弦波の信号を出力するミキサ12cと、を有することを特徴としている。

(もっと読む)

相補信号生成回路

【課題】 容量素子のみによるこれまでのスキュー調整方法よりもスキューの微調整を可能にした相補信号生成回路を提供する。

【解決手段】 本発明による相補信号生成回路は、複数のインバータ(901、904、905、906)を含む第1の信号伝達経路と、インバータ(901、907、908)と抵抗素子903を含む第2の伝達経路とを有する。

(もっと読む)

IQ信号発生器のためのスワップ機能を実施するためのシステム及び方法

【課題】IQ信号発生器に対してスワップ機能を実施するためのシステム及び方法を提供する。

【解決手段】IQ信号発生器を実施するためのシステム及び方法は、クロック入力信号に応答してI信号を発生するマスターラッチ、及び反転クロック入力信号に応答してQ信号を発生するスレーブラッチを含む。マスターセレクタが、マスターラッチからスレーブラッチへの通信経路を形成するように構成され、スレーブセレクタが、スレーブラッチからマスターラッチへのフィードバック経路を形成するように構成される。上述のI及びQ信号は、いかなる介在電子回路もなしにそれぞれマスター及びスレーブラッチから直接出力される。

(もっと読む)

位相制御回路

【課題】 データ信号とクロック信号がどのような位相差であっても位相差に応じたパルス幅の位相差信号を出力する。

【解決手段】 データ信号および反転した信号Yを入力し、反転した信号Yをデータ信号の遷移タイミングで保持して信号Xを出力する第1の保持手段と、クロック信号および信号Xを入力し、信号Xをクロック信号の遷移タイミングで保持して信号Yを出力する第2の保持手段と、信号Xおよび信号Yを入力し、その位相差に応じたパルス幅を有する位相差信号を生成し、データ信号とクロック信号の位相差に応じたパルス幅を有する位相差信号として出力する比較手段とを備える。

(もっと読む)

21 - 40 / 122

[ Back to top ]