Fターム[5J106CC01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 発振回路、VCO (2,067)

Fターム[5J106CC01]の下位に属するFターム

アナログ発振回路 (130)

パルス・クロック発振回路 (169)

マイクロ波・分布定数発振回路 (4)

注入同期発振回路 (18)

原子発振器 (149)

掃引周波数発振回路 (4)

掃引電圧発振(発生)回路 (7)

基準発振回路 (165)

局部発振回路 (38)

予備発振回路 (1)

複数の発振回路・VCO (166)

Fターム[5J106CC01]に分類される特許

121 - 140 / 1,216

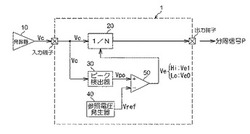

分周回路及び集積回路

【課題】分周器の発振を防止する分周回路を提供する。

【解決手段】クロック信号Vcを所定の分周比にて分周する分周器20を備え、分周器の発振を防止する分周回路1であって、クロック信号のピーク電圧Vcpを検出してピーク値を保持するピーク検出器30と、分周器が正常動作するために必要なクロック信号の振幅vpに対応した参照電圧Vrefを出力する参照電圧発生器40と、ピーク検出器により検出されたピーク値と参照電圧とを比較する比較器50と、を備え、分周器に分周開始を指示する制御信号を入力する制御端子を備え、制御端子に比較器の出力信号Veを接続し、ピーク値が参照電圧を超えたときに、比較器は、分周器の制御端子に分周開始を指示する制御信号を出力する

(もっと読む)

信号処理回路

【課題】内部回路の内部クロックと内部回路の入力信号との位相関係により内部回路の出力が変動する場合であっても、安定した回路動作とすることができる信号処理回路を得る。

【解決手段】入力信号と位相制御信号とを受け、前記入力信号及び前記位相制御信号の位相差に基づき位相比較信号を出力する位相比較手段と、前記位相比較信号を受け、前記位相比較信号に基づく周波数で発振する発振信号を出力する発振手段と、前記発振信号を受け、前記位相制御信号を出力する位相制御信号発生手段とを備え、同時に前記位相制御信号を出力信号とし、該位相制御信号を内部クロックとして供給することを特徴とする位相差制御回路である信号処理回路等を提供する。

(もっと読む)

デジタル位相同期ループ回路

【課題】TDC(Time−to−DigitalConverter)の回路規模を拡張することなく、デスキュー用途に用いることが可能であるADPLLの構成の提供。

【解決手段】DCO19と、FREFを分周するMDIV11と、DCOの出力FOを分周するPDIV20と、PDIVの出力FOUTを分周するNDIV12と、MDIVの出力信号FRとDCOの出力FOの位相差を測定するTDC13と、NDIVの出力FDとFOの位相差を測定するTDC14と、FRでFOをサンプルするFF15と、FRとFDのうち位相が先行するパルスと次のパルスのエッジの期間、FOをカウントするCONT17と、TDC13、14、FF15の出力を入力し、カウンタの出力を受け、FRとFDの位相差を演算するPERR16と、PERRの出力を入力し、フィルタ処理した信号をDCOに供給するDFIL18を備える。

(もっと読む)

フェーズロックドループの方法及び装置

【課題】2点変調を採用するフェーズロックドループを用いた通信システムを提供する。

【解決手段】フェーズロックドループは、位相検出器106の第1の入力に動作可能に接続された出力を有する主発振器100、位相検出器106の第2の入力に動作可能に接続された出力を有する従発振器102、及び位相検出器106の生誤り端末に動作可能に接続されたフォワード利得適応モジュールを含む。フォワード利得適応モジュールは、位相検出器106の生誤り端末と動作可能に接続された、フォワード利得適応モジュールの可変利得増幅器200と、前記フォワード利得適応モジュールの可変利得増幅器200と前記従発振器102とに動作可能に接続された、フォワード利得適応モジュールの積分器202とを具備する。

(もっと読む)

位相同期ループ回路

【課題】必要な特性を満たしつつ、回路構成を簡素化し、省面積化を可能とするデジタルPLLの提供。

【解決手段】リファレンスクロック信号FRと分周クロック信号FDの位相差を検出するTDC101、FDとFRの進み遅れを出力するFF103、位相誤差演算器102、位相誤差(PERR)を平滑化するデジタルフィルタ104、出力クロック信号FOを出力するDCO105、FOを分周したFDを出力するN分周器106、N分周器106内のカウンタ値をFRに応答してサンプルするレジスタ107を備え、TDC101は、位相差検出測定範囲がFOの1周期以内とされ、FRとFDの位相差をFOの1周期に換算した小数で出力し、位相誤差演算器102は、FDとFRの位相差が、FOの周期の整数倍以上のときは、レジスタ107出力と符号情報signから、FOの1周期内のときは、TDCの出力と符号情報signからPERRを演算出力する。

(もっと読む)

PLLシンセサイザ

【課題】温度補償ループフィルタのキャパシタの容量値を小さくする。

【解決手段】PLLシンセサイザは,位相比較器PDと,ループフィルタLFと,電圧制御発振器VCOとを有する。さらに,温度補償ループとして,周波数制御電圧が制御電圧範囲から外れたときに比較信号30を出力する比較器CMPと,比較信号30を積分してMビットの第1のデジタル信号32を生成するデジタルフィルタDFと,第1のデジタル信号32を入力し,前記Mビットより少ないNビットで、前記第1のデジタル信号32に対応する第2のデジタル信号34を生成するΣΔ変調器12、10と,第2のデジタル信号34を電流信号36に変換する温度補償チャージポンプCPtと,前記電流信号36を温度補償制御電圧に変換する温度補償ループフィルタTFとを有し,電圧制御発振器VCOは温度補償制御電圧ftに基づいて出力クロックCKoutの周波数を制御する。

(もっと読む)

位相同期回路および無線通信装置

【課題】周波数補正ミスをなくせ、電圧対周波数変換利得Kvcoを低く抑えることが可能で、PLL位相ノイズ設計を緩和できる位相同期回路および無線通信装置を提供する。

【解決手段】キャリブレーション部190は、電圧制御発振器184の出力発振信号の周波数をカウントするカウンタ回路191と、カウンタ回路のカウント結果を保持しておくための第1および第2の記憶回路193,194と、カウンタ回路とターゲット周波数を比較し大小を判定する比較回路195と、比較回路の結果を受けカウンタ回路のカウント結果と第1の記憶回路の保持結果を比較し、電圧制御発振器の容量バンクを制御する制御回路106と、電圧制御発振器にキャリブレーション電圧を生成し与える電圧生成回路197と、カウンタ回路のカウント結果と第1および第2の記憶回路の結果より演算を行い、演算結果に応じて電圧生成回路を制御する処理回路198と、を含む。

(もっと読む)

クロックデータリカバリ回路

【課題】簡易な構成で、データおよびクロック間のタイミングスキューの制約をなくすとともに、データの周波数可変範囲を広くとることができるCDR回路を提供する。

【解決手段】CDR回路は、基準クロック信号を用いてクロック信号を所望の周波数にロックするLTモードと、クロック信号をデータ信号に位相同期させる通常動作モードとを有する。CDR回路は、VCOと、入力信号を平滑化して制御電圧を生成してVCOに出力するLPFと、LTモード時に、基準クロック信号とクロック信号との周波数比較を行ない、該比較結果に応じた信号をLPFに出力する周波数ループと、通常動作モード時に、データ信号とクロック信号との位相比較を行ない、該比較結果に応じた信号をLPFに出力する位相ループと、基準クロック信号の周波数カウント値に応じてVCOに設定する周波数レンジを調整する周波数検出回路とを備える。

(もっと読む)

半導体集積回路

【課題】チップサイズの大型化を防止することができる半導体集積回路。

【解決手段】同一のリセット信号が入力されることにより、互いに同期が取られる複数の送信ブロックを備える半導体集積回路。各送信ブロックは、基準クロック信号とフィードバッククロック信号との位相差に応じた制御電圧に基づいて周期Tの第1のクロック信号を発振する電圧制御発振器と、第1のクロック信号がN(Nは自然数)分周された第2のクロック信号が入力され、当該第2のクロック信号から、第1の送信用クロック信号と当該第1の送信用クロック信号よりも周波数の低い第2の送信用クロック信号とを生成し、リセット信号に応じて少なくとも第2の送信用クロック信号を出力するリセット機能付き分周器と、第1及び第2の送信用クロック信号が分配される複数の送信機と、を備える。

(もっと読む)

多相信号を生成する方法及び回路

【課題】2つの結合されたLCVCOにおいて生じる多相クロック信号の位相誤差を改善し、制御可能な位相オフセットでクロック信号を生成する方法を提供する。

【解決手段】方法は、LCVCOによって第1のLCタンクの共振周波数に基づく第1の位相を有する第1の周期信号を生成するステップと、第2のLCVCOによって第2のLCタンクの共振周波数に基づく第2の位相を有する第2の周期信号を生成するステップと、第1及び第2の周期信号に基づいて第1及び第2のLCタンクの間の位相オフセットを決定するステップと、決定された位相オフセットに基づいて第1及び第2の出力信号を生成するステップと、所定の位相オフセットと略等しくなるよう位相オフセットを調整するステップとを有する。調整ステップは、第1の出力信号に基づいて第1のLCタンクの第1のインピーダンスを変調するステップ、及び/又は、第2の出力信号に基づいて第2のLCタンクの第2のインピーダンスを変調するステップを有する。

(もっと読む)

PLL周波数シンセサイザ、無線通信装置およびPLL周波数シンセサイザの制御方法

【課題】安価な構成とするとともに、性能を向上させることができるPLL周波数シンセサイザ、無線通信装置およびPLL周波数シンセサイザの制御方法を提供する。

【解決手段】PLL周波数シンセサイザは、基準周波数信号と分周信号との位相を比較する位相比較部101からの信号と位相誤差補償信号とに応じて、電流パルス信号を生成するCPDAC102と、電流パルス信号を電圧信号に変換するループフィルタ103と、電圧信号に応じた発振周波数の信号を出力するVCO104と、VCO104からの出力を分周して分周信号として出力する分周器105と、分数分周のための分周比のデータに基づいて、分周比制御信号を生成するデルタシグマ変調器107および加算器106と、分周比のデータから少なくとも2つの位相誤差補償用のデータを生成し、生成したデータを異なるタイミングで利用して、位相誤差補償信号を生成する制御部108とを備える。

(もっと読む)

クロック供給装置およびクロック供給方法

【課題】発振器のウォームアップの完了を容易に判定できるようにする。

【解決手段】クロック供給装置1は、通信装置内の処理に用いられるクロック信号を供給する。発振器1aは、クロック信号を生成する。測定部1bは、通信装置に接続された伝送路から抽出されたリファレンスクロック信号を取得し、クロック信号とリファレンスクロック信号との周波数ずれを測定する。判定部1cは、周波数ずれの測定結果と電力供給の状況とに基づいて、発振器1aのウォームアップが完了したか否か判定する。

(もっと読む)

位相ロックループ回路

【課題】簡素な回路構成で、電圧制御発振回路の入力部でのリークに起因する定常位相誤差を防止できる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号とフィードバッククロック信号の位相差を検出する位相比較回路1と、検出された位相差に応じた電流を容量に出力するチャージポンプ回路2と、容量に蓄積されている電荷に基づく制御電圧に応じた発振周波数の出力クロック信号を生成する電圧制御発振回路4とを有する位相ロックループ回路にて、制御電圧がロック状態時の電圧であった場合に電圧制御発振回路4の入力部に流れるリーク電流に等しい電流を生成し、生成された電流に応じた補正電流をカレントミラー回路を介して容量に出力するようにして、リーク電流による制御電圧の変動を抑制する。

(もっと読む)

全デジタル位相ロックループ

【課題】周波数差の変化を正しくDCOに伝達し、且つグリッチノイズを低減する。

【解決手段】一つの実施形態の全デジタル位相ロックループ90には、デジタル周波数比較器1、グリッチ発生期間検出回路2、グリッチ補正回路3、累積器4、ループフィルタ5、及びDCO6が設けられる。デジタル周波数比較器1には、整数部周波数差生成回路11、小数部周波数差生成回路12、及び加算器13が設けられる。グリッチ発生期間検出回路2は、小数部周波数差生成回路12から出力されるTDC出力信号Stdcoが入力され、グリッチ発生期間信号Sgctimを生成する。グリッチ補正回路3は、加算器13から出力される周波数差信号Sfdif及びグリッチ発生期間信号Sgctimが入力され、グリッチ発生期間信号Sgctimがイネーブル状態のときに周波数差信号Sfdifに含まれるグリッチノイズを低減処理する。

(もっと読む)

周波数シンセサイザ装置及び変調周波数変位調整方法

【課題】2つの変調経路を有する周波数シンセサイザ装置において、DACから電圧制御発振器に出力される制御電圧の振幅を適切に調整することができる。

【解決手段】周波数シンセサイザ装置10は、入力電圧に応じた発振周波数で発振する電圧制御発振器14、電圧制御発振器14からの信号を分周するプログラマブル分周器20、分周信号と基準クロックとの位相差を電圧制御発振器14に出力する周波数位相比較器22、送信データに応じて目標周波数変位分周波数を変位させる場合の調整電圧を電圧制御発振器14に出力するDAC12、調整電圧の校正時に、電圧制御発振器14を基準電圧電源に接続するスイッチ32、任意の送信データをDAC12に出力して発振させた状態で分周信号の周波数をカウントしたカウント値に基づいて、目標周波数変位に対応する調整電圧に対応した調整データを設定する変調周波数変位校正回路30を備える。

(もっと読む)

電圧制御発振回路

【課題】従来のノイズ除去手段にはノイズ原因となる一定の高調波成分を有するパルス信号を一旦生成してから、ノイズ除去のための変調をかける為、ノイズ除去のための変調をかける前の信号がノイズの原因となる。

【解決手段】電圧制御発振回路10を、車両に設置された電子機器に供給する交流電圧を出力する電圧制御発振回路10であって、電圧制御発振回路10は入力信号の電圧に応じた周波数の交流電圧を出力し入力信号は三角波かまたは正弦波であることを特徴とするものとする。

(もっと読む)

リファレンスリークの発生や位相ノイズを低減できるPLL回路

【課題】リファレンスリークを低減することができ、位相ノイズを抑制することができるPLL回路を提供する。

【解決手段】切り替え機能付き周波数位相比較器は、入力されるロック検出信号に基づいて、入力される2つの信号の立ち上がりエッジを検出することにより当該2つの信号の位相差を検出する周波数比較と、入力される2つの信号の電圧レベルを検出することにより当該2つの信号の位相差を検出する位相比較とを切り替えて行う。

(もっと読む)

位相制御装置

【課題】従来のこの種の装置では不可能な伝送路長の大きな変化による位相変動を調整できると同時に、検出精度を高める。

【解決手段】高周波信号である原信号を発生する原発振器1と、制御信号に基づいて原信号の通過時間を調整する移相器2と、原信号が伝送される伝送路3と、位相検出用信号を発生する位相検出用発振器4と、位相検出用信号の周波数を切り替える信号を発生する周波数切替信号発生器5と、位相検出用信号を2つに分岐して、基準信号と変調信号として出力する方向性結合器6と、方向性結合器6により分岐した変調信号が伝送される伝送路7,8と、方向性結合器6により分岐した基準信号と方向性結合器6により分岐して伝送路7,8を伝播した変調信号との位相を比較し、比較結果に応じて、原信号の通過時間を調整する制御信号を生成し移相器2に出力する位相検出器9とを備えた位相制御装置である。

(もっと読む)

タイミング同期装置、タイミング同期方法

【課題】基準タイミング信号に自装置の内部タイミング信号を正確に同期させるタイミング同期装置を提供する。

【解決手段】所定の時間間隔を示す基準タイミング信号と基準タイミング信号に対応する基準時刻を示す基準時刻情報とを取得する取得部と、クロック周波数を有する内部クロック信号を生成するクロック生成部と、内部クロック信号に基づいて、所定の時間間隔を示す内部タイミング信号と内部タイミング信号に対応する時刻を示す内部時刻情報とを生成する時刻情報生成部と、基準タイミング信号と内部タイミング信号、及び、基準時刻情報と内部時刻情報を比較することにより、基準タイミング信号に対する内部タイミング信号の進み又は遅れを検出し、且つ、基準タイミング信号に対する内部タイミング信号の位相の進み量又は遅れ量を検出する検出部と、位相の進み量又は遅れ量に応じてクロック周波数を調整する調整部と、を備えるタイミング同期装置。

(もっと読む)

原子発振器

【課題】光検出器で吸収される光のレベルを高めてS/Nを改善した原子発振器を提供す

る。

【解決手段】この原子発振器50は大きく分けると、アルカリ金属原子と該アルカリ金属

原子の同位体とを混合した気体を封入したセル2と、可干渉性(コヒーレント性)を有し

、1つの中心周波数に対して2つの異なる周波数成分を有する第1の共鳴光対と第2の共

鳴光対を含む複数の光を気体に照射する光源(LD)1と、気体を透過した光の強度に応

じた検出信号を生成する光検出部(PD)3と、検出信号の強度に基づいて、アルカリ金

属原子に電磁誘起透過現象(以下、EIT現象と呼ぶ)を生起させるように第1の共鳴光

対の周波数を制御すると共に、アルカリ金属原子の同位体にEIT現象を生起させるよう

に、第2の共鳴光対の周波数を制御する周波数制御部12と、を備えて構成されている。

(もっと読む)

121 - 140 / 1,216

[ Back to top ]