Fターム[5J106CC01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 発振回路、VCO (2,067)

Fターム[5J106CC01]の下位に属するFターム

アナログ発振回路 (130)

パルス・クロック発振回路 (169)

マイクロ波・分布定数発振回路 (4)

注入同期発振回路 (18)

原子発振器 (149)

掃引周波数発振回路 (4)

掃引電圧発振(発生)回路 (7)

基準発振回路 (165)

局部発振回路 (38)

予備発振回路 (1)

複数の発振回路・VCO (166)

Fターム[5J106CC01]に分類される特許

161 - 180 / 1,216

半導体装置及びその測定方法

【課題】従来の測定方法では、測定電流の精度を十分に確保できない問題があった。

【解決手段】本発明の半導体装置の測定方法は、外部端子TMと、出力信号の位相及び周波数に応じてチャージポンプ回路12を制御する位相周波数比較器11と、周波数制御電圧生成ノードVNDに対する電流を出力するチャージポンプ回路12と、チャージポンプ回路12が出力する電流に応じて周波数制御電圧を周波数制御電圧生成ノードVNDに生成するループフィルタ14と、周波数制御電圧に応じて出力信号の周波数を制御する電圧制御発振器15と、を有する半導体装置の測定方法であって、外部端子TMを介してチャージポンプ回路12の出力電流を含む第1、第2の測定電流のいずれか一方を測定し、外部端子TMに流れるリーク電流を含む第3の測定電流を測定し、第1、第2の測定電流とリーク電流との差分に基づき流出電流IS1又は流入電流IS2の電流値を算出する。

(もっと読む)

周波数補正回路

【課題】送信波の周波数に同期された周波数又はその逓倍波を容易かつ正確に出力できる周波数補正回路を提供する。

【解決手段】第1電圧制御発振器16の出力信号と基準発振信号との位相差に応じた位相差信号を第1位相比較器10により生成し、第1ループフィルタ12を介して第1位相差信号に応じた第1発振制御信号により第1制御発振器16の発振をフィードバック制御する第1フェーズロックループ回路106と、第2電圧制御発振器36の出力信号と比較対象信号との位相差に応じた位相差信号を第2位相比較器30により生成し、第2ループフィルタ32を介して第2位相差信号に応じた第2発振制御信号により第2制御発振器36の発振をフィードバック制御する第2フェーズロックループ回路114とを備え、第1発振制御信号に応じて第2発振制御信号を変動させることによって比較対象信号に応じて出力信号をロックする。

(もっと読む)

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

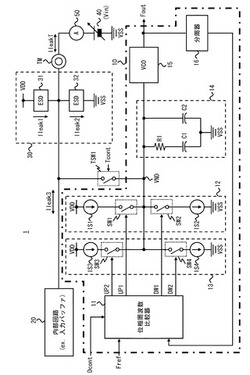

発振回路

【課題】従来の発振回路では、出力信号のジッタを抑制できない問題があった。

【解決手段】本発明の発振回路は、発振周波数設定電流に基づき蓄積された電荷量に応じて発振周波数制御電圧Vcpを生成するフィルタコンデンサCpumpと、発振周波数制御電圧Vcpに応じて出力する発振信号Foutの周波数を変動させる発振器30と、発振信号Foutの周期に基づき論理レベルが切り替えられるタイミング制御信号を生成する制御回路40と、タイミング制御信号に基づき発振信号Foutの周期の長さに応じて連続的に電圧レベルが変化する周波数検出電圧Vcapを生成する周波数検出回路10と、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて発振周波数設定電流を連続的に可変してフィルタコンデンサCpumpに出力する差動増幅器20と、を有する。

(もっと読む)

半導体装置

【課題】位相同期回路の面積を低減しつつ特性を保持するために、プロセスマイグレーションに利点のあるデジタル補償回路を適用し、位相余裕を確保する半導体装置を提供する。

【解決手段】半導体装置のデジタル補償型位相同期回路200において、発振ノードに容量を具備し、印加電圧で連続的に制御される電圧制御型発振器104を含む位相同期回路100と、入力される位相差に応じて電圧制御型発振器104の発振ノードの容量を可変に制御するデジタル補償回路201とを有する。従来方式の印加電圧によって利得が決定される電圧制御型発振器104を、デジタル補償回路201の制御信号によって利得を離散的に変化させる。デジタル補償回路201は、電圧制御型発振器104の発振ノードに、位相進みに対して負荷を印加し、位相遅れに対して負荷を減らし、最適な位相余裕が確保できるように動的に利得を制御する。

(もっと読む)

クロック信号生成装置及び電子装置

【課題】目標周波数が変更されても、生成するクロック信号の周波数を短時間で目標周波数に一致させるクロック信号生成装置、及び、電子装置を提供することを目的とする。

【解決手段】第1制御部は、設定された目標周波数が第1の目標周波数から第2の目標周波数に変更されると、第1の所定のタイミングで、第1設定数として第3の数よりも小さい第5の数を前記第1カウンタに設定するとともに、第2設定数として第4の数よりも小さい第6の数を前記第2カウンタに設定し、第1の所定のタイミングの後の第2の所定のタイミングで、第3の数を前記第1カウンタに設定するとともに、前記第4の数を前記第2カウンタに設定する。

(もっと読む)

電圧電流変換回路及びこれを備えたPLL回路

【課題】電源電圧依存性が小さい電圧電流変換回路及びこれを備えたPLL回路を提供する。

【解決手段】電圧電流変換回路は、第1電圧が供給される第1導電型のトランジスタで構成され、第1電流に基づいて第2電流を生成するカレントミラー回路と、前記第1電流が流れる第2導電型の第1のトランジスタと、一端が前記第1のトランジスタのソースに接続され、他端に第2電圧が供給され、入力された制御電圧に応じて抵抗値が変化する可変抵抗と、前記第2電流が流れ、ドレインとゲートとが前記第1のトランジスタのゲートに接続され、ソースに前記第2電圧が供給され、ゲート幅Wとゲート長Lとの比W/Lが前記第1のトランジスタの比W/Lより小さい第2導電型の第2のトランジスタと、前記第1電流または前記第2電流に基づいて出力電流を出力する電流出力部と、を備える。

(もっと読む)

PLL回路

【課題】 安定した位相雑音特性を得ることができるPLL回路を提供する。

【解決手段】 基準発振器4からの基準周波数(Fref)信号のレベルを検波回路7で検出し、制御回路5が、検出したレベルが特定値に比べて小さい場合は可変ATT6の減衰量を小さくし、検出したレベルが特定値に比べて大きい場合は可変ATT6の減衰量を大きくする制御信号を可変ATT6に出力し、可変ATT6では制御回路5からの制御信号に従って基準周波数信号の減衰を行い、PLL IC2への基準周波数信号の入力レベルを安定化させ、位相雑音特性の劣化を防止し、更にアンロックを防止できるPLL回路である。

(もっと読む)

サブサンプリングされた周波数ロックループを備える送受信機

周波数シンセサイザ

【課題】 スプリアスを低減すると共にDDS回路本来の出力周波数帯域を十分に活用して所望の基準周波数信号を出力することができる周波数シンセサイザを提供する。

【解決手段】 DDS回路22の出力に、帯域制御電圧に応じて通過周波数帯域を可変とする帯域可変型フィルタ24を備え、制御回路21が、周波数の値と帯域制御電圧の値とを対応付けた制御電圧テーブルを記憶しており、外部からDDS回路22の出力周波数が設定されると、制御電圧テーブルを参照して、設定された出力周波数に対応する制御電圧を帯域可変型フィルタ24に出力して、帯域可変型フィルタ24をDDS回路からの出力周波数に応じたフィルタ特性としてスプリアス成分を除去する周波数シンセサイザとしている。

(もっと読む)

PLL周波数シンセサイザ

【課題】デジタル制御発振器の周波数を安定して制御する。

【解決手段】PLL周波数シンセサイザ(101)は、基準クロック信号とPLL周波数シンセサイザの出力信号との位相差を検出する位相比較器(2)と、位相差に応じた整数値および小数値の和からなる制御値を出力するループフィルタ(4)と、第1のクロック信号に同期して、整数値に相当する第1のデジタル制御信号を出力する周波数制御部(6)と、第1のクロック信号よりも高い周波数の第2のクロック信号に同期して、平均値として小数値を表す第2のデジタル制御信号を出力する周波数制御部(7)であって、当該PLL周波数シンセサイザがロック状態にあるとき、第2のデジタル制御信号の取り得る値の範囲をロック時の範囲に制限する周波数制御部と、第1および第2のデジタル制御信号によるそれぞれの周波数制御の組み合わせに応じた周波数で発振するデジタル制御発振器(10)とを備えている。

(もっと読む)

PLL回路

【課題】ループフィルタの容量値を抑え、且つ動作を安定させることが可能なPLL回路を提供することを目的としている。

【解決手段】入力信号の位相と電圧制御発振回路の出力信号の位相とを比較し、位相差に応じた信号を出力する位相比較器と、前記位相比較器の出力信号に応じて充放電電流を生成するチャージポンプ回路と、前記チャージポンプ回路の出力を平滑し第一の制御電圧を生成するループフィルタと、前記ループフィルタから出力される前記第一の制御電圧を所定の電圧になるよう第二の制御電圧を生成する制御電圧生成回路と、を備え、前記第一の制御電圧と前記第二の制御電圧とが前記電圧制御発振回路に入力される。

(もっと読む)

PLL装置

【課題】外部からの基準周波数信号の振幅レベルの適正範囲内を特定し、その適正範囲の内外に応じて電圧制御発振器に制御電圧を供給するPLL装置において、温度により動作が不安定になることを防ぐこと。

【解決手段】制御電圧出力部に供給される信号を位相比較部と予備信号供給部との間で切り替える切り替え部と、前記基準周波数信号の信号路とアースとの間に設けられ、当該基準周波数信号の振幅レベルを規制するために、ダイオードを逆並列に接続した保護回路と、この保護回路の雰囲気温度を検出する温度検出部と、外部からの前記基準周波数信号の振幅レベルを検出するレベル検出部と、を備えるようにPLL装置を構成し、検出温度に応じて前記切り替えの基準となるしきい値を設定し、前記ダイオードの温度特性により前記振幅レベルが変わることに対応する。

(もっと読む)

発振器

【課題】フロア雑音または位相雑音を抑えることができ、かつ分周器の分周比の設定に手間がかからない発振器を提供すること。

【解決手段】周波数シンセサイザの出力信号を順次分周する複数の分周器と、前記複数の分周器における最終段の分周器から目的とする周波数が得られるように、当該複数の分周器の各々について、入力周波数と分周比との組み合わせを複数設定すると共に各組み合わせ毎に、各段の分周器の出力信号のフロア雑音または位相雑音の大きさを記載した分周特性データを記憶する記憶部と、前記記憶部に記憶されている分周特性データに基づいて、各分周器の許容入力周波数の範囲内でありかつ最終段の分周器からの出力信号のフロア雑音または位相雑音が良好な入力周波数と分周比との組み合わせを判断して選択する選択部と、を備えるように発振器を構成する。

(もっと読む)

周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

(もっと読む)

通信装置及び周波数シンセサイザ

【課題】使用する周波数帯域で、温度変化による送受信の振幅値の偏差を抑えることができる通信装置を提供すること。

【解決手段】送信信号の信号路に介在して設けられると共に制御電圧の印加により容量が変化する可変容量素子とインダクタンスとを含む共振回路を有し、この共振回路の共振点に応じて高周波の入力信号の振幅を調整する振幅調整回路と、前記信号路が置かれている雰囲気の温度を検出する温度検出部と、一のチャンネルにおける周波数帯域において、送信信号の振幅値が予め設定した値になるようにまたは近づくように、前記振幅調整回路の制御電圧値と温度検出値との関係データを記憶する記憶部と、前記温度検出部の温度検出値と前記関係データとに基づいて振幅調整回路の制御電圧を出力する制御電圧出力部と、を備えるように装置を構成する。

(もっと読む)

アナログ及びデジタルフィードバック制御を備えた位相ロック・ループ(PLL)

光受信装置及びクロック生成方法

【課題】分散値の調整を簡易かつ迅速に行うとともに、分散値の調整時にアンロック状態が発生することを回避すること。

【解決手段】分散補償部は、設定された分散値を用いて光信号の波長分散を補償する。位相差信号生成部は、分散補償部によって補償された光信号に含まれるクロックである外部クロックと、自装置内で用いるクロックである内部クロックとの位相差を算出することにより位相差信号を生成する。分散値調整部は、分散補償部に設定された分散値を調整する。抑制部は、分散値調整部によって分散値が調整された場合に、位相差信号生成部によって生成された位相差信号に現れる変動を抑制する。クロック生成部は、抑制部によって抑制された位相差信号に基づいて、外部クロックの位相と同期した内部クロックを生成する。

(もっと読む)

基準信号発生装置及び方法

【課題】 GPS信号の受信障害が発生しても、内蔵オシレータよりも高い周波数安定度の基準信号を発生することと、受信障害の発生前後で連続性の高い基準信号を出力することとを両立した基準信号発生装置を提供する。

【解決手段】 GPS受信機にて取得したGPS受信時刻と、そのGPS受信時刻の直前或いはその直後に標準電波受信機にて取得した標準電波受信時刻との時刻差を、予め定められた時間間隔毎に算出し、算出した時刻差と日時とを関連づけた時刻差データベースを構築する。GPS受信障害の発生を未検出のときGPS受信時刻に基づいて電圧制御発振器を制御して基準信号を発生し、GPS受信障害の発生を検出中は、時刻差データベースから取得した現在の日時に対応する時刻差に基づいて標準電波受信時刻を補正して電圧制御発振器を制御して基準信号を発生する。

(もっと読む)

原子発振器

【課題】従来よりも周波数精度を向上させることができる原子発振器を提供する。

【解決手段】磁場発生部40は、アルカリ金属原子20の第1基底準位と第2基底準位にゼーマン分裂を生じさせる磁場を発生させる。周波数制御部50は、光検出部30の検出信号32に基づいて、光源10が出射する第1の光と第2の光が、順に、複数の所定の磁気量子数の各々に対応する第1基底準位と第2基底準位の間で遷移を引き起こす共鳴光対となるように、所定の切り替えタイミングで第1の光及び第2の光の少なくとも一方の周波数を切り替える。磁場制御部60は、検出信号32に基づいて、第1の光と第2の光が、所定の磁気量子数の各々に対応する共鳴光対となるときの第1基底準位と第2基底準位のエネルギー差を特定可能なプロファイル情報を順に取得し、アルカリ金属原子20にかかる磁場の強度が一定になるように磁場発生部40が発生させる磁場の強度を制御する。

(もっと読む)

161 - 180 / 1,216

[ Back to top ]