Fターム[4K030BB12]の内容

Fターム[4K030BB12]の下位に属するFターム

2層被覆からなるもの (432)

Fターム[4K030BB12]に分類される特許

61 - 80 / 1,270

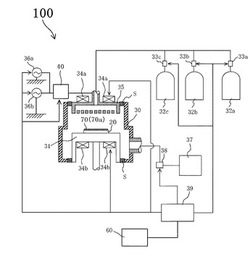

窒化膜の製造装置及びその製造方法、並びにその製造プログラム

【課題】窒化膜の屈折率及び/又は堆積速度の分布の均一性を所定の数値範囲内に収めるとともに、窒化膜の応力の制御性を高める。

【解決手段】本発明の1つの窒化膜の製造装置100は、チャンバー30内に配置された基板20上にプラズマCVD法によって窒化膜70(70a)を形成する窒化膜の製造装置100である。具体的には、この窒化膜の製造装置100は、窒化膜70(70a)の形成のために独立に印加する相対的に高い周波数の第1高周波電力及び/又は相対的に低い周波数の第2高周波電力とを用いて得られる、所定の数値範囲内に収まった前述の窒化膜の屈折率の分布及び/又は前述の窒化膜の堆積速度の分布に基づいて、所望(応力が0の場合を含む)の窒化膜70(70a)の圧縮応力又は引張応力を得るための第1高周波電力が印加される第1期間と第2高周波電力が印加される第2期間とを算出する制御部39を備えている。

(もっと読む)

成膜方法

【課題】長時間に亘り十分なバリア性を発揮する積層構造のバリア膜を単一のプラズマCVD装置にて一貫して成膜することができる量産性のよい成膜方法を提供する。

【解決手段】減圧下のプラズマCVD装置の反応室内に、シリコンを含む原料ガスと、窒素を含む第1の反応ガスとを導入し、放電用電力を投入してプラズマCVD法にて処理対象物表面に下層(窒化シリコン膜)Bdを成膜する第1工程と、第1の反応ガスから、窒素及び酸素を含む第2の反応ガスに切り換え、原料ガスと共に反応室内に導入し、中間層(酸窒化シリコン膜)Bmを成膜する第2工程と、第2の反応ガスから第1の反応ガスに切り換え、原料ガスと共に反応室内に導入し、上層(窒化シリコン膜)Buを成膜する第3工程とを含み、少なくとも第2工程と第3工程との間で、少なくとも原料ガスの導入を一時的に停止する工程を更に含む。

(もっと読む)

窒化ガリウムの気相成長方法

【課題】 大きな直径を有する複数枚の基板(4インチ基板、6インチ基板)の表面に、1000℃以上の温度で窒化ガリウムの気相成長を行なっても、基板が割れず高品質の結晶成長が可能な気相成長方法を提供する。

【解決手段】 前記のような基板を保持するためのサセプタ、該サセプタの対面、該基板を加熱するためのヒータ、該サセプタと該サセプタの対面の間隙からなる反応炉、原料ガス導入部、及び反応ガス排出部を有する気相成長装置を用いた窒化ガリウムの気相成長方法であって、基板表面の温度、基板表面と該基板の対面表面との温度差を適切な範囲内に設定し、かつ基板の位置における原料ガスの線速を適切な範囲内となるように原料ガスの供給を調整して基板表面に窒化ガリウム層の形成を行なう気相成長方法とする。

(もっと読む)

プラズマCVD装置を用いた半導体装置の製造方法

【課題】プラズマCVD装置を用いた半導体装置の製造方法に関し、製膜室のクリーニング後に、仮製膜を行った際に堆積する膜の剥離を防ぎ、半導体薄膜中に堆積膜が混入することを防ぐ方法を提供する。

【解決手段】プラズマCVD装置を用いた半導体装置の製造方法においては、仮製膜の際に結晶質シリコン薄膜を用いている。仮製膜の際に、結晶質シリコン薄膜を用いることで、堆積膜が半導体薄膜の膜中に取り込まれることを防ぐことが可能となった。

(もっと読む)

積層フィルム、電子デバイス

【課題】高いガスバリア性を有する積層フィルムを提供する。

【解決手段】基材と、前記基材の少なくとも片方の表面上に形成された少なくとも1層の薄膜層とを備える積層フィルムであって、前記薄膜層のうちの少なくとも1層がケイ素、酸素および水素を含んでおり、前記薄膜層の29Si固体NMR測定において求められる、酸素原子との結合状態が異なるケイ素原子の存在比に基づいて、Q4のピーク面積に対する、Q1,Q2,Q3のピーク面積を合計した値の比が、下記条件式(I)を満たす。(Q1,Q2,Q3のピーク面積を合計した値)/(Q4のピーク面積)<1.0…(I)(Q1:1つの中性酸素原子及び3つの水酸基と結合したケイ素原子、Q2:2つの中性酸素原子及び2つの水酸基と結合したケイ素原子、Q3:3つの中性酸素原子及び1つの水酸基と結合したケイ素原子、Q4:4つの中性酸素原子と結合したケイ素原子)

(もっと読む)

成膜装置

【課題】基板上に成膜される膜の膜厚の均一性を向上する。

【解決手段】基板200を搬送経路に沿って搬送する搬送コンベアと、搬送経路中に位置する成膜室100と、搬送経路に沿ってトンネル状に位置し、成膜室100を通過する基板200を取り囲んで加熱する加熱炉120とを備える。成膜室100は、筐体150と、この筐体150内に成膜材料を微粒子化した成膜ガスを噴霧する噴霧機構と、筐体150の1つの側壁に位置して成膜ガスを排気するための排気口とを有する。筐体150は、成膜室100を通過する基板200と対向する開放部を加熱炉120内に有する。成膜ガスは、成膜室100において、噴霧機構から開放部を通過して排気口に向けて流動する。開放部は、対向して通過する基板200の搬送方向と直交する方向において、基板200の幅に対して1.15倍以上1.4倍以下の幅を有する。

(もっと読む)

半導体装置の製造方法

【課題】金属酸化膜の表面に形成される導電膜の基板面内における厚さばらつきを低減して、半導体装置の歩留まりを向上させることが可能であり、かつ導電膜の成長速度を向上させて、半導体装置の生産性を向上させることの可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に、金属酸化膜を含む誘電体膜5を形成する工程と、誘電体膜5において、表面5aに非晶質の金属酸化膜が露出した状態で、誘電体膜5の表面5aに導電膜6を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】第1の金属元素および第2の金属元素を含む金属酸化膜を形成する際に、金属酸化膜中の第1の金属元素及び第2の金属元素の組成比の制御性を向上させる。

【解決手段】基板を収容した処理室内に、第1の金属元素を含む第1原料と酸化剤とを供給することで、基板上に第1の金属元素を含む第1の金属酸化膜を形成する工程と、処理室内に、第1原料と第2の金属元素を含む第2原料とを混合した混合原料と酸化剤とを供給することで、基板上に第1の金属元素および第2の金属元素を含む第2の金属酸化膜を形成する工程と、を交互に繰り返すことで、基板上に、第1の金属酸化膜と第2の金属酸化膜とを交互に積層して、第1の金属元素および第2の金属元素を含む第3の金属酸化膜を形成する工程を有する。

(もっと読む)

化学気相蒸着方法を使用した発光素子の製造方法

【課題】互いに異なる流動ガスを交互に注入して工程温度を変化させる化学気相蒸着方法を使用した発光素子の製造方法を提供する。

【解決手段】本発明の化学気相蒸着方法を使用した発光素子の製造方法は、第1工程温度で、サテライトディスクに載置された基板上に量子ウェル層を形成する段階と、第2工程温度で、量子ウェル層上に量子障壁層を形成する段階と、を有し、量子ウェル層と量子障壁層とを形成する段階を少なくとも一回遂行する。

(もっと読む)

半導体装置の製造方法

【課題】高周波数動作が可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、成長炉内に配置した基板10上に、GaN電子走行層16を成長する工程と、成長炉に導入する混合ガス中の窒素原料ガスの分圧比を0.15以上0.35以下として、GaN電子走行層16上に、InAlN電子供給層18を成長する工程と、InAlN電子供給層18上に、ゲート電極26と、ゲート電極26を挟むソース電極28およびドレイン電極30と、を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

III族窒化物半導体発光素子の製造方法

【課題】pコンタクト層をp型化し、かつ電極とのコンタクト抵抗を低減すること。

【解決手段】pクラッド層14上に、MOCVD法によって、MgがドープされたGaNである第1のpコンタクト層151を形成する(図2(b))。次に、次工程で形成する第2のpコンタクト層152の成長温度である700℃まで降温した後、アンモニアの供給を停止し、キャリアガスを水素から窒素へと切り換えて置換する。これにより、第1のpコンタクト層151のMgは活性化され、第1のpコンタクト層151はp型化する。次に、前工程の温度である700℃を維持し、キャリアガスには窒素を用いてMOCVD法によって、第1のpコンタクト層151上に、MgがドープされたInGaNである第2のpコンタクト層152を形成する(図2(c))。

(もっと読む)

III族窒化物エピタキシャル基板およびその製造方法

【課題】デバイス化の工程で割れが発生することを抑制することが可能なIII族窒化物エピタキシャル基板およびその製造方法を提供する。

【解決手段】本発明のIII族窒化物エピタキシャル基板10は、Si基板11と、該Si基板11と接する初期層14と、該初期層14上に形成され、Al組成比が0.5超え1以下のAlGaNからなる第1層15A1(15B1)およびAl組成比が0超え0.5以下のAlGaNからなる第2層15A2(15B2)を順次有する積層体を複数組有する超格子積層体15と、を有し、前記第2層のAl組成比が、前記基板から離れるほど漸減することを特徴とする。

(もっと読む)

軸オフの種結晶上での100ミリメートル炭化ケイ素結晶の成長

【課題】 軸オフのウェーハを得るための従来技術において、より大きな結晶は、一般に結晶の垂線から離れて配向され、ついで軸オフの種結晶を産生するためにウェーハが配向方向に向かって切断される。垂線から離れて結晶を配向することは、結晶と同じサイズのウェーハを切断するために利用可能な有効な層厚を低減する。

【解決手段】 半導体結晶および関連する成長方法が開示される。結晶は、種結晶部分と、種結晶部分上の成長部分とを含んでいる。種結晶部分および成長部分は、実質的に直立した円筒形の炭化ケイ素の単結晶を形成する。種結晶面は、成長部分と種結晶部分との間の界面を規定し、種結晶面は、直立した円筒形の結晶の基部に実質的に平行であり、単結晶の基底平面に関して軸オフである。成長部分は、種結晶部分のポリタイプを複製し、成長部分は、少なくとも約100mmの直径を有する。

(もっと読む)

成膜方法及び成膜装置

【課題】低誘電率化、ウェットエッチング耐性の向上及びリーク電流の低減化が達成されたSiBCN膜を形成することが可能な成膜方法を提供する。

【解決手段】被処理体Wが収容されて真空引き可能になされた処理容器4内に、ボロン含有ガスと窒化ガスとシラン含有ガスと炭化水素ガスとを供給して被処理体の表面にボロンと窒素とシリコンと炭素を含む薄膜を形成する成膜方法において、ボロン含有ガスと窒化ガスとを交互に間欠的に供給するサイクルを1回以上行ってBN膜を形成する第1の工程と、シラン系ガスと炭化水素ガスと窒化ガスとを間欠的に供給するサイクルを1回以上行ってSiCN膜を形成する第2の工程とを有する。これにより、低誘電率化、ウェットエッチング耐性の向上及びリーク電流の低減化が達成されたボロンと窒素とシリコンと炭素とを含む薄膜を形成する。

(もっと読む)

製造プロセス用の処理槽及びその製造法

【課題】継続的に使用しても内壁面に反応生成物が実質的に付着することはなく、生産効率を格段に伸ばすことができる反応槽を提供することを目的としている。

更に、その製造法によれば、継続的に使用しても内壁面に反応生成物が実質的に付着することのない製造プロセス用処理槽の構造体及びその構造体を用いた製造プロセス用処理槽を容易に提供できる製造プロセス用処理槽の構造体及びその構造体を用いた製造プロセス用処理槽の製造法を提供することを目的としている。

【解決手段】本発明に係る反応槽は、槽本体の内表面にPFAから成る膜を設けたものである。又、反応槽及びその構造体の製造法は、内壁面に溶融・再溶融してPFA膜を設けるものである。

(もっと読む)

基材表面処理装置

【課題】各チャンバーの処理速度が異なる場合であっても、基材の片面に接触することなく処理中基材を一時的に保持することにより品質の安定した処理済基材を得ることができる基板表面処理装置を提供する。

【解決手段】基材送出リールから送出された基材の処理面に各処理を行って処理後の基材を下流側の基材巻取リールに巻き取る基材表面処理装置であって、基材の処理面に処理を行う処理チャンバーと、処理後の基材を一時的に滞留させるバッファチャンバーと、を備えており、バッファチャンバーは、固定ローラと、この固定ローラに対して接離可能に移動する余長調整ローラとを有しており、固定ローラ及び余長調整ローラは、基材の進行方向に対して傾斜して配置されており、固定ローラのローラ面と余長調整ローラのローラ面とに基材の処理面の裏面を接触させつつ、余長調整ローラを移動させることにより基材の長さに応じて基材を滞留させるように構成する。

(もっと読む)

エピタキシャルウエハ及び半導体素子

【課題】エピタキシャル成長層の結晶品質を向上させることができ、厚膜のエピタキシャル成長層を形成する場合においてもキャリア移動度の低下が生じず、素子抵抗の低い炭化珪素エピタキシャルウエハおよび炭化珪素半導体素子を提供する。

【解決手段】炭化珪素半導体素子は、ドーピングにより格子定数が減少するドーパントを濃度Aでドーピングした基板と、ドーパントを基板よりも小さい濃度Bでドーピングしたエピタキシャル成長層と、基板とエピタキシャル層との間に、ドーパントをドーピングした2層以上積層した多層構造で形成されたバッファ層とを有し、多層構造の各層のドーパントのドーピング濃度Cが、バッファ層の厚さをd、エピタキシャル成長層からの各層までの平均距離をx、所定の割合をPとして、[B+(A−B)×x/d]×(1−P)≦C≦[B+(A−B)×x/d]×(1+P)とした。

(もっと読む)

半導体エピ薄膜の成長方法及びこれを用いた半導体発光素子の製造方法

【課題】反応ガスを供給するノズルが詰まる現象を緩和して工程効率及び生産性を向上させた半導体エピ薄膜の成長方法及びこれを用いた半導体発光素子の製造方法を提供する。

【解決手段】本発明の半導体エピ薄膜の成長方法は、ウェハーホルダーに積載された複数のウェハーを反応チャンバの内部に配置する段階と、ウェハーの積載方向に沿って延長されて備えられたガス供給部を通じて塩素系有機金属化合物を含む反応ガスをウェハーに噴射し、各ウェハーの表面に半導体エピ薄膜を成長させる段階と、を有する。

(もっと読む)

半導体素子の製造方法

【課題】400℃以上の温度で原子層蒸着法により蒸着が可能な前駆体を用いて高密度を有する非晶質の高誘電絶縁膜形成を通じてキャパシタンス等価厚及び漏洩電流特性を向上させることができる半導体素子の製造方法を提供する。

【解決手段】半導体基板100上にZr[C5H4(CH3)]2(CH3)2、Zr[C5H4(CH3)]2(OCH3)CH3及びZr[C5H4(CH2CH3)][N(CH3)(CH2CH3)]3の何れか一つの前駆体を用いて400℃〜500℃の温度で形成されたジルコニウム酸化膜(ZrO2)140を含む高誘電絶縁膜を形成することを特徴とする。

(もっと読む)

半極性(Al,In,Ga,B)NまたはIII族窒化物の結晶

【課題】故意にミスカットした基板を用いることにより、半極性(Al,In,Ga、B)NまたはIII族窒化物および該結晶の成長方向に垂直な表面からなる結晶である。

【解決手段】具体的には、結晶は、(Al,In,Ga,B)NまたはIII族窒化物および該結晶の成長方向に垂直な表面からなる結晶であって、該表面は少なくとも幅10μmであり、半極性方位を有し、 該結晶はx線回折により測定される半値全幅(FWHM)が0.55°未満であるロッキング・カーブにより特徴づけられる結晶品質を有することを特徴とする結晶を提供する。

(もっと読む)

61 - 80 / 1,270

[ Back to top ]