Fターム[4M104BB37]の内容

Fターム[4M104BB37]に分類される特許

261 - 280 / 284

銅配線層、銅配線層の形成方法、半導体装置、及び半導体装置の製造方法

【課題】広範囲にわたって全導電性領域に、断切れ及び上層配線層との間のリーク電流の発生のない、均一な膜厚の銅配線層を形成することが可能な銅配線層の形成方法を提供すること。

【解決手段】基板上に銅シード層のパターンを形成する工程、及び前記銅シード層のパターン上に銅配線層を無電解めっき法で形成する工程を具備することを特徴とする。

(もっと読む)

半導体素子

【課題】純度99.9999重量%以上の銅からなるスパッタリングターゲット、及び銅を用いたスパッタリングターゲットを用いて配線された、耐酸化性、耐エレクトロマイグレーション性、耐ストレスマイグレーション性に優れた銅配線を持つ半導体素子を提供する。

【解決手段】ガス成分を除いた純度99.9999重量%以上の銅からスパッタリングターゲットを作成して、このスパッタリングターゲットを用いて成膜された配線を、真空中又は不活性ガス雰囲気で450゜C未満の温度の熱処理を行うことにより、配線の結晶粒を粗大化して、粗大化した配線の結晶粒の大きさが2μm以上にして、粗大化した配線の結晶粒の幅と長さの比を6倍以上、厚さと長さの比を2.5倍以上にする。

(もっと読む)

無電解ニッケル−リンめっき皮膜及び無電解ニッケル−リンめっき浴

【解決手段】 被めっき物上に形成された無電解ニッケル−リンめっき皮膜の厚さ方向に配向した柱状晶により構成されている無電解ニッケル−リンめっき皮膜、及び水溶性ニッケル塩と、次亜リン酸及び/又はその塩と、アミノカルボン酸及び/又はその塩とを含み、アミノカルボン酸以外の有機カルボン酸及びその塩を含まない無電解ニッケル−リンめっき浴。

【効果】 本発明の無電解ニッケル−リンめっき皮膜は、柔軟性に優れ、内部応力が小さく、しかも加熱しても内部応力が増加しにくいものである。また、このめっき皮膜が形成されたフレキシブル基板は、皮膜が柔軟性に富み、皮膜に亀裂、剥離が発生しにくいものとなり、このめっき皮膜が形成されたシリコンウェハ基板は、皮膜の内部応力が小さく、加熱処理によるシリコンウェハ基板の反りが発生しにくいものとなる。

(もっと読む)

深トレンチのドープシリコン充填のプロセスシーケンス

膜堆積がトレンチの底部から上に向かって生じるようなシラン比に対する温度、圧力およびドーパントで第1の充填が実施される、深トレンチ構造のイン・シトゥー・ドープアモルファスシリコンによるボイドフリー充填方法が提供される。この第1の充填によって、100%を超えるステップカバレージウェルが達成される。第2の充填ステップにおいて、堆積レートに対するドーパントの影響を低減するために変更された条件で堆積が実施されることによって、トレンチ充填が、第1の充填の堆積レートを超える堆積レートで完了される。深トレンチキャパシタ構造を形成するためのこの方法の用途において、中間ステップはさらに、アモルファスシリコン層によるボイドフリー充填トレンチのキャッピング、その後のウェーハの平坦化、およびドーパントを再分布させるための熱アニーリングを含む。 (もっと読む)

表示装置用配線、該配線を有する薄膜トランジスタ表示板及びその製造方法

【課題】配線の低抵抗特性及び信頼性を同時に確保する。

【解決手段】導電性酸化物を含有する第1導電層及び銀を含有する第2導電層を有する表示装置用配線と、基板110、該基板110上に形成されているゲート線、ゲート線上に形成されているゲート絶縁膜140、ゲート絶縁膜140上に形成されているソース電極173を含むデータ線171及びソース電極173と対向しているドレイン電極175、及びドレイン電極175と接続されている画素電極190を有している。ゲート線とデータ線171及びドレイン電極175の少なくとも一方とは、導電性酸化物を含有する第1導電層及び銀を含有する第2導電層を有する。これにより、配線の密着性が向上するので剥離を防止することができ、信頼性が向上する。

(もっと読む)

半導体を利用した薄膜トランジスタ表示板及びその製造方法

【課題】安定した接触特性及び電気的特性を有する信号線を含む有機半導体薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】まず、絶縁基板上にゲート線を形成し、ゲート線を覆う有機絶縁物質のゲート絶縁膜を形成する。次に、ゲート絶縁膜上に常温で非晶質状態のITO膜を積層して感光膜パターンを利用した湿式エッチング工程でパターニングして、データ線及びドレイン電極を形成する。この時、エッチング液はクロムエッチング液を利用する。次に、感光膜パターンを除去した後でアニーリング工程を実施して、非晶質状態のITO膜を準結晶化する。次に、有機半導体を形成した後、ドレイン電極を露出する接触孔を有する保護膜を形成し、接触孔を通じてドレイン電極と連結される画素電極を形成する。

(もっと読む)

銅配線層の形成方法、半導体装置の製造方法

【課題】 細りのない所望する断面積の銅配線を形成することができる銅配線層の形成方法および半導体装置の製造方法を提供すること。

【解決手段】 基板1上に下地絶縁膜2、下地バリア層3、銅シード層4を順次成膜したのち、この銅シード層4上にフォトレジスト層5の配線溝6パターンを形成し、この配線溝6の底部に露出した銅シード層4上に銅配線層7を形成し(図2(a))、この層7上に保護層8を形成したのちこの層8をマスクとしてフォトレジスト層5、銅シード層4、下地バリア層3を順次エッチングして図2(e)に示す銅配線層7のパターンを形成する。

この層7からの銅の拡散を防止するため表面に層間絶縁層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板4上にシリコン酸化膜5を介して例えばゲ−ト電極2を形成するに際し、このゲ−ト電極2を複数の多結晶シリコン層6の積層体で構成する。ゲ−ト電極2の部分は、非晶質層の堆積工程とこの非晶質材料の結晶化(再結晶化)工程とを有する薄膜の製造方法により形成する。この際、1回に成膜する非晶質層の厚さが不良事象に応じて決定される臨界応力値によって規定される厚み以下であるように非晶質層の堆積を複数回に分割して行い、各非晶質層の堆積工程後毎に非晶質材料を結晶化させ、かつ非晶質層堆積工程と非晶質材料結晶化工程を繰り返すことにより必要な膜厚の多結晶層6の積層構造体を得る。

【解決手段】 半導体装置の電気特性の劣化と、層間剥離,層内での割れ等の不良を防止し、かつ多結晶材料層の積層により、所望厚さで小粒径の多結晶層が得られる。

(もっと読む)

半導体配線用Cu合金、Cu合金配線の製法、該製法で得られたCu合金配線を有する半導体装置、並びに半導体のCu合金配線形成用スパッタリングターゲット

【課題】 第1の目的:半導体装置に使用される配線用Cu合金であって、半導体の配線幅を狭く設計しても該配線幅に対応する凹部に確実に埋め込むことのできる半導体配線用Cu合金を提供する。第2の目的:半導体基板に設けられた凹部に上記半導体配線用Cu合金を埋め込むことによりCu合金からなる配線を形成する製法を提供する。第3の目的:上記製法で得られるCu合金配線を有する半導体装置を提供する。第4の目的:半導体のCu合金配線を形成する際に用いるスパッタリングターゲットを提供する。

【解決手段】 第1の目的を解決できる半導体配線用Cu合金とは、Sb:0.10〜10原子%、Bi:0.010〜1.0原子%、および、Dy:0.01〜3原子%よりなる群から選ばれる少なくとも1種を含み、残部がCuおよび不可避不純物からなる半導体配線用Cu合金である。

(もっと読む)

熱化学気相成長プロセスにおけるルテニウム金属層の堆積

【課題】 熱化学気相成長プロセスにおけるルテニウム金属層の堆積を提供することである。

【解決手段】 基板にRu金属層を堆積させる方法は、示される。方法は、処理チャンバに基板を提供することと、キャリヤガス、ルテニウム-カルボニルプリカーサ、および水素を含むプロセスガスを処理チャンバに導入することとを含む。方法は、熱化学気相成長プロセスによって基板にRu金属層を堆積させることを更に含む。本発明の1つの実施形態では、ルテニウム-カルボニルプリカーサは、Ru3(CO)12を含むことができる。および、Ru金属層は、主にRu(002)結晶方位を有しているRu金属層をもたらす基板温度で堆積されることができる。

(もっと読む)

エピタキシャル膜の形成方法と、これを用いた薄膜形成方法、及び半導体装置の製造方法

【課題】 エピタキシャル膜の形成方法と、これを用いた薄膜形成方法、及び半導体装置の製造方法が開示される。

【解決手段】 エピタキシャル膜の形成方法と、これを用いた薄膜形成方法、及び半導体装置の製造方法において、第1単結晶シリコン膜上に前記第1単結晶シリコン膜の表面を部分的に露出させる開口部を有する第1絶縁膜パターンを形成した後、前記開口部によって露出された第1単結晶シリコン膜上に単結晶シリコンで構成された第1シード膜を形成する。そして、前記第1シード膜が形成された結果物上部にシリコンソースガスを提供して、前記第1シード膜上にエピタキシャル膜を成長させながら、前記第1絶縁膜パターン上に非晶質シリコン膜を形成する。その後、前記非晶質シリコン膜の結晶構造を単結晶に転換させて前記エピタキシャル膜と非晶質シリコン膜から第2単結晶シリコン膜を獲得する。

(もっと読む)

半導体装置

【課題】ゲート電極の空乏化を抑制しながら、ゲート電極を形成する際の製造プロセスを簡略化することが可能な半導体装置を提供する。

【解決手段】この半導体装置は、一対のn型のソース/ドレイン領域6aと、チャネル領域5a上にゲート絶縁膜7aを介して形成されたゲート電極8aと、一対のp型のソース/ドレイン領域6bと、チャネル領域5b上にゲート絶縁膜7bを介して形成されたゲート電極8bとを備えている。そして、ゲート電極8aは、ゲート絶縁膜7a上に形成されたTaN層9aと、TaN層9a上に形成されたポリシリコン層10aとを含み、ゲート電極8bは、ゲート絶縁膜7b上に形成されたTaN層9bと、TaN層9b上に形成されたポリシリコン層10bとを含み、TaN層9aおよび9bは、同じ層からなる。

(もっと読む)

スパッタリングターゲット

【課題】

耐酸化性、耐腐食性、耐エレクトロマイグレーション性、耐ストレスマイグレーション性に優れたスパッタリングターゲットを提供する。

【解決手段】

ガス成分を除いた純度99.9999重量%以上の銅を、酸素濃度0.1容量ppm以下の雰囲気で、溶解し、さらに鋳造を行う。得られた鋳塊に機械加工と中間焼鈍を行い、その後有機洗浄とエッチングを行ってスパッタリングターゲットを得る。

(もっと読む)

発光素子及びその製造方法

【課題】 発光素子の出光面において、方位による光の強度のバラツキの少ない発光素子を提供する。

【解決手段】 本発明の発光素子は、発光部6を介して第一導電型層5と第二導電型層7を配してなる積層体と、該積層体をなす第二導電型層7上に設けた金属薄膜層9と、該金属薄膜電極層9上に設けた透明導電体12とを少なくとも備えてなる発光素子1であって、前記透明導電体12は、単層の透明導電膜10からなり、該透明導電膜10の出光面10´における結晶粒径を30nm以上300nm以下とする。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】 薄膜トランジスタ表示板の製造工程を簡素化する。また、画素電極の断線を防止できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】 本発明の一実施形態による薄膜トランジスタ表示板の製造方法は、基板上にゲート線を形成する段階と、前記ゲート線上にゲート絶縁膜を形成する段階と、前記ゲート絶縁膜上に半導体層を形成する段階と、前記半導体層上にオーミック接触部材を形成する段階と、前記オーミック接触部材上にデータ線及びドレイン電極を形成する段階と、前記データ線及び前記ドレイン電極上に保護膜を蒸着する段階と、前記保護膜上に第1感光膜を形成する段階と、前記第1感光膜をマスクとして前記ゲート絶縁膜及び前記保護膜をエッチングすることによって、前記ドレイン電極の少なくとも一部と前記基板の少なくとも一部を露出させる段階と、導電体膜を蒸着する段階と、並びに前記第1感光膜を除去し、前記ドレイン電極の露出した部分上に画素電極を形成する段階とを含む。

(もっと読む)

半導体内部配線

【課題】Si基板上に成膜配線して半導体素子を形成することにより銅の利点である耐EM性や耐SM性を十分に生かして高度耐腐食性の微細化配線を持つ半導体素子を製造することができる高純度単結晶銅とその製造方法、更に得られた単結晶銅からなるスパッタリングターゲットおよび同ターゲットを用いて成膜した配線を有する半導体素子を提供すること。

【解決手段】銀と硫黄の合計含有量が0.1ppm以下である純度99.9999wt%以上の高純度銅を出発原料として用い、これを電気炉1内に配置した原料るつぼ5内に入れて溶解し、るつぼ底部の溶解滴下孔4から下方の単結晶鋳型6に溶解銅を滴下する。この間上部、中部、下部ヒーター10、11、12により温度を調節し、石英外筒3内を真空排気装置2により排気する。炉底部には断熱トラップ8がありその外側に冷却水9が貫流する水冷フランジ7が配置されている。この装置の単結晶鋳型内に半導体素子の配線形成用ターゲット材として好適な高純度単結晶銅が得られる。

(もっと読む)

薄膜電極用ペースト並びに薄膜電極及び薄膜素子の製造方法

【課題】電極を低コストかつ短いタイムで形成し、比較的安価な薄膜素子を得る。

【解決手段】薄膜電極用ペーストは、Pd系合金,Pt系合金,Au系合金,Ag系合金又はNi系合金のいずれかからなる粒径が1〜40nmの金属微粒子と、その金属微粒子が分散した水又は有機溶剤とを備える。薄膜電極の製造方法は、基板11の平坦な上面にそのペーストを塗布して所定の厚さに成膜する工程と、熱処理によりペーストにおける溶媒を除去して金属微粒子を焼成することにより基板11上に薄膜電極12を得る工程とを含む。薄膜素子の製造方法は、その第1薄膜電極12上にゾルゲル法により誘電体材料膜13を形成する工程と、更にそのペーストを塗布して所定の厚さに成膜した後に熱処理して金属微粒子を焼成することにより誘電体材料膜13上に第2薄膜電極14を形成する工程とを含む。

(もっと読む)

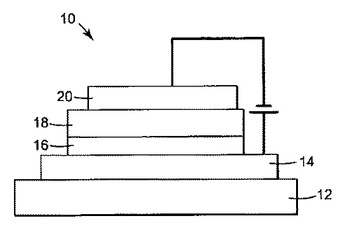

バリア層を含む発光ダイオードおよびその製造方法

発光ダイオードなどの半導体発光素子は、基板と、基板上に設けられ、発光ダイオード領域などの発光領域を含むエピタキシャル領域と、エピタキシャル領域上に設けられ、反射層を含む多層導電スタックとを含む。反射層上にはバリア層が設けられ、反射層の側壁上に延びている。多層導電スタックは、反射体とエピタキシャル領域の間にオーミック層も含むことができる。バリア層はさらに、オーミック層の側壁上に延びている。バリア層は、多層導電スタック外部のエピタキシャル領域上へも延びていてもよい。バリア層は、交互に重ねた一連の第1および第2の副層として製作できる。  (もっと読む)

(もっと読む)

真性半導体とオーミック接触部の間にPドープ半導体を備えた有機ショットキーダイオード

有機ショットキーダイオードは多結晶有機半導体層を含み、その層の一方の側面に整流接触部を有する。上記多結晶有機半導体層のもう一方の側面に非晶質のドープ半導体層が配置され、これが上記半導体層とオーミック接触層の間のバッファとして働く。  (もっと読む)

(もっと読む)

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

261 - 280 / 284

[ Back to top ]