Fターム[5F033QQ00]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095)

Fターム[5F033QQ00]の下位に属するFターム

露光 (971)

エッチング (29,543)

リフトオフ (276)

研磨 (4,337)

エネルギービームの照射 (929)

不純物導入、イオン注入 (1,611)

選択導電化、絶縁化によるパターン形成 (22)

合金化処理(熱処理を含む) (771)

熱処理 (5,181)

冷却(自然冷却は除く) (23)

酸化処理 (296)

窒化処理 (195)

清浄化 (1,803)

空気、大気に晒さない連続処理 (330)

外力を加えて形状を変化させるもの (66)

Fターム[5F033QQ00]に分類される特許

61 - 80 / 741

バリア層の形成方法

【課題】 本発明は、以上の点に鑑み、異種金属からなる導電層間に介在されるような場合でも十分なバリア性能を発揮し得るバリア層を生産性よく形成することができるバリア層の形成方法を提供する。

【解決手段】 バリア層BMは、処理対象物Wを一方の導電層CL1を有するものとし、この処理対象物と、例えばTi製のターゲット2とを真空処理室1a内に配置し、真空処理室内に希ガスを導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして一方の導電層表面に第1金属層を形成し、真空処理室内に酸素ガス及び窒素ガスを含むガスを導入してプラズマ雰囲気を形成し、第1金属層の表面を酸窒化処理すると共に、ターゲットをもプラズマ雰囲気に曝して当該ターゲット表面を酸窒化し、真空処理室内に希ガスを更に導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして酸窒化処理された表面に第2金属層を形成してなる。

(もっと読む)

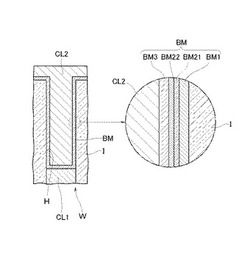

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体構造同士を直接結合する方法、およびこの方法を使用して形成された結合された半導体構造

【課題】半導体構造同士を直接結合する方法を提供すること。

【解決手段】本発明の実施形態は、半導体構造同士を直接結合する方法を含む。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ間の境界面に、キャップ層を提供することができる。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ内に、不純物が提供される。そのような方法を使用して、結合された半導体構造が形成される。

(もっと読む)

機能性膜の形成方法、積層構造体、多層配線基板、アクティブマトリクス基板及び画像表示装置、並びに図面製造装置、インクジェット装置、積層構造体製造装置

【課題】インクジェット法により微細なパターンでショートさせることなく機能性膜を形成することができる機能性膜の形成方法を提供する。

【解決手段】被印刷面上に、低表面エネルギー領域を隔てて隣接する高表面エネルギー領域231,241を有する表面において、高表面エネルギー領域231,241の形状及び機能液の着弾範囲に基づいて、高表面エネルギー領域231(241)に機能液を供給する際に該機能液が高表面エネルギー領域231(241)のみに触れるための滴下許容範囲231A(241A)を決定し、ついで滴下許容範囲231A(241A)内の任意の位置を高表面エネルギー領域231(241)に対する機能液の滴下位置231C(241C)として決定し、高表面エネルギー領域231(241)の滴下位置231C(241C)にインクジェット法を用いて選択的に機能液を供給して所定パターンの機能性膜を形成する。

(もっと読む)

金属含有犠牲材料及びダマシン配線形成の方法

【課題】ヴィアのダメージを抑制することが可能な構造及び方法を提供する。

【解決手段】実施形態に係る半導体装置を形成するための構造は、半導体基板と、ベースキャップ層210と、配線層の形成のための絶縁体層215と、絶縁体層上に形成されたハードマスク層220とを備え、ヴィアがハードマスク層及び絶縁体層の少なくとも一部を貫通して形成され、ヴィアが金属又は金属化合物を含有した犠牲材料で埋められている。

(もっと読む)

パターン化金属膜及びその形成方法

【課題】ドライエッチングが困難な遷移金属の膜を、サイドエッチングが極力生じないようにパターニングする。

【解決手段】絶縁膜の上にバリア層・密着層を形成し(S1)、その上に遷移金属からなるシード層を形成する(S2)。シード層の上にSiO2膜及びフォトレジスト膜を順次形成し(S3、S4)、フォトレジスト膜、SiO2膜をパターニングして開口を形成し(S5,S6)、開口内にCu膜及びマスクAl膜を積層する(S7、S8)。次に、SiO2膜をエッチング(S9)、露出したシード層をその膜厚方向に異方的に改質し(S10)、改質されたシード層、露出したバリア・密着層、及びマスクAl膜を順次エッチングにより除去することにより(S10〜S13)、パターン化金属膜を得る。

(もっと読む)

カーボンナノチューブ配線の製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線の製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13を形成する工程と、第1配線層上の層間絶縁膜内にコンタクト孔15を形成する工程と、コンタクト孔内の第1配線層上にカーボンナノチューブ16を成長させ、コンタクト孔から先端が突き出た複数のカーボンナノチューブを形成する工程と、層間絶縁膜上及び複数のカーボンナノチューブ間に、ストッパ膜17を形成する工程と、ストッパ膜上及び複数のカーボンナノチューブ上に絶縁膜を形成する工程と、ストッパ膜をストッパとして用い、ストッパ膜上の絶縁膜と共に、コンタクト孔上の複数のカーボンナノチューブを除去する工程と、複数のカーボンナノチューブ上に第2配線層14を形成する工程とを備える。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

パターン形成体の製造方法、および有機薄膜トランジスタ

【課題】 本発明は、簡易な製造工程で高精細なパターン状に導電性パターン等を効率よく形成可能なパターン形成体の製造方法、およびその方法により形成されたパターン形成体を用いた配線基板の製造方法や有機薄膜トランジスタの製造方法等を提供することを主目的としている。

【解決手段】 上記目的を達成するために、本発明は、光触媒を含有する光触媒含有層および基体を有する光触媒含有層側基板の光触媒含有層と、撥水性を有する樹脂製基材とを対向させて配置し、パターン状にエネルギーを照射することにより、前記樹脂製基材上に水との接触角が低下した濡れ性変化パターンをパターン状に形成するエネルギー照射工程を有することを特徴とするパターン形成体の製造方法を提供する。

(もっと読む)

配線材料、配線の製造方法、及びナノ粒子分散液

【課題】焼成無しで、酸素雰囲気に安定であり、かつ低抵抗な配線材料を提供する。また、従来の配線材料よりも低い温度で還元焼成できる配線材料を提供する。

【解決手段】銅と窒素を含む配線材料であって、当該配線材料には、添加材料として、エリンガム図において銅よりも酸化しやすい材料が0.5atm%以上10atm%以下添加されている。添加材料として、例えば、Si、Zr、Ti、Ni、Sn、Mn、Alのうち少なくとも1種類の金属を含む。この配線材料を加熱還元して低抵抗化する場合、1000Pa以下に減圧した雰囲気で加熱を行うことが好ましい。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線の製造方法は、絶縁膜13内に、配線溝30を形成し、前記配線溝内の全面に、触媒膜14を形成し、前記配線溝内の前記触媒膜上に、前記配線溝の底面に対して垂直方向に積層された複数のグラフェンシート16a〜16eで構成されるグラフェン層16を形成することを具備する。

(もっと読む)

パターン形成方法及び回路基板の製造方法

【課題】印刷法にて、容易にヴィアホール等のパターンを形成する方法を提供する事。

【解決手段】基板上に設けられた第一高分子材料からなる第一薄膜をパターニングする際に、第一高分子材料を溶解する第一溶媒に第二高分子材料を溶解させた高分子溶液を準備し、これを第一薄膜に滴下する高分子溶液滴下工程と、第一溶媒が乾燥した後に第一薄膜を第二溶媒に触れさせる第二溶媒接触工程と、を含み、第二溶媒は第一高分子材料を溶解せず、第二高分子材料を溶解する溶媒とする。

(もっと読む)

配線形成方法、及び配線

【課題】カーボンナノチューブを用いて、高精細な配線を、簡単に、かつ生産性良く形成できる半導体装置の製造方法を提供する。

【解決手段】エアロゾルジェット手段により、カーボンナノチューブ含有分散液を、基板3上にエアロゾル状態にて吹き付け、電極1に接続するカーボンナノチューブからなる配線2を形成する。配線はカーボンナノチューブがネットワーク状に絡み合った構造になっているので導電性が高い。

(もっと読む)

重合体、膜形成用組成物、絶縁膜、半導体装置および重合体の製造方法

【課題】エッチング工程によってもダメージを受けにくい絶縁膜を形成し得る重合体を含む膜形成用組成物、前記絶縁膜、該絶縁膜を備える半導体装置、さらには前記重合体の製造方法を提供すること。

【解決手段】本発明の膜形成用組成物は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する化合物Cを含む重合性化合物を重合することにより得られる、分散比が1.0以上2.5以下の重合体を含むものである。

(もっと読む)

配線形成方法

【課題】下層配線層と配線シード層との密着性を低下させないで高く維持することが可能な配線形成方法を提供する。

【解決手段】下層配線層4と絶縁性バリヤ層6と層間絶縁膜8と上層配線層が順次積層された被処理体に対して上層配線層と、連通配線層16とを形成する配線形成方法において、絶縁性バリヤ層を残した状態で連通ホール9Bを形成し、連通ホール内に犠牲膜を埋め込み、トレンチ9Aを形成するパターンマスク62を形成する前処理工程と、トレンチを形成するトレンチ形成工程と、犠牲膜60とパターンマスクとをアッシングするアッシング工程と、トレンチ内と連通ホール内に熱処理によりバリヤ層10を形成するバリヤ層形成工程と、異方性エッチングにより連通ホールの底部のバリヤ層と絶縁性バリヤ層とを除去する異方性エッチング工程と、配線シード層12を形成する配線シード層形成工程とを有する。

(もっと読む)

半導体装置の製造方法および半導体装置の製造システム

【課題】ダマシン配線構造を有する半導体装置において、CMP法によるCu配線への処理により発生するCu配線の腐食(コロージョン)の発生を防止し、配線抵抗の上昇を抑制し、信頼性の担保された半導体装置の製造方法および半導体装置の製造システムを提供する。

【解決手段】ダマシン配線構造を有する半導体装置の製造方法であって、基板上の層間絶縁膜に形成される配線パターン溝にバリアメタル膜およびCu膜が形成された状態で、ケミカルメカニカルポリッシングによって配線パターン溝以外に堆積したCuを除去する工程と、配線パターン溝以外に堆積したバリアメタルをケミカルメカニカルポリッシングによって除去する工程と、前記バリアメタルを除去する工程後、除電する工程と、基板上に残るスラリーおよび残渣物を洗浄する工程と、を有する半導体装置の製造方法が提供される。

(もっと読む)

半導体装置とその製造方法

【課題】ダマシン配線構造を有する半導体装置において、フルオロカーボン膜へのエッチングダメージによるCu配線構造でのリーク電流の増加や誘電率の低下を抑制し、信頼性の担保された半導体装置の製造方法を提供する。

【解決手段】エッチング処理の施されたフルオロカーボン膜の表面に対し、窒化プラズマ処理またはCFプラズマ処理を行う、半導体装置の製造方法が提供される。これによれば、配線溝形成時のフルオロカーボン膜へのエッチングダメージが修復され、Cu配線構造におけるリーク電流の増加や誘電率の低下を抑制することができる。

(もっと読む)

回路基板の製造方法

【課題】印刷法にて、回路基板に容易にヴィアホールを開口できる回路基板の製造方法を提供する事。

【解決手段】基板上に第一導電体を形成する第一導電体形成工程を行い、次に第一導電体を被覆する様に第一絶縁膜を成膜する第一絶縁膜成膜工程を行い、次に第一導電体上の第一絶縁膜に貫通孔32を開口して、第一導電体の表面を露出させる貫通孔形成工程を行い、次に第一導電体の表面を撥液化させる撥液化工程を行い、次に貫通孔32以外の領域に前駆体樹脂を印刷し、印刷後に前駆体樹脂を硬化して第二絶縁膜を形成する第二絶縁膜形成工程を行う。

(もっと読む)

半導体装置

【課題】低抵抗かつ微細化が可能なグラフェン配線を有する半導体装置およびその製造方法を提供する。

【解決手段】一実施の形態によれば、半導体装置は、配線と前記配線に接続されるコンタクトプラグを有する。前記配線は、長さ方向の両側面に触媒層を有する基体と、前記基体の前記両側面上に前記触媒層と接して形成され、前記基体の前記両側面と垂直に積層された複数のグラフェンを有するグラフェン層を有する。

(もっと読む)

半導体基板の製造方法

【課題】ビア配孔内に形成したカーボンナノチューブを埋め込む埋め込み膜が基板に均一に形成されないため基板の平坦化処理工程において層間絶縁膜が不均一に研磨されて、下層配線と上部電極がビア配線以外で電気的につながってしまう場合が発生する。

【解決手段】半導体基板における層間絶縁膜内のビアホール内にカーボンナノチューブを形成した後、基板全体をフッ化処理することにより、カーボンナノチューブが存在するビアホールにのみ埋め込み膜が形成され、その後に基板全体の平坦化処理のために基板を研磨する工程において、層間絶縁膜が局所的に研磨されることを防止する。

(もっと読む)

61 - 80 / 741

[ Back to top ]